Устройство для контроля интегральных микросхем оперативной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для создания аппаратуры экспресс-проверки модулей оперативной памяти. Цель изобретения - упрощение устройства. Устройство содержит генератор 1 импульсов, формирователь 2 сигналов выборки, счетчик 3 адреса, первый 4 и второй 6 элементы И, триггер 7 записи-чтения, триггер 8 цикла, триггер 9 выбора режима, триггер 10 останова, управляемый инвертор 11, блок 12 контроля, счетчик на 2 N+1 состояние. Устройство реализует тест "Бегущие 0 и 1". 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1

„„SU „„1589325 (51)5 G 11 С 29/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ айаг.!

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4382914/24-24 (22) 22.02.88 (46) 30.08.90. Бюл. № 32 (72) M. М. Букин (53) 681.327.6 (088.8) (56) Авторско свидетельство СССР № 955208, G 11 С 29/00, 1980.

Авторское свидетельство СССР № 1249588, кл. G 11 С 29/00, 1984.

2 (54) УСТРОИС 1 ВО ДЛЯ.КОНТРОЛЯ ИНТЕГРАЛЬНЬ1Х МИКРОСХЕМ ОПЕРАТИВ"

HOA ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для создания аппаратуры экспресс-проверки модулей оперативной памяти. Цель изобретения — упрощение устройства. Устройство содержит генератор 1 импульсов, формирователь 2 сигналов выборки, счетчик 3 адреса, первый 4 и второй 6 элементы И, триггер 7 записи-чтения, триггер 8 цикла, триггер 9 выбора режима, триггер 10 останова,управляемый инвертор 11, блок 12 контроля, счетчик на 2" +1 состояние. Устройство реализует тест «Бегущие 0 и 1». 3 ил.

1589325

Изобретение относится к вычислительной техн ке и может быть использовано для создачия аппаратуры экспресс-проверки модулей оперативной памяти.

1Яель изобретения — упрощение устройст5 ва.

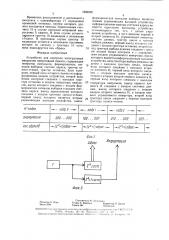

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 и 3 — схемы поясняющие принцип работы устройства.

Устройство содержит генератор 1 импульсов, формирователь 2 сигналов выборки, счетчик 3 адреса, первый элемент И 4, проверяемую микросхему 5, второй элемент

И 6, триггер 7 записи-чтения, триггер 8 цикла, триггер 9 выбора режима, триггер 10 останова, управляемый инвертор 11, блок 12 контроля и счетчик 13 данных.

Блок 12 контроля образуют управляемый икнертор 14, счетчик 15 результата, третий элемент И 16, однонибратор 17, блок 18 индикации и триггер 19 индикации.

Счетчик 13 данных включает четвер- 20 тыи 20 и пятый 2! элементы И, счетчик 22 информации и триггер 23 информации.

Принцип действия счетчика данных 13 следующий. В начальный момент триггер 23 информации находится н нулевом состоянии и элемент И 20 пропускает импульсы с выхода генератора 1 на счетчик 22. На

2-м импульсе счетчик 22 обнуляется и импульс переполнения устанавливает триггер

23 н единичное состояние. Следовательно, для следующего импульса с выхода генератора 1:-лемент И 20 закрыт, а элемент

И 21, через который проходит импульс сброса триггера 23, открыт. (2 +1) -й импульс приводит схему в начальное состояние.

Устройство работает следующим образом.

Устройство производит запись, считывание и проверку считыва=-.ì",îé информации по всем адресам проверяемой микросхемы памяти. Запись и считывание информации с

0-го по (2 +1) -й адрес производятся поочередно и называются кадром записи-чтения.

Если информацию типа «бегущая едини1I,à l>> расположить линейно, кадр за кадром. то легко заметить (фиг. 2), что интервалы между единицами одинаковы и равны (2+1) адресам. Для построения устройства на основе указанной закономерности не- 4> обходим ы двоичный счетчик на 2" состояний (n разрядов) в качестве счетчика ади реса и еще один счетчик на 2+1 состояние, являющийся источником информации.

Л -разрядный счетчик 22, триггер 23 информации и элементы И 20 и 21 в сонокуп- gg ности образуют с етчик данных.

Информация, снимаемая с выхода триггера 23, представляет собой бегущую единицу, которая записывается по адресу, задаваемому счетчиком 3 àëðåñà.

В нулевом кадре н испытуемую микро- 55 схему 5 памяти по всем адресам записывается «О», поступающий с единичного выхода триггера 23 информации. Импульсы переполнения счетчика 3 адреса и счетчика 22 устанавливают соответственно триггер 7 записи-чтения и триггер 23 информации, вследствие чего испытуемая микросхема начинает работать в режиме «Чтение«; уровнем с инверсного выхода триггера 7 записи-чтения закрывается элемент И 4, поэтому на счетчик 22 во время работы в режиме чтения не поступают импульсы с выхода генератора 1 и он не меняет своего состояния.

В режиме чтения происходит считывание информации по всем адресам. После чтения по последнему адресу импульс переполнения счетчика 3 адреса устанавливает триггер 7 записи-чтения в нулевое состояние и открывается элемент И 4. На этом заканчивается нулевой кадр.

В первом кадре в режиме записи при нулевом адресе на счетчике 3 адреса триггер 23 еще находится в единичном состоянии, что обуславливает запись «1» по нулевому адресуу.

Очередной импульс с выхода генератора 1, пройдя через элементы И 4 и 21, устанавливает триггер 23 в нулевое состояние.

В последующих кадрах устройство работает аналогично описанному, при этом «1» в каждом последующем кадре записывается со сдвигом адреса на единицу.

Окончание контроля в режиме «бегущая

1» характеризуется записью единицы н последнем кадре по последнему адресу, что фиксируется элементом И 6 с инверсией, на ныходе которого при этом появляется «0».

Зтот сигнал устанавливает в единичное состояние триггер 8. В момент окончания чтения по последнему адресу триггер 8 возвращается в нулевое состояние и устанавливает в единичное состояние триггер 9 выбора режима работы. С этого момента устройство начинает работать в режиме «бегущей О».

При воздействии уровня «1» на входах управления иннерторон 11 и 14 на информационный вход проверяемой микросхемы 5, а также на вход блока контроля поступает информация, обратная по отношению к той, которая поступила в режиме «Бегущая 1».

Контроль в режиме «Бегущий О» проходит так же, как и в режиме «Бегущая 1».

По окончании его триггер 9 возвращается в нулевое состояние, и по заднему фронту этого сигнала триггер 10 останона устанавливается в единичное состояние и останавливает генератор 1.

В случае контроля исправной микросхемы на вход счетчика 15 поступает 2+1 импульсон (в режиме работы «Бегущая 1»

2 импульсов и 2 импульсов н режиме работы «Бегущий О») . По последнему импульсу устанавливается триг:-ер 10 останона, сигнал с выхода которого àïóñêàåò однонибратор !7.

1589325 нрп тцв

Составитель М. Лапушкин

Редактор А. Огар Техред А. Кравчук Корректор О. Ципле

Заказ 2544 Тираж 484 Подписное

BHH1IIII I Государственного комитета по изобретенннм и открытиям нрн ГKIIT C.(.(.!

113035, Москва, Ж вЂ” 35, Раушскан:шб.. д. 4, 5

Произвотственно-издательский комбинат «Патен-», г. Ужгород, ул. 1 агарина, 1и!

Временное расположение и длительность импульса с одновибратора 17 определяют временной интервал, внутри которого должен находиться импульс переполнения счетчика 15 в случае контроля исправной микросхемы 5 памяти. В этом случае устанавливается триггер 19 индикации в положение

«Годен». В противном случае триггер 19 индикации остается в начальном состоянии, которое по сигналу с триггера 10 останова индицируется как «Брак».

10 Формула изобретения

Устройство для контроля интегральных микросхем оперативной памяти, содержащее генератор импульсов, формирователь сигналов выборки, счетчик адреса, триггер записи-чтения, триггер останова, блок контроля, первый вход которого является информационным входом устройства, второй вход блока контроля соединен с выходом триггера останова и входом генератора импульсов, выход которого соединен с входом формирователя сигналов выборки и входом счетчика адреса, выход переполнения которого соединен с входом триггера записи-чтения, первый выход которого является вторым 25 управляющим выходом устройства, выход

6 формирователя сигналов выборки является первым управляющим выходом устройства, информационные выходы счетчика адреса являются адресными выходами устройства, отличающееся тем, что, с целью упрощения устройства, в него введены первый и второй элементы И, управляемый инвертор, счетчик данных, триггер цикла и триггер выбора режима, первый выход которого соединен с входом триггера останова, второй выход триггера выбора режима соединен с третьим входом блока контроля и с управляющим входом управляемого инвертора, выход которого является информационным выходом устройства, вход триггера выбора режима сое— динен с выходом триггера цикла, первый вход которого соединен с выходом второго элемента И, первый вход которого соединен с вторым выходом триггера записичтения и вторым входом первого элемента И, первый вход которого соединен с выходом генератора импульсов, выход первого элемента И соединен с входом счетчика данных, в ыход которого соединен с вторым входом второго элемента И, и входом первого управляемого инвертора, второй вход триггера цикла соединен с первым выходом триггера записи-чтения.