Устройство для контроля дискретного канала

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи. Цель изобретения - повышение точности контроля. Устройство содержит анализатор 1 принимаемых сигналов, коммутатор 2, формирователь 3 сигналов перехода, реверсивный счетчик 4 и дешифратор 5 номера состояния. По оценке входного сигнала в анализаторе 1 формирователь 3 вычисляет кумулятивные суммы, влияющие на содержимое реверсивного счетчика 4, отражающее состояние дискретного канала и дешифрируемое дешифратором 5. Устройство отличается выполнением формирователя 3 и входящих в него вычислителей кумулятивных сумм. 2 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU „„15894О7 (Я)5 Н 04 В 3/4

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСИОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР! (21) 4607562/24-09 (22).21.11.88 (46) 30.08.90. Бюл. У. 32 (71) Белорусский институт инженеров железнодорожного транспорта (72) Н.Ф.Семенюта и А.Н.Семенюта (53) 62 1.395.664(088.8) (56) Авторское свидетельство СССР

Р 1142894,, кл. Н 04 В 3/46, 10.06.83 . (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДИСКРЕТНОГО КАНАЛА (57) Изобретение относится к электросвязи. -Цель изобретения — повышение

2 точности контроля. Устр-во содержит анализатор 1 принимаемых сигналов, коммутатор 2, формирователь 3 сигналов перехода, реверсивный счетчик 4 и дешифратор 5 номера состояния. По оценке входного сигнала в анализаторе 1 формирователь 3 вычисляет кумулятивные суммы, влияющие на содержимое реверсивного счетчика 4, отражающее состояние дискретного канала и дешифрируемое дешифратором 5, Устр-во отличается выполнением формирователя

3 и входящих в него вычислителей кумулятивных сумм. 2 з.п. ф-лы, 3 ил.

1589407

Изобретение относится к электросвязи и мсжет использоваться в адаптивных системах передачи дискретных сообщений (СПДС).

Цель изобретения — повышение точности контроля.

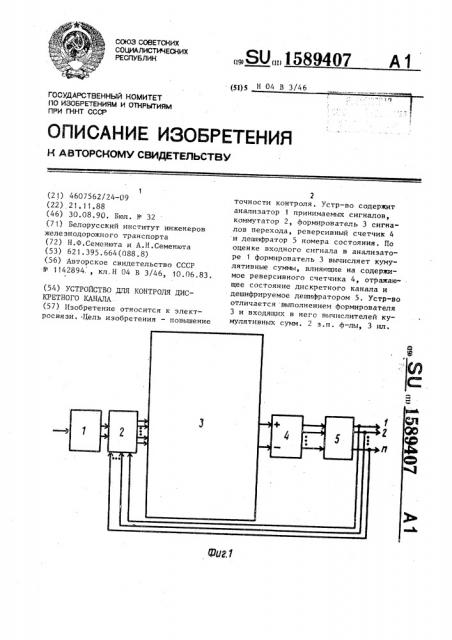

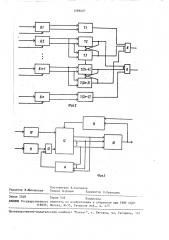

Па фиг. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 — структурная

10 электрическая схема формирователя с1нгналов перехода; на фиг. 3 — структ рная электрическая схема вычислителя кумулятивной суммы.

YCtpOHCTBO для KOHTpOJIH JIHCKpBTHO го канала (ДК) (фиг. 1) содержит нализатор 1 принимаемых сигналов, оммутатор 2, формирователь 3 сигна. ов перехода, реверсивный счетчик 4 дешифратор 5 номера состояния, при- 20 ем формирователь 3 сигналов перехоа содержи коммутаторы 6.1-6.п, выислители 7.1-7.(2n-2) кумулятивной уммы и первый 8 и второй 9 элементы а каждый из вычислителей 7.1- 25

3.(2r -2) кумулятивной суммы содержит первый 10 и второй 11 формирователи импульсов, элементы 12 запрета, реЬерсивный счетчик 13, дешифратор 14 нулевого состояния, блок 15 установки нулевого состояния и дешифратор 16 порогового состояния.

Устройство работает следующим образом.

На вход анализатора 1 принимаемых сигналов поступают кодовые блоки. На35 значение анализатора 1 принимаемых сигналов состоит в том, чтобы определи-.ь, искажен или не искажен очередной гринятый кодовый блок. В случае искажения кодового блока на сигнальном выходе анализатора 1 вырабатывается высокий, as случае неискажения — низкий уровень. В обоих случаях этч сигналы сопровождаются тактовым импульсом на тактовом вьп:оде анализатора 1. Сигналы поступают на вход коммутатора 2 и в зависимости от текущего состояния ДК, которое в данный момент определяется дешифратором 5 номера состояния, проходят на какой-либо вход формирователя 3 сигналов перехода.

С входов формирователя 3 через соответствующие коммутаторы 6 сигналы поступают на соответствующие вычислители 7 кумулятивных сумм, в которых происходит вычисление кумулятивных сумм и сравнение их с заданными порогами. При превышении какой-либо кумулятивной суммой заданного порога на выходе соответствующего вычислителя 7 образуется импульс, который через первый 8 или второй 9 элемент

ИЛИ поступает на суммирующий или вычитающий вход реверсивного счетчика 4.

Реверсивный счетчик 4 изменяет свое состояние. Дешифратор 5 номера состояния вырабатывает сигнал на одном из своих выходов в зависимости от состояния реверсивного счетчика

Этот сигнал является выходным для устройства контроля состояния ДК и используется в адаптивных СПДС для изменения режима функционирования.

Вычислитель 7 кумулятивной суммы (фиг. 3) работает следующим образом.

B зависимости от того, искажен или не искажен очередной кодовый блок, тактовый импульс с коммутатора 6 поступает на первый 10 или второй 11 формирователь импульсов соответственно. При поступлении тактового импульса на вход формирователя 10 последний выдает заранее заданное число импульсов, которые поступают на суммирующий вход реверсивного счетчика 13. Это число импульсов пропорционально логарифму отношения вероятностей приема искаженного блока в двух соседних состояниях ДК. При поступлении тактового импульса на вход формирователя 11 последний также выдает заранее заданное число импульсов, которые через элемент 12 запрета прохо,дят на вычитающии вход реверсивного счетчика 13. Это число импульсов пропорционально логарифму отношения вероятностей приема неискаженного блока в двух соседних состояниях ДК. Таким образом, реверсивный счетчик 13 в зависимости от поступающих импульсов изменяет свое состояние и накапливает кумулятивную сумму. При переходе реверсисного счетчика 13 через заданное граничное состояние (при превышении кумулятивной суммой заданного порога) срабатывает дешифратор

16 порогового состояния и выдает на выходе импульс. Этот импульс поступает на вход первого 8 или второго 9 элемента ИЛИ и на первый вход блока

15 установки нулевого состояния.

Реверсивный счетчик 13 приходит в исходное нулевое состояние. К выходу реверсивного счетчика 13 подключен также дешифратор 14 нулевого состоя5 15894 ния, назначение которого состоит в недопущении поступления на вычитающий вход реверсивного счетчика 13 импульсов от формирователя 11 при нахождении реверсивного счетчика 13 в нулевом состоянии (реализация отражающего экрана). формула изобретения

1. Устройство для контроля дискретного канала, содержащее анализатор принимаемых сигналов и последовательно соединенные реверсивный счетчик и дешифратор номера состояния, отличающееся тем, что, с целью повышения точности контроля, введены последовательно соединенные коммутатор и формирователь сигналов 20 перехода, при этом сигнальный и тактовый выходы анализатора .принимаемых сигналов подключены соответственно к сигнальному и тактовому входам коммутатора, управляющие входы которого 25 соединены с соответствующими выходами дешифратора номера состояния, а первый и второй выходы формирователя сигналов перехода подключены соответственно к входу сложения и к входу вычитания реверсивного счетчика.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что формирователь сигналов перехода содержит п коммутаторов по числу контролируемых состояний дискретного канала, ?и-2

35 вычислителей кумулятивной суммы и первый и второй элементы ИЛИ, выходы которых являются соответственно первым и вторым выходами формировате- 40 ля сигналов перехода, входами которого являются первые и вторые входы

07 6 коммутаторов, первый и второй выходы каждого из которых подключены соответственно к первым и вторым входам соответствующих вычислителей кумулятивной суммы, причем выходы вычислителей кумулятивной суммы с нечетными номерами подключены к соответствующим . входам первого элемента ИЛИ, выходы вычислителей кумулятивной суммы с четными номерами подключены к соответствующим входам второго элемента ИЛИ, а входы сброса вычислителей кумулятивной суммы с второго по (2п-3)-й соединены с выходами соответствующих вычислителей кумулятивной суммы.

3. Устройство по пп. 1 и 2, о т— л и ч а ю щ е е с я тем, что вычис литель кумулятивной суммы содержитпоследовательно соединенные первый формирователь импульсов, реверсивный счетчик, дешифратор порогового "îñòîÿíèÿ и блок установки нулевого состояния, выход которого подключен к входу сброса реверсивного счетчика, второй формирователь импульсов и последовательно соединенные дешифратор нулевого состояния, входы которого соединены с соответствующими выходами реверсивного счетчика, и элемент запрета, второй вход и выход которого соединены соответственно с выходом второго формирователя импульсов и с входом вычитания реверсивного счетчика, причем первым и вторым входами, выхо-, дом и входом сброса вычислителя кумулятивной суммы являются соответственно входы первого и второго формирователей импульсов, выход дешифратора порогового состояния и второй вход блока установки нулевого состоя- . ния.

1589407

Составитель В.Слепаков

Техред И.Дидык 1(орректор О, 1(равцова

Редактор В.Иаковская

Заказ 2548 Тираж 538 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ C(Cp

113035, Москва, >К-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул, Гагарина, 101