Цифровой демодулятор сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи и может использоваться для демодуляции сигналов с частотной и относительной фазовой манипуляцией (ФМ). Цель изобретения - повышение помехоустойчивости от импульсных помех. Демодулятор содержит усилитель-ограничитель 1, регистр 2 сдвига, фазовые детекторы 3 и 4, вычитатель 5, фильтр 6 нижних частот, компаратор 7 и блок фильтрации (БФ) 8, состоящий из выделителей 9 и 12 переднего и заднего фронтов импульса, блоков 10 и 13 обработки импульса и RS-триггера 11. Входной сигнал с ФМ поступает на усилитель-ограничитель 1, формирующий прямоугольный импульсный сигнал, который поступает в БФ 8. Здесь происходит восстановление сигнала, в фазу которого заложена информация о сигнале ФМ. Далее сигнал задерживается в регистре 2 и полученные сигналы перемножаются в детекторах 3 и 4. Сигналы перемножения поступают на вычитатель 5, формирующий трехуровневый импульсный сигнал, постоянная составляющая которого меняется по закону сигнала манипуляции. Эта составляющая выделяется фильтром 6 и поступает на компаратор 7, формирующий выходной двухуровневый сигнал. Цель достигается введением компаратора 7 и БФ 8. 2 з.п. ф-лы, 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТ ИЧЕСНИХ

РЕСПУБЛИН (19) (11) А1 (g1)g Н 04 1. 27/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМЪГ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ К ОТНРЦТИЯМ

ПРИ ГКНТ СССР (21) 4631549/24-09 (22) 04.01.89 (46) 30.08.90. Бюл. 1,"- 32 (72) E.Ï.Ãóäíåâ, И.Н.Решетняк и С.В.Долгушев (53) 621.394.4 (088;8) (56) Авторское свидетельство СССР

Р 543132, кл. Н 03 D 3/06, 1975. (54) ЦИФРОВОЙ ДГИОДУЛЯТОР СИГНАЛОВ (57) Изобретение относится к технике связи и может использоваться для демодуляции сигналов с частотной и относительной фазовой манипуляцией (ФИ). Цель изобретения — повышение помехоустойчивости от импульсных помех. Демодулятор содержит. усилитель-ограничитель t, регистр 2 сдвига, фазовые детекторы 3 и 4, вычитатель

5, фильтр 6 нижних частот, компаратор 7 и блок йильтрации (БФ) 8, состояций из выделителей 9 и 12 переднеI го и заднего пронтов импульса, блоков 10 н 13 обработки импульса и

RS-триггера 11. В:-:одной сигнал с И! поступает на усилитель-ограничитель

1, Аормируюций прямоугольный импульсный сигнал, который поступает в БФ 8.

Здесь происходит восстановление сигнала, в Лазу которого заложена информация о сигнале Ф)1. Далее сигнал задерживается в регистре 2 и полученные сигналы перемножаются в детекторах 3 и 4. Сигналы перемножения поступают на вычитатель 5, Аарми" руюций трехуровневый импульсный сигнал, постоянная составляюшая которого меняется по закону сигнала.ма. нипуляции. Эта составляюшая выделяется фильтром 6 и поступает на кампаратор 7, Ьормируюший выходной двухуровневый сигнал. Цель достигается введением компаратора 7 и БФ 8.

2 з.п. h-лы, 4 ил.

3 1589420 4

Изобретение относится к технике связи и может использовaòüñÿ для дейодуляции сигналов с частотной и относительной Аазовой манипуляцией.

Цель изобретения — повьш ение помехоустойчивости от импульсных помех.

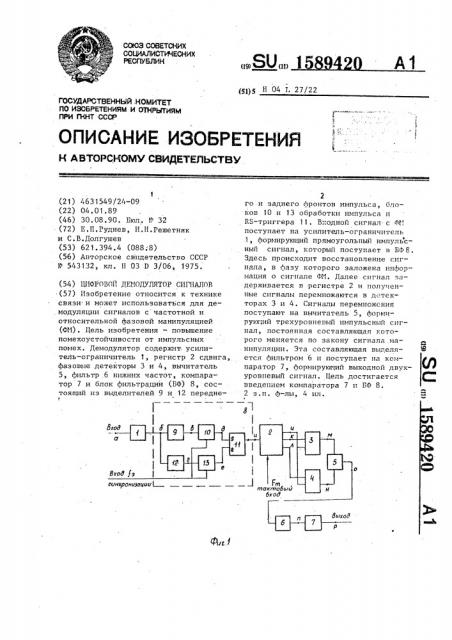

На фиг.1 изображена структурная электрическая схема цифровсго демодулятора сигналов; на фиг.2 — схема 10 блока обработки импульса; на Лиг.3, 4 — временные диаграммы, поясняющие работу демодулятора.

Цифровой демодулятор содержит усилитель-ограничитель 1, регистр 2

15 сдвига, первый 3 и второй 4 фазовые детекторы, вычитатель 5, Аильтр 6 нижних частот, компаратор 7, блок 8 фильтрации, содержащий -вьщелитель 9 переднего Аронта импульса, первый блок 10 обработки импульса, RS-.òðèã гер 11, вьщелитель 12 заднего фронта импульса, второй блок 13 обработки ! импульса. Блоки 10, 13 содержат пер вый, второй счетчики 14, 15, дешифра — 25 тор 16, блок 17 задержки, делитель

18 частоты, РЯ-триггер .19, первый, третий, второй элементы И 20, 21, 22, элемент ИЛИ 23.

Цифровой демодулятор работает

30 следующим образом.

Входной сигнал (диаграмма "а" фиг.3), например с Аазовой манипуляцией поступает на вход усилителяограничителя 1, на выходе которого формируется прямоугольный импульсный сигнал, синфазный входному, то есть передние и задние фронты этой импульсной последовательности совпадают с моментами положительных переходов вход- 40 ного сигнала через нулевой уровень (диаграмма "б" Аиг.3). С выхода усилителя-ограничителя 1 прямоугольная импульсная последовательность поступает на входы выделителей 9, 12 переднего и заднего фронтов импульса, на выходах которых Аормируются последовательности коротких по длительности

1 импульсов („((— —, где f „- часах

50 тора входного сигнала), моменты их появления совпадают с моментами появления передних и задних фронтов импульсного сигнала с выхода усилителя-ограничителя 1 (диаграмма "в" Аиг.3) . Последовательности коротких импульсов с выходов вьщелителей 9 и 12 поступают на входы блоков 10, 13, где осуществляется фильтрация импульсных сигналов. С выходов блоков 10, 13 отфильтрованные импульсные сигналы (соответствующие передним и задним Аронтам импульсного сигнала с выхода усилителя-ограничителя 1) поступают на входы Р$-триггера 11 (диаграммы "д,е" фиг.3). С его помощью происходит восстановление прямоугольного импульсного сигнала (диаграмма "и" фиг.3), в фазу которого заложена инАормация о сигнале манипуляции, который необходимо получить в результате демодуляции. С выхода PS-триггера 11 прямоугольная последовательность импульсов поступает на информационный вход регистра 2, который задерживает прямоугольный импульсный сигнал на время =- m/Ã, где m — число разрядов регистра сдвига между разрядом, соотВетствующим третьему выходу регистра

2, и разрядом регистра 2, который является средним ло отношению к разря- дам соответствующим первому и второму выходам регистра 2; à — такто- вая частота. В случае обработки Аазоманипулированного сигнала величина должна быть равна длительности элементарного символа. Сигналы с первого и второго выходов регистра 2 и сигнал с третьего выхода этого же регистра перемножаются на Ааэовых детекторах

3, 4, причем сигнал с первого выхода о регистра 2 сдвинут на плюс 45 относительно ш разряда регистра 2 (диаграмма к" Аиг.3), а сигнал с второю

ro выхода регистра 2 — на минус 45 относительно ш разряда регистра 2 (диаграмма "л" Апг.3).

На выходах Аазовых детекторов 3,4 имеют место перемноженные сигналы (диаграммы "м,п" Аиг.3). Эти сигналы поступают на входы вычитателя 5, на выходе которого формируется трехуровневый импульсный сигнал (диаграмма о" Аиг.3), постоянная составляющая которого меняется по закону сигнала манипуляции. Далее эта постоянная составляющая выделяется с помощью фильтра б (диаграмма "и" фиг.3) и поступает на вход компаратора 7, который Аормирует выходной двухуровневый сигнал (диаграмма р Аиг.3).

Работа блока 8 поясняется временными диаграммами, приведенными на фиг.4. На вход блока 8 (входы выделителей 9 и 12} приходит импульсная последовательность прямоугольных импульсов (диаграмма "а" Аиг.4).

5. 15

На выходах выделителей 9 и 12 выделяются последовательности коротких по длительности импульсов (диаграммы

11 11 б,в фиг.4), совпадающие с фронтами импульсного сигнала, приведенного на диаграмме "а" фиг.4. Далее импульсные сигналы, соответствующие передним Ароптам входного сигнала, поступают на вход блока 10. Очередной i-й импульс (диаграмма "б" фиг.4) сбрасывает счетчик 14 в нулевое состояние. КоэААициент счета счетчика

14 выбран так, что период повторения любого из его Аазовых состояний равен периоду повторения импульсов в последовательности, поступающей на вход сброса, то есть выполняется равенство К Т „=Т „, где Т > период входного сигнала, Т О„вЂ” период высокой опорной частоты. При достижении счетчиком 14 состояния, близкого к K-му, когда следующий «.+1-й импульс (диаграмма "б" Аиг.4) еще не появился на входе сброса счетчика

14, на выходе деыифратора 16 выделяется короткий импульс (диаграмма

"д" фиг.4), который, непосредственно и через блок 17 (диаграмма "е" фиг.4) воздействуя на P u S — входы

RS-триггера 19, Аормирует на его выходе импульс строба (диаграмма "г"

hz1I .4). Длительность строба, определяемая временем задержки блока 17, выбрана такой, что импульс строба симметричен относительно К-го состояпия счетчика 14. Далее (i+1) é импульс (диаграмма "б" Аиг.4), поступая

»а вход элемента И 20, сравнивается во времени с импульсов строба (диаграмма "г" h!Zl«..4). При их совпадении (i+1)-й импульс проходит а выход элемента И 20 (диаграмма "3 AliI .4), при этом происходит заполнение счетчи ка 15 (диаграмма "и" Аиг.4) и (i+2) и импульс в случае его совпадения с импульсом строба проходит через элемент И 22 (диаграмма "к" Аиг.4), поступая на выход блока 10 через элемент

ИЛИ 23 (диаграмма "м" Аиг.4) и на вход установки в "0" (сброса в пуль) делителя 18, на тактовьп« вход которого подана высокая опорная частота

Так как коэААициент деления К «, делителя 18 выбран из условия, что "

Т 1=К ч/f щ,=-т»1 где T >< — период, импульсной последовательности с выхода делителя 18, в случае отсутствия импульсов на его входе сброса в нуль

89420 6

1/Т я (опорная частота). Таким образом, при наличии на входе блока

10 импульсного сигнала с равньп«и смежными периодами, например Т;;, Аиг.4), совпадающими с точностью, определяемой длительностью импульса строба, импульсы, соответствующие этим периодам,,проходят через элементы И 20, 21, 23 и оказываются на выходе блока 10 (диаграмма "м" Аиг.4).

При искажении фазовой структуры входного сигнала цифрового демодуля15 тора из-за воздействия значительного уровня п«умовь«х выбросов либо из-за наличия импульсных помех в канале связи периоды следования импульсов

««лют

/ изменяться (диаграмма "б" Аиг.4).

Это приводит к несовпадению импульсов на входе элемента И 20 (с выхода выделителя 9) и импульса строба (с выхода PS-триггера 19). При этом про.хожден««е импульсного сигнала через элемент И 20 блокируется, следовательно, на выход блока 10 оп не проходит (g«lQI раммь« "K bi" hzll . 4) . Импульсньп« сигнал проходит через элемент И 21 (диаграмма "ж" фиг.4) и, воздействуя на вход установки в нуль счетчика 15,. устанавливаегся нулевой уровень сигнала на выходе счетчика 15 (диаграм»а "и" фиг.4), блокируя работу элемента И 22. Иипульс««ьп« сигнал с вь«хо-.

35 да элемента И 22 в этом случае отсутствует и, следовательно, воздействие на делитель 18 по входу установки в нуль прекращается (диаграмма "к" h«I«..4). Бследствие этого на выходе делителя 18 появляется импульсный сигнал (диаграмма "л" фиг.4) с частотой, равно«1 частоте входного сигнала, и Аазой, определяе45 мой импульсом с выхода элемента И 22, который последний раз (перед началом интервала, »а котором имеют место искажен««я фазовой структуры сигнала) воздействовал на вход установки «: нуль делителя 18. В данном случае это (i-3)-й импульс (диаграмма к" фпг.4). Таким образом, на выходе блока 10 присутствует. импульсная последовательность, образованная суммйрованп м (по««ощью 9JIPMPHT И 3) импульсов с выхода выделителя 9,. которые совпадают с импульсом строба (,диаграмма) "к" di«ir.4), и импульсов с выхода делителя 18 (диаграмма "л"

1589420 фиг.4), моменты появления которых совпадают с.фазой сигнала на неискаженных интервалах входного сигнала (диаграмма "б" фиг.4 — пунктиp).

Выходная последовательность блока

10 приведена на диаграмме "м" фиг.4.

Как видно, если на входе блока 10 имеют место значительные смещения импульсов (относительно их номинального положения), то на выходе этого блока они в значительной степени

1 уменьшены, что видно из сравнения временных диаграмма "б" и "м" фиг.4, и, следовательно мОжнО ГQBopHTb О наличии эффекта фильтрации рассмотренным блоком 10 сигнала, поступающего на его вход.

Блок 13 обработки импульсной последовательности выполнен аналогично блоку 10 обработки. Для сравнения на диаграммах фиг.4 приведены идеальный,входной сигнал блока 8 (диаграмма "п" фиг.4), сигнал с интервалом, на котором имеет место нарушение фазовой структуры сигнала за счет помехи (диаграмма "а" фиг.4), и сигнал, восстановленный на выходе

RS-триггера 11 (диаграмма "о" фиг.4), то есть отфильтрованный с помощью

ll блока 8. Из сравнения диаграмм о, и,п" фиг.4 можно прийти к выводу, что включение в состав цифрового демодулятора сигналов блока 8 значительно уменьшает фазовые (временные) иска35 жения сигнала на информационном входе регистра 2.

На фиг.3 приведены диаграммы работы цифрового демодулятора сигналов в режиме приема фазоманипулированных сигналов. Сплошными линиями на диграммах показаны сигналы при отсутствии каких-либо искажений во входном сигнале. Ela интервале (j+1)-й посылки пунктиром показано возмож- 45 ное влияние фазового искажения, вызванного, например, импульсной помеxoEI (диаграмма "а" фиг.3). Далее на диаграммах "б-р" фиг.3 пунктиром показаны возможные изменения сигналов в одноименных точках схемы фиг.1, которые имели бы место при отсутствии блока 8 в составе цифрового демодулятора сигналов.

Как видно, наличие искажений на интервале (j+1)-й посылки без блока

8 приводит к временным искажениям сигналов на выходах фазовых детекто ров 3, 4 (диаграммы "м, и" фиг.3 с учетом пунктйра) как на интервале (j+1)-й посылки, так и iIa интервале (j+2)-й посылки из-за того, что сигнал задержан регистром на длительность элементарной посылки (диаграммы "м,н" фиг.3). Временные искажения появляются в сигнале на выходе вычитателя 5 (пунктирная линия диаграммы

"о" фиг.3). Это приводит к случайным выбросам на выходе фильтра 6 (диаграмма "и" фиг.3) и появлениям искажений двухуровневого сигнала на выходе компаратора 7 (диаграмма "р" фиг.3).

При появлении импульсного сигнала на выходе элемента И 22, то есть импульсов, находящихся в пределах импульса строба, но смещенных относительно номинального положения в сторону увеличения периода, например, за счет воздействия шумов (i-5)-й и i+3-й импульсы, диаграмма

"к" фиг.4), на выходе блока 10 либо

13 (диаграммы "м, н" фиг.4) могут появиться два импульса (вместо одного) — один за счет срабатывания делителя 18, другой — за счет прохождения с выхода выделителя на выход через элементы И 20, 22 и ИЛИ 23, так как он совпадает с импульсом строба (диаграммы "м,н" фиг.4).

На восстановление прямоугольного импульсного сигнала с помощью RSтриггера 11 наличие таких двойных импульсов не оказывает влияния, так как RS-триггер 11 срабатывает только по первому импульсу из этой пары, и временное расстояние между этими импульсами не превышает половины длительности строба (диаграмма

"о" фиг.4). Длительность импульса строба, определяемая временем задержки блока 17, и модуль счетчика

15 выбираются из соображений о степени эффективности фильтрации импульсного сигнала с выходов выделителей 10,. 13 и должны обеспечить основную часть потока импульсов, соответствующих передним либо задним фронтам входного сигнала, которые имеют небольшие временные (фазовые) отклонения от номинального положения из-за воздействия помех. Выделители 9, 12 переднего и заднего фронтов могут быть выполнены в виде генератора одиночного импульса, срабатывающего по фронту управляющего сигнала.

1589420

Формула изобретения

1. Цифровой демодулятор сигналов, содержащий усилитель-ограничитель, вход которого является входом цифрового демодулятора, регистр сдвига, первый и второй выходы которого соединены соответственно с первыми входами первого и второго фазовых детекторов, выходы которых соединены с входами вычитателя, подключенного к входу фильтра нижних частот, тактовый вход регистра сдвига является тактовым входом цифрового демодулятора, отличающийся тем, что, с целью повьппения помехоустойчивости от импульсных помех, введены блок фильтрации и компаратор, причем выход усилителя-ограничителя соединен с первым входом блока фильтрации, выход которого соединен с входом регистра сдвига, третий выход которого соединен с вторыми входами фазовых детекторов, выход фильтра нижних часТоТ соединен с входом компаратора, выход которого является выходом цифрового демодулятора, второй вход блока фильтрации является входом синхронизации цифрового демодулятора.

2. Демодулятор по п.1, о т л и— ч а ю шийся тем, что блок фильтрации содержит последовательно соединенные выделитель переднего фронта импульса и первый блок обработки импульса, выход которого соединен с

S-входом РЛ-триггера, последовательно соединенные выделитель заднего фронта импульса и второй блок обработки импульса, выход которого соединен с R-входом PS-триггера, выход

5 которого является выходом блока фильтрации, первым входом которого являются входы выделителей переднего и заднего фронтов импульса, а вторым входом — вторые входы блоков обработки импульса.

3. Демодулятор по пп. 1 и 2, о т— л и ч а ю шийся тем, что блоки обработки импульса содержат каждый последовательно соединенные первый счетчик, дешифратор, блок задержки

RS-триггер, первый элемент И, второй счетчик, второй элемент И, делитель частоты и элемент ИЛИ, выход K0Topol о. является выходом блока обработки импульса, а также третий элемент И, причем первый вход первого счетчика, второй вход первого элемента И и первый вход третьего элемента.И являются пер25 вым входом блока обработки импульса, вторым входом которого являются вторые входы первого счетчика н делителя частоты, выход дешифратора соединен с другим входом РЛ-триггера, второй выход которого соединен с вторым входом третьего элемента И, выход которого соединен с другим входом второго счетчика, выход первого элемента И соединен с вторым входом вто35 ро -о .. е !е. . 11, вы од о оро о сое дипел с вторым входом элемента ИЛИ.

1589420

J (лссылка

Г ! 1 !

Г Г

Ji2 лосьика

Фиг. 4

Подписное

Тираж 528 ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, И-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101

Редактор А.11аковская

Заказ 2549

1589420 интероси на которон сиенами поранен панели

Составитель Н.Лазарева

Техред Л.Сердюкова Корректор И.Муска