Импульсный регулятор

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсным средствам автоматического управления и может быть использовано в качестве регулятора в системах автоматического управления компрессорными станциями. Целью изобретения является повышение точности и быстродействия регулирования. Импульсный регулятор содержит датчик 1, измеритель рассогласования 2, первый элемент ИЗ, первый усилитель мощности 4, исполнительный механизм 5, второй элемент И 6, второй усилитель мощности 7, первый интегратор 8, компаратор 9, задатчик 10, первый ключ 11, сумматор 12, второй интегратор 13, релейный элемент 14, выпрямитель 15, триггер Шмитта 16, дифференциатор 17, первый элемент НЕ 18, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, второй элемент НЕ 20, второй ключ 21, инвертор 22, третий элемент НЕ 23 и источник постоянного напряжения 24. Сущность изобретения заключается во введении плавно изменяющихся по частоте и длительности регулирующих импульсов в функции от величины сигнала ошибки регулирования. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„Я1„! „„1594485 (g1)g G 05 В 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

r10 ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР.

1 (21) 4450350/24-24 (22) 27.06,88 (46) 23.09,90, Вюл, Ф 35 (7)) Донецкий политехнический институт (72) В, Н. Дек аненк о, M. К. Пух но, В.А,Вальчук, А.A.Цыганок., А.С.Иващенко и В.Я,Биленко (53) 62,50 (088,8) . (56) Авторское свидетельство СССР

В 1117585, кл. G 05 Б !!/26, !984.

Авторское свидетельство СССР

У 1170426, кл.-G 05 13 !!/26, 1984. (54) ИИПУЛЬСНЫЙ РЕГУЛЯТОР (57) Изобретение относится к импульсным средствам автоматического управления и может быть использовано в качестве регулятора в системах автоматического управления компрессорными станциями, Целью изобретения является повышение точности и быстродейст2 вия регулирования ° Импульсный регулятор содержит датчик 1>,измеритель рассогласования 2, первый элемент

И 3, первый усилитель мощности 4, исполнительный механизм 5, второй элемент И 6, второй усилитель мощности

7, первый интегратор 8, компаратор

9, задатчик 10, первый ключ l! сумматор 12, второй интегратор 1,3, релейный элемент 14, выпрямитель 15 ..г триггер Шмитта 16, дифференциатор 7, первый элемент НЕ 18, элемент ИСКЛЮЧАВШЕЕ ИЛИ 19, второй элемент НЕ 20, второй ключ 21, инвертор 22, третий элемент НЕ 23 н источник постоянного напряжения 24, Сущность изобретения заключается во введении плавно изменяющихся по частоте и длительности регулирующих импульсов в функции от величины сигнала ошибки регулирования, 2 ил, 1594485

Изобретение относится к импульсным средствам автоматического управления и может быть использовано н качестве регулятора н системах авто5 матического управления компрессорными станциями.

Целью изобретения является повышение точности и быстродейстния регулирования, l0

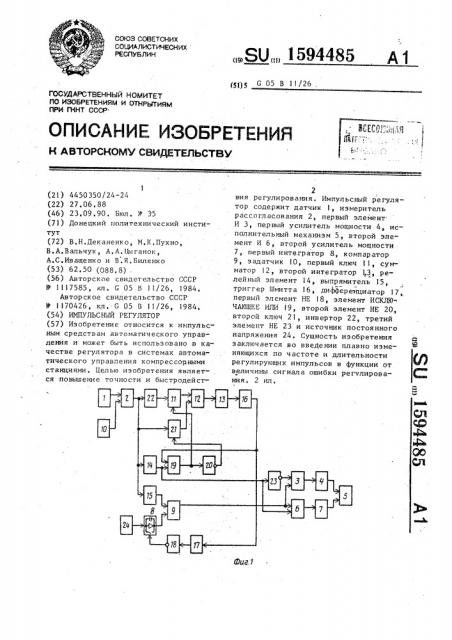

На фиг. I представлена блок-схема импульсного регулятора> на фиг. 2 временные диаграммы сигналов на выходе блоков импульсного регулятора.

Импульсный Регулятор (фиг. 1) со- 15 держит датчик 1, измеритель. 2 рассогласования, . первый элемент И 3, первый усилитель 4 мощности, исполнительный механизм 5, второй элеме.нт И

6, второй усилитель 7 мощности, пер- 20 вый интегратор 8. компаватор 9, задатчик 10, первый ключ 11 „сумматор

1 2, второй . инте гратор 13, релейный элемент 14, выпрямитель 15, триггер

Шмитт а l 6, диффер е нци втор l 7, пер вый 25 элемент НЕ 18, элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 19, второй элемент НЕ 20, второй ключ 21, иннертор 22, третий элемент

HE 23, источник 24 постоянного напряжения. 30

Импульсный регулятор работает сле-дуюп тм образом.

Сигнал с датчика 1 поступает на нход измерителя 2 рассогласования, где сравнивается с сигналом задания

35 (фиг. 2, кривая 30), Сигнал рассогласования, например, попожительной полярности (фиг. 2, кривая 25) через замкнутый второй ключ 21 поступает на второй вход сумматора 12 (кривая .43). Замкнутое состояние второго ключа 21 и первого ключа 11 соответствует нулевому уровню сигнала на управляющем входе, соответственно кривые

42 и 41 (фиг, 2), C выхода сумматора

12 сигнал (фиг, 2, кривая 32, интервал времени t -t,) поступает на вход второго интегратора 13 Выходное напряжение второго интегратора 13 при этом линейно уменьшается-(фиг. 2, кривая 33) до тех пор, пока не станет равным отрицательному уровню (фиг. 2, крив ая 37), срабатывания три ггер а

Шмитт а 16 (фиг. 2, момент времени t,), В этот момент времени триггер Шмитта

16 переключается в состояние логической "1" (фиг. 2, кривая 36, момент времени t),,При этом сигнал логичес1 кой "1" (кривая 36, интернал времени

) подается па первый вход эле—

z мента ИСКЛ1ОЧА ОЩЕЕ ИЛИ 1Ч, на второй вход которого, подается также сигнал .пс гиче ской "1" с выхода релейного элемента 14 (фиг. 2, кривая .34), так как на его выходе присутствует положительный сигнал рассогласования (фиг. 2, кривая 25) с выхода измерителя 2 рассогласования.

На выходе элемента ИСКЛЮЧА1ОЩЕЕ ИЛИ

19 появляется сигнал логического "Оп (фиг, 2, кривая 4 1, интерн ал нр еме ни и — t<), а на выходе второго элемента

HE 20 — сигнал логической "1" (фиг. 2, момент времени t> t, кривая 42), Эти сигналы, поступая на управляющие входы ключей 11 и 21, переключают первый

11 и второй 21 ключи (кривые 31 и 43 соответственно), при. этом первый ключ

11 замыкается, а второй ключ 21 раз-. ьыкается. На первый вход сумматора 12 с выхода инвертора 22 через замкнутый первый ключ 11 (интервап времени

1-й ) подается инверсный сигнал рассогласования (фиг, 2, кривая 31), С выхода сумматора (фиг. 2, крив ая 32, интервал времени t t z) сигнал подается на вход второго интегратора 13, выходной сигнал которого начинает линейно возрастать (фиг, 2, кривая 33, момент времени t ) . Напряжение на выходе второго интегратора 13 растет до тех пор, пока не становится равным положительному уровню (фиг, 2, крив ая 38) срабатывания триггера Шмитта

16. В этот момент времени (фиг, 2, момент времени t ) выходной сигнал триггера Шмитта 16 (фиг. 2, кривая

36) становится равен ло гическому "0", При этом на первый вход элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 19 подается сигнал логического "0" (фиг, 2, кривая 36, момент вРемени t>-t ), на второй вход — сигнал логической "1" (фиг. 2, кри в ая 34 ), т ак к ак си гн ал р а с со гласования по-прежнему остается положительной полярности ° На выходе элемента ИСКЛЮЧАЮЩЕЕ Hei 19 появится сигнал логической "!" (фиг, 2, кривая 41, интервал времени t;t з), а на выходе второго элемента НЕ 20 сигнал логического "0" (фиг.. 2, кривая 42, интервал времени t q-t ). После этого происходит переключение перBoI о 1 1 H BTopo1 о 2 1 ключей (фиг; 2, кривые 31 и 43 соответственно) ° В интервале t z-t > первый ключ 1 1 разомкнут, а второй ключ 21 з амкнут, 5 159

Далее процесс повторяется аналогичным образом (фи г. 2, интервал времени t>-t< ) ° С уменьшением сигнала рассогласования (ф и, 2, кривая 25) уменьшается уровень сигнала на выходе сумматора 12 (фиг. 2, кривая 32), что приводит к более медленному возрастанию (убыванию) напряжения на выходе второго интегратора 13 (фиг. 2, кривая 33), а следовательно, и к уменьшению частоты импульсов на выходе триггера ц!митта 16 (фиг. 2, кривая 36), С выхода триггера Шмитта 16 им- пульсы поступают на дифференциатор

1.7, с выхода которого продифференцированный си гнал (фи г, 2, кривая 39) через первый элемент HE 18 (фиг, 2, кривая 40) поступает на вход обнуления первого интегратора 8. На информационный вход и нте гр а тор а 8 подается также сигнал (фиг. 2, кривая 46) с источника. 24 постоянного напряжения, величина которого определяет скорость нарастания напряжения (фиг,2; кривая 28) на выходе интегратора 8, В моменты времени когда си гнал на выходе первого элемента HE 18 (фиг, 2, кривая

40) равен логическому "0", происходит обнуление первого интегратора 8, после чего сигнал на его выходе начинает линейно возрастать (фиг, 2, кривая 28), В эти периоды времени сигнал (фи г. 2, кривая 40) р авен логической "1", Сигнал с выхода первого интегратора 8 поступает на первый вход компаратора 9, на второй вход которого подается сигнал положительной полярности с выхода выпрямителя

15 (фи г, 2, кри вая 35) . Этот си гнал является выпрямленным сигналом рассогласования, На выходе компаратора

9 появляются импульсы (фиг. 2, кривая 29), длительность и частота которых зависит от величины сигнала рассогласования, Импульсы с выхода компаратора 9. поступают на первый 3 и второй 6 элементы И, на другие входы которых подается сигнал с выхода релейного элемента 14 (фиг. 2, кривая 34), причем на первый элемент И 3 он подается, через третий элемент НЕ 23 (фиг. 2, кривая 45), Сигнал на выходе элемента

НЕ 23 равен в этот период логическому "0". Репейный элемент 14 служит для выбора канала регулирования

4485 (" Меньше" или Больше" ). При гюложительном сигнале рассогласования (фи r. 2, кривая 25) работает канал

"Больше" — второй элемент И 6, вто5 рой усилитель 7 мощности и исполнительный механизм 5.

При отрицательном сигнале рассои гласования работает канал Меньше" третий элемент HE 23, первый элемент

И 3, первый усилитель 4 мощности и исполнительный механизм 5. Кроме того, в этом случае изменяется полярность сигнала на выходе релейного элемента

14 и очередность переключения первого

11 и второго 2! ключей при неизменных сигналах на выходах других блоков.

Таким образом> повышается точ2О но сть и быстродей стви е ре гул ятора з а счет плавно изменяющихся по частоте и длительности регулирующих импульсов в зависимости от величины сигнала рассогласования.

Фор мул а из обретения

Импульсный регулятор, содержащий датчик, выход которого соединен с первым входом измерителя рассогласования, второй вход которого соединен с задатчиком, первый и второй элементы И, каждый из которых через соответствующий усилитель мощности соединен с соответствующим входом исполнительного механизма, первый ключ, два

35 интегратора, сумматор и источник постоянного напряжения, о т л и ч а юшийся тем, что, с целью повышения точности и быстродействия регули40 рования, в него дополнительно введены инвертор, триггер Шмктта, второй ключ, релейный элемент. элемент ИСКЛЮЧАЗ!ЦЕЕ

ИЛИ, три элемента НЕ, выпрямитель, компаратор и дифференциатор, выход

45 измерителя рассогл асов ания соединен с входами выпря жтеля, релейного элемента, второго ключа и инвертора, выход которого соединен с входом первого ключа, выход которого соединен с первым входом сумматора, выход которого. через последовательно соединенные второй интегратор и триггер Шмитта соединен с первым входом элемента

ИСКЛЮЧА101ЦЕЕ ИГ!И и входом дифференциатора, выход которого через первый элемент НЕ соединен с входом обнуле-. ния первого инте гратора, выход второго ключа соединен с вторым входом сумматора, выход релейного элемента

1594485

Составитель b,Êèðñàíîâ

Те хр ед М, Дидык

Корректор Л.Бескид

Редактор М.Бланар

Тираж 669

Подпи сное

Заказ 2827

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 соединен с первым входом второго эле-, мента И, входом третьего элемента НЕ и вторым входом элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, выход которого соединен с управ5 ляюшим входом первого ключа и через второи элемент ИЕ с упр авля ющим входом второго клюЧа, выход третьего элемента НЕ соединен с первым входом первого элемента И, выход выпрямителя соединен с первым входом компаратора, выход которого соединен с вторыми входами первого и второго элементов И, источник постоянно о напряжения. соединен с информационным входом первого триггера, выход которого соединен с вторым входом компаратора.