Устройство для деления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в универсальных и специализированных ЭВМ для выполнения операции деления чисел. Целью изобретения является сокращение аппаратурных затрат. Устройство содержит вычислительные узлы 1 1-1 M, группу узлов 3 1-3 M формирования переноса в старший разряд вычислительного узла, группу узлов 4 1-4 M формирования цифры частного и группу узлов 2 1-2 M формирования функций генерации и транзита переноса. 7 ил.

1594527

Изобретение относится к выч и слител ьной технике и может быть применено в быстродействующих арифметических устройствах для выполнения операции деления чисел.

Цель изобретения сокращение аппаратурных затрат.

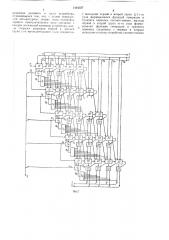

На фиг. 1 приведена обобщенная структурная схема устройства; на фиг. 2 структурная схема устройства, вариант реализации (8 разрядов делимого делится на 4 разряда делителя и образуется 5 разрядов частного); на фиг. 3 — функциональная схема вычислительной я ейки вычислительного узла; на фиг. 4 — функциональная схема знаковой ячейки вычислительного узла; на фиг. 5 — — функциональная схема ячейки узла формирования функций генерации и транзита переноса; ка фиг. 6 — функциональная схема узла формирования переноса в старший разряд вычислителя; на фиг. 7 — функциональная схема узла формирования цифры частного.

Устройство для деления (фиг. 1) содержит вычислительные узль1 11 lm, узлы 2; — -2,. формирования функций генерации и ."ранзита переноса, узлы 3I--3 формирования переноса в старший разряд вычислительногого узла, узлы 4I — 4m формирования цифры частного, вход 5 делителя устройства, вход 6 логического нуля, вход 7 делимого устройства, выход 8 частного устрОистВа, первый и второй выходы 9---10 остатка устройства, вход . 1 логической единицы устройства, выходы 12,— — 2„, сумм старших разрядов и выходы 13; — 13m переносов в старший разряд вычислительных

УЗЛОВ (I — -lm, ВЫХОДЫ 14 — 14m СУММ И ВЫходы 15 — 15„, переносов вычислительных узлов (I 1, выходы !6I — 16„, первой и

17 — 17m второй группы узлов 2 - — 2m формирования функций генерации H транзита переноса, выходы 18I---(8,„узлов 3; — 3 формирования переноса в старший разряд вычислительных узлов, выходы 19:, — 19,„формирования цифры частного.

Б схеме реализации варианта устройства (фиг. 2) вычислительные узлы I I - Im построены в виде совокупности вычислительных ячеек 20 и знаковых ячеек 21, а узлы формирования 2I---2„, функций генерации и транзита переноса -- в виде совокупности ячеек 22.

Вычислительная ячейка 20 (фиг. 3) содержит элементы 23 неравнозначности, элементы И 24, инвертор 25, элемент ИЛ((26, вход 27 (он же является выходом 34 ячейки) разряда делителя, входы 28 и 29 разрядов функций генерации и транзита переноса соответственно, управляющий вход

30 (на этот вход подается значение соответствующей цифры частного), который является и выходом 3! ячейки, выход 32 суммы, выход 33 переноса ячейки 20 и выход

34 ячейки.

Знаковая ячейка 21 (фиг. 4) содержит инвертор 35, элемент И 36, элемент 37 неравнозначности, вход 38 разряда функции генерации и вход 39 функции транзита переноса, управляющий вход 19 (на этот вход подается значение соответствующей цифры частного }, который является и ВыхОдОм 40 ячейки.

Ячейка 22 (фиг. 5) содержит элемент

И 41 и элемент ИЛИ 42, вход 43 сум1О мы и вход 44 переноса, выход 45 функции генерации пере1юса и выход 46 функции транзита перекоса.

Узел 3 формирования переноса в старший разряд (фиг. 6) содержит элемент

15 ИЛИ 47 и элементы И 48 — 50, входы

51- — -57 разрядов функций генерации и транзита lie,1екосое .

Узел 4 формирования цифры частного (фиг. 7) содержит элемент 58 неравкозкачности и элемент 59 равнозначности.

Рассмотрим функциочальное назначение и реализацию основных узлов и блоков устройства для деления.

Каждый из узлов l I — -1„, предназначен для вычисления в соответствии с алгоритмом деления без восстановления остатков соответствующего остатка в виде двух чисел; первого числа, составленного из поразрядных смм м, и В I opoI О числа, составленного из поразрядных переносов (сумма этих двух чисел равна этому остат3Q ку) . Входной информацией для каждо о из узлов (I — 1„, является три числа. Первое число — делитель, второе и третье представляют собой совокупность разрядов функций соотвстстве ко ге;Ic oàöèè и транзита переноса соо гветствующего остатка (для не(1 Bol е ы 1исл изелького зла Второе число является í". åvI, а третье число делиMûvi) с присоединеккl=lìè младшиvè разрядами, поступающими с входов 6 и 7.

Фактически в каждом из узлов 1. — (m из значения остатка, представленного совокуп40 ностью разрядов функции гекерации и транзита переноса, Вычитается или прибавляется значение делителя и образуется двухрядный код нового остатка. Особенностью первого вычислительного узла 1I является

45 то, что на его входы второй и третьеи групп может подаваться значение остатка с первого 9 и второго 10 выходов устройства в виде совокупности разрядов функций генерации и транзита переноса при многократном использовании устройства в про5р цесса ьыполнения операции деления. Одной из Возможных реализаций вычислительных узлов lI- — 1„, является их построение в виде совокупности вычислительных

20 и знаковой 21 ячеек (фиг. 2---4), между которыми отсутствуют переносы.

55 Узлы 2,— 2,, фор пирования для каждого разряда определяют значения функций генерации и транзита переноса по значениям разрядной суммы и поступивше1594527

ro в данный разряд переноса. Они могут быть реализованы в виде совокупности ячеек 22 (фиг. 2 и 5).

Узел 3; по значениям функций генерации и транзита переноса, вырабатываемых узлом 2;,.вычисляет значение переноса в старший разряд узла 1;. Функция, реализуемая узлом 3;, определяется выражением.

P=Gi+T;Gq+Ti Тг. бз+-,.+Ti ° Тг...

Т G, где б„и ҄— функции соответственно генерации и транзита переноса к-го разряда i-ro остатка (к=1,2, З,...Р; р — количество разрядов делителя). Для одной из возможных реализаций устройства (фиг. 2) узлы 31 — 3 переноса в старший разряд вычислителя могут быть построены так, как это показано на фиг. 6.

Узел 4; по значениям старшей разрядной суммы с выхода 12 узла 1;1и переноса в этот старший разряд с выхода 13 узла 1;, а также по значению переноса в старший разряд этого узла,: выработанного узлом 3;, определяет сответствующую цифру частного (фиг. 7).

Работа на примере реализации устройства, изображенного на фиг. 2.

На вход 5 делителя устройства подается значение четрех разрядов делителя с, сг, сз, с,ь на вход 6 устройства поступают нули, а на вход 7 устройства значения восьми разрядов делимого а0, аь аг, аз, а4, аь, а, а, а8. В тех случаях, когда информация, образуемая на выходах

9 и 10 в виде совокупности разрядов функций генерации и транзита переноса, снова подается на входы устройства для дальнейшей обработки (через соответствующие промежуточные регистры) на этом же устройстве, на вход 6 нуля устройства подаются разряды функций генерации переноса, а на вход 7 делимого — разряды функций транзита переноса. Первый узел l i производит вычитание из значений старших четырех разрядов делимого значения четырех разрядов делителя (знак делимого и разряд с входа 6 устройства, поступающие на знаковую ячейку 21, имеют нулевые значения). Настройка этого узла на вычитание (т. е. прибавление к значению старших разрядов делимого дополнительного кода делителя) осуществляется логической единицей, поступающей с входа 11 устройства, которая инвертирует все разряды делителя и подается на вход

44 переноса самой младшей ячейки 22 первого узла 21. Первый узел 21 формирует функции генерации G и транзита Т переноса по значениям сумм и переносов четырех вычислительных ячеек 20 первого узла lь На выходе 18 первого узла 3i вырабатывается перенос P в старший разряд узла l i согласно выражению:

P=G1+Т1 бг+Т1 Тг Gg+Ti . Тг. Тз

G<.

Узел 4i формирует первую цифру частного, которая равна единице, если значение- делителя меньше или равно значению старших четырех разрядов делимого, и равна нулю, если делитель больше, чем значение старших четырех разряддв делимого. Далее действия, производимые i-м узлом 2; формирования функций генерации и транзита переноса (i= l, 2, 3, 4) и (i+1) -м узлом 1;,„, соответствуют действиям, производимым во время очередного (i+ l ) -го цикла обычного деления без

15 восстановления остатка: если q;=1(0), то делитель вычитается (прибавляется) из i-ro остатка, образуемого в виде разрядов сумм и переносов на выходах i ãî узла 1;. Узел 2;, вырабатывает значения функций генерации и транзита переноса, которые участвуют в определении последней младшей цифры частного, а также подаются на выходы 9 и 0 остатка устройства.

Формула изоЬретенич

Устройство для деления, содержащее

m вычислительных узлов, где m — количество получаемых цифр частного, m узлов формирования функций генерации и транзита переноса, m узлов формирования

30 переноса в старший разряд вычислительного узла, m узлов формирования цифр и частного, причем вход делителя устройства соединен с входами первой группы i-го вычислительного узла (где i= 1, 2, m), выходы суммы старшего разряда и

35 переноса в старший разряд i-го вычислительного узла соединены соответственно с первым и вторым входами i-го узла формирования цифры частного, выходы переносов и суммы i-го вычислительного узла

40 соединены соответственно с входами первой и второй групп i-го узла формирования функций генерации и транзита переноса, выходы первой и второй групп которого соединены соответственно с входа ми первой и второй групп i-го узла формиро45 вания переноса в старший разряд вычислительного узла, выход которого соединен с третьим входом i-ro узла формирования цифры частного, вход настройки j-го вычислительного узла (j=2, 3,..., m) соединен с выходом (l1) -го узла формирования цифры

50 частного и с соответствующим разрядом выхода частного устройства, выход m-го узла формирования цифры частного соединен с выходом m-го разряда частного устройства, входы разрядов делимого и нуля устройства соединены с входами второй и TpcTb55 еи групп первого вычислительного узла, входы младших разрядов второй и третье 1 группы j-ro вычислительного узла соединены соответственно с входами соответствующих

1594527

7 разрядов делимого и нуля устройства, отличающееся тем, что, с целью сокраьцения аппаратурных затрат, вход настройки первого вычислительного узла соединен с входом логической единицы устройства, вхо.,ы старших разрядов второй и третьей групп )-го вычислительного узла соединены

8 с выходами первой и второй групп (j-1)-ro узла формирования функций генерации и транзита переноса соответственно, выходы первой и второй групп rri-го узла формирования функции генерации и транзита переноса соединены с первым и вторым выходами остатка устройства соответственно.

1594527

Сосга витель Н. Маркелова

Редактор E. Папи Техред А. Кравчук Корректор С. Черни

3а к а з 2830 Тираж 564 Подписное

Б!!ИИГ!И Гос!дарсги нного комитета по изобретениям и открытиям при "KH Г СССР ! !3035, Москва, )}1- 35, aiшская наб., д. 4)5 !

1р<шзводсrвеппо-издательский комбинат «!1атснт», г. Уж ород, ул. Гагарина, 01