Микропрограммное устройство управления с контролем и восстановлением

Иллюстрации

Показать всеРеферат

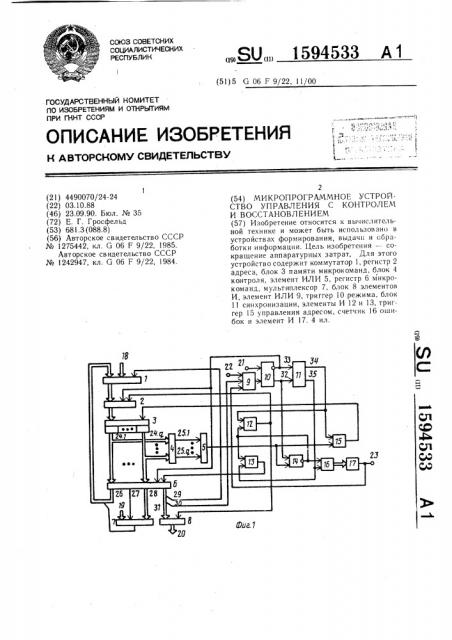

Изобретение относится к вычислительной технике и может быть использовано в устройствах формирования, выдачи и обработки информации. Цель изобретения - сокращение аппаратурных затрат. Для этого устройство содержит коммутатор 1, регистр 2 адреса, блок 3 памяти микрокоманд, блок 4 контроля, элемент ИЛИ 5, регистр 6 микрокоманд, мультиплексор 7, блок 8 элементов И, элемент ИЛИ 9, триггер 10 режима, блок 11 синхронизации, элементы И 12 и 13, триггер 15 управления адресом, счетчик 16 ошибок и элемент И 17. 4 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 5 G 06 F 9/22, 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPblTHRM

ПРИ ГКНТ СССР (21) 4490070/24-24

1 (22) 03.10.88 (46) 23.09.90. Бюл. № 35 (72) Е. Г. Гросфельд (53) 681.3 (088.8) (56) Авторское св идет ел ьств î СССР № 1275442, кл. G 06 F 9/22, 1985.

Авторское свидетельство СССР № 1242947, кл. G 06 F 9/22, 1984.

„„SU„„1594533 А 1

2 (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ С КОНТРОЛЕМ

И ВОССТАНОВЛЕНИЕМ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах формирования, выдачи и обработки информации. Цель изобретения — - сокращение аппаратурных затрат. Для этого устройство содержит коммутатор 1, регистр 2 адреса, блок 3 памяти микрокоманд, блок 4 контроля, элемент ИЛИ 5, регистр 6 м икрокоманд, мультиплексор 7, блок 8 элементов

И, элемент ИЛИ 9, триггер 10 режима, блок

11 синхронизации, элементы И 12 и 13, триггер 15 управления адресом, счетчик 16 ошибок и элемент И 17. 4 ил.

1594533

Изобретение относится к вычислительной технике и может быть использовано в устройствах формирования, выдачи и обработки информации.

Цель изобретения — сокращение аппаратурных затрат.

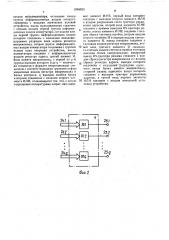

На фиг. 1 представлена функциональная схем а предлагаемого устройства; на фиг. 2 — функциональная схема возможной реализации блока контроля; на фиг. 3 функциональная схема возможной реализации блока синхронизации; на фиг. 4 — временные диаграммы сигналов на выходах блока синхронизации в рабочем режиме.

Микропрограммное устройство управления с контролем и восстановлением содержит коммутатор 1, регистр 2 адреса, блок

3 памяти микрокоманд, блок 4 контроля, второй элемент ИЛИ 5, регистр 6 микрокоманд, мультиплексор 7, блок 8 элементов

И, первый элемент ИЛИ 9., RS-триггер 10 режима, блок 11 синхронизации, второй .2 и третий 13 элементы И, элемент И-НЕ 14, триггер 15 управления адресом, счетчик 16 ошибок, первый элемент И 17, вход 18 кода операции, вход 19 логических условий, гзуппу 20 выходов микроопераций, входы запуска 21 и начальной установки 22, выход 23 неисправности, с первой по q-ю группы выходов 24.1 — 24.q блока 3 памяти микрокоманд, выходы 25.1 — 25.q ошибки соответственно первого — q-го сегментов в блоке 4 контроля, выходы поля немодифицируемых разрядов адреса 26, модифицируемого разряда адреса 27, поля проверяемого логического условия 28, признака конца команды 29, признака конца работы 30 и поля микроопераций 31 регистра б микрокоманд, входы запуска 32 и останова 33, первый 34 и второй 35 выходы блока 11 синхронизации.

Блок 4 контроля (фиг. 2) содержит первый q-й сумматоры 36.1 — Зб.q по модулю два.

Блок 11 синхронизации (фиг. 3) содержит управляемый генератор 37 импульсов, счетный триггер 38 и элементы И 39 и 40.

Микропрограммное устройство управления с контролем и восстановлением работает следующим образом.

После включения устройство должно быть установлено в исходное состояние подачей импульса на вход 22. В исходном состоянии триггер 10 установлен в «0», все разряды регистров 2 и 6, а также счетчика 16 принудительно удерживаются в состоянии

«О» под действием уровней «1», имеющихся на их входах сброса. Блок 11 импульсы на выходах 34 и 35 не формирует. Триггер 15 находится в произвольном состоянии, например в состоянии «0». В этом режиме коммутатор 1 пропускает на свои выходы и информационные входы регистра 2 код операции с входа 18, поскольку на его управляющем входе действует уровень «О», поступающий с выхода 29 регистра б.

55 и во всех последующих (кроме конечной) микрокомандах запущенной микропрограммы на выходе 29 регистра 6 установлен уровень «1», который обеспечивает выборку коммутатором 1 адресов следующих микрокоманд с выхода мультиплексора 7 и выхода 26 регистра 6.

В соответствии с кодом проверяемого логического условия, появившимся на выходе

28 регистра б, и значением этого логического условия на входе 19 мультиплексор 7 формирует на своем выходе младший разряд адреса следующей микрокоманды, который совместно с остальными разрядами адреса, поступающими с выхода 26 регистра 6, проЗапуск устройства производится подачей импульса на вход 21, что вызывает переключение в «1» триггера 10. При этом снимается блокировка с входов сброса регистров 2 и 6, на выходе элемента И-НЕ 14 и входе сброса счетчика 16 сохраняется уровень «1», обусловленный действием уровня

«О» на выходе элемента ИЛИ 5, и происходит запуск блока 11, который начинает формировать поочередно на своих выходах 34 и 35

"О тактовые импульсы, синхронизирующие работу устройства.

Первый импульс, формируемый блоком 11 на выходе 34, поступает на счетный вход триггера 15 и проходит на выход элемента И

12. При этом триггер 15 сохраняет свое состояние, поскольку его работа запрещена уровнем «О», поступающим на него с выхода элемента ИЛИ 5. Импульс, выделенный на выходе элемента И 12, открывает блок 8, через который на группу 20 выходов посту20 пает при этом нулевой код с выходов 31 регистра 6, а также своим задним фронтом загружает в регистр 2 стартовый адрес микропрограммы, заданный на входе 18.

Это обеспечивает выборку из блока 3 микро25 команды, хранящейся в банке, номер которого задан состоянием триггера 15 (для рассматриваемого случая номер банка нулевой) . Считанная микрокоманда поступает на информационные входы регистра б и подвергается контролю блоком 4, который осу30 ществляет проверку ее сегментов на наличие ошибок по принятой в устройстве дисциплине контроля (реализация блока 4, приведенная на фиг. 2, соответствует случаю, когда в устройстве организован контроль сегментов на четность). Если в микрокоманде

35 ошибок не обнаружено, то на выходе элемента ИЛИ 5 сохраняется уровень «О», который

/ продолжает удерживать триггер 15 в режиме запрета счета, а счетчик 16 — в режиме принудитеЛьной установки исходного состояния по его входу сброса. Далее блок 11 формирует первый импульс на выходе 35.

Этот импульс, не изменяя состояния счетчика 16, проходит на выход элемента И 13 и своим задним фронтом загружает в регистр 6 микрокоманду, считанную из блока 3. В этой

1594533

Формула изобретеиия

5 ходит через коммутатор 1 на информационные входы регистра 2. Если проверка логического условия в данной микрокоманде не задана, то младший разряд адреса микрокоманды с выхода 27 регистра 6 передается через мультиплексор 7 без изменений.

Под действием второго импульса, формируемого блоком 11 на выходе 34, содержимое поля микроопераций регистра 6 выдается на группу 20 выходов, а в регистр 2 загружается адрес следующей микрокоманды. Если в этой микрокоманде блоком 4 ошибок не обнаружено, то второй импульс с выхода 35 блока 11 загружает данную микрокоманду в регистр 6.

Дальнейшее функционирование устройства при отсутствии ошибок в сегментах считываемых микрокоманд осуществляется аналогично до тех пор, пока не произойдет его останов по единичному признаку конца работы с выхода 30 регистра б. При этом происходит сброс в «О» триггера 1О, который запрещает работу блока 11 и обнуляет регистры 2 и 6 и счетчик 16, переводя устройство в исходное состояние.

Если в процессе функционирования устройства в одном либо в нескольких сегментах микрокоманды, считанной из блока 3, блок 4 обнаруживает ошибку, то на его соответствующем выходе (либо выходах) формируется уровень «1», который проходит на выход элемента ИЛИ 5. При этом разрешается работа триггера 15 и счетчика 16, а работа элементов И 12 и 13 запрешается.

Очередной импульс, формируемый блоком 11 на выходе 35, инкрементирует содержимое счетчика 16, а следующий за ним импульс с выхода 34 своим задним фронтом изменяет состояние триггера 15 с «О» на «1», что обеспечивает переключение номера рабочего банка блока 3 по входу его старшего разряда адреса. По коду, хранящемуся в регистре 2, на выходы 24.1 — 24.q блока 3 выдается из активизированного банка памяти копия актуальной микрокоманды, которая поступает на информационные входы регистра 6 и подвергается контролю блоком 4.

Если ни в одном из сегментов считанной из блока 3 микрокоманды ошибок не обнаружено, то на выходе элемента ИЛИ 5 устанавливается уровень «О», который запрещает дальнейшую работу триггера 15, сбрасывает через элемент И-НЕ 14 счетчик 16 и разблокирует элементы И 12 и 13. Далее импульс с выхода 35 блока 11 проходит на выход элемента И 13 и загружает считанную микрокоманду в регистр 6. Таким образом, происходит восстановление работоспособности устройства в той точке микропрограммы, в которой имеется сбой. Последуюшее функционирование устройства осуществляется аналогично, но выборка микрокоманд происходит из первого банка блока 3.

Если в копии актуальной микрокоманды обнаружены ошибки в тех же или других сегментах ее формата, то на выходе элемента ИЛИ 5 сохраняется уровень «1». При этом работа элементов И 12 и 13 запрещена, а работа триггера 15 и счетчика 16 разрешена. С приходом импульса с выхода

35 блока 11 содержимое счетчика 16 увеличивается на единицу, а по импульсу с выхода

34 триггер 15, вновь переключается в состояние «О», что обеспечивает отключение первого банка и включение нулевого банка блока 3. Если блок 4 продолжает фиксировать ошибку, то вновь осуществляется инкремент содержимого счетчика 16. В процессе дальнейшего функционирования устройства считывание одной и той же микрокоманды происходит поочередно из обоих банков блока 3 до тех пор, пока либо осуществитсяя восстановление его работы по формиров анию трассы микропрограммы, гиб, количество считываний одной и той ж.:,n команды достигнет порогового значени:-.: втором случае на выходе элемента И 17 формируется сигнал «Отказ», который выдается на выход 23, а также через элемент ИЛИ 9 устанавливает устройство в исходное состояние.

Один из путей повышения отказоустойчивости предлагаемого устройства заключается в увеличении количества копий микрокоманд, В этом случае в качестве блока 15 следует использовать счетчик.

Микропрограммное устройство управления с контролем и восстановлением. содержащее счетчик ошибок, выходы которо; о соединены с входами первого элемента И, выход которого соединен с выходом неисправности устройства и первым входом первого элемента ИЛИ, выход которого соединен с К-входом RS-триггера режима. S-вход которого соединен с входом запуска устройства, прямой и инверсный выходы RS-триггера режима соединены соответственно с входами запуска и останова блока синхронизации, первый выход которого соединен со счетным входом триггера управления адресом и первым входом второго элемента И, выход которого соединен с тактов Ь|м входом регистра адреса и первым входом блока элементов И, группа выходов которого соединена с группой выходов микроопераций устройства, второй вход блока элементов И соединен с выходом поля микроопераций регистра микрокоманд, выход признака конца работы которого соединен с вторым входом первого элемента ИЛИ, выход признака конца команды регистра микрокоманд соединен суправляющим входом коммутатора, выход поля проверяемого логического условия и выход модифицируемого разряда адреса регистра микрокоманд соединены соответственно с адресным входом и первым входом группы информационных

1594533 входов муЛьтиплекСора, остальные входы группы информационных входов, которого соединены с входами логических условий устройства, выход мультиплексора соединен с первым входом первой группы информационных входов коммутатора, остальные входы первой группы информационных входов которого соединены с выходами немодифицируемых разрядов поля адреса регистра

Микрокоманд, вторая, группа информационных входов коммутатора соединена с группой входов кода операции устройства, выход коммутатора соединен с информационным входом регистра адреса, третий элемент И, блок памяти микрокомайд, с первой по q"þ группы выходов которого (где q — количество сегментов в формате микрокоманды) соединены с соответствующи ми группами информационных входов регистра микрокоманд и блока контроля, q выходов ошибки блока контроля Соединены с входами второго элемента ИЛИ, отличающееся тем, что, с целью сокращения ацпаратурных затрат, оно содержит элемент И-НЕ, первый вход которого .соединен выходом второго элемента ИЛИ и входом разрешения счета триггера управления адресом, второй вход элемента.И-НЕ соединен с прямым выходом RS-триггера режима, выход элемента И-НЕ соединен с входом сброса счетчика ошибок, вторым входом второго элемента И и первым входом третьего элемента И, выход которого соединен с тактовым входом регистра микрокоманд, вто1О пой вход третьего элемента И соединен со счетным входом счетчика ошибок и вторым выходом блока синхронизации, инверсный выход RS-триггера режима. соединен с входом сброса регистра микрокомаид и с входом, 15 сброса регистра адреса, выходы которого соединены с младшими разрядами адресного входа блока памяти микрокоманд; старший разряд адресного входа которого соединен с выходом триггера управления„. адресом, а третий вход первого элемента:

20 ИЛИ соединен с входом начальной установки устройства.

1594533

Составитель Ю. Ланцов

Редактор И. Горная Техред А. Кравчук Корректор А. Обручар

Заказ 2830 Тираж 573 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР ! !3035, Москва, )К вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород. ул. Гагарина, IOI