Устройство для адресации блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти. Целью изобретения является повышение надежности работы за счет способности устройства блокировать возможное прерывание выборки блока памяти до завершения сеанса обмена с блоком памяти. Устройство содержит группу переключателей 1, регистр 2 адреса, дешифратор 3 адреса, матричный коммутатор 4, элемент ИЛИ-НЕ 7, группу D-триггеров 8. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУ БЛИН

„„SU„„1594547 (51)5 G 06 F 12/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ бт

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21 ) 4487003/24-24 (22) 26.09.88 (46) 23.09.90. Бюл. У 35 (72) Н.Г.Пархоменко; В.Г.Черняев, В.Ю.Лозбенев н С.В.Козелков (53) 681.325(088.8) (56) Авторское свидетельство СССР

Р 1024926, кл. G 06 F 13/00, 1983.

Авторское свидетельство СССР

У 1388877, кл. G 06 Р 12/00р 1988. (54) УСТРОЙСТВО ДЛЯ АДРЕСАЦИИ БЛОКОВ

ПАМЯТИ ,(57) Изобретение относится к автома2 тике и вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти. Целью изобретения является повышение надежности работы за счет способности устройства блокировать возможное прерывание выборки блока памяти до завершения сеанса обмена с блоком памяти. Устройство содержит группу переключателей 1, регистр 2 адреса, дешифратор 3 адреса, матричный коммутатор 4, элемент ИЛИ-НЕ 7, группу Dтриггеров 8. 1 ил.

1 594547 ся невозможными, поскольку сигнал низкого уровня на выходе элемента

ИЛИ-НЕ, поступающий на синхровходы

D-триггеров, блокирует его переключение и сохраняет такое распределение памяти, которое существовалонепосредственно до подачи данного адреса об-. ращения.

Формула изобретения

Составитель А.Баркина

Техред М.Дидык ; Корректор A.0бРYчаР

Редактор A.Èîòûïü

Заказ 2831 Тираж 563 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

11роизводственно-издательский комбинат "Патент", r.Ужгород, ул. Гагарина, 101

Изобретение относится к автоматике и вычислительной технике и может быть использовано для адресации блоков памяти в системе памяти.

Целью изобретения является повыше5 ние надежности работы за счет способ" ности устройства блокировать возможное прерывание выборки блока памяти, до завершения сеанса .обмена с блоком памяти.

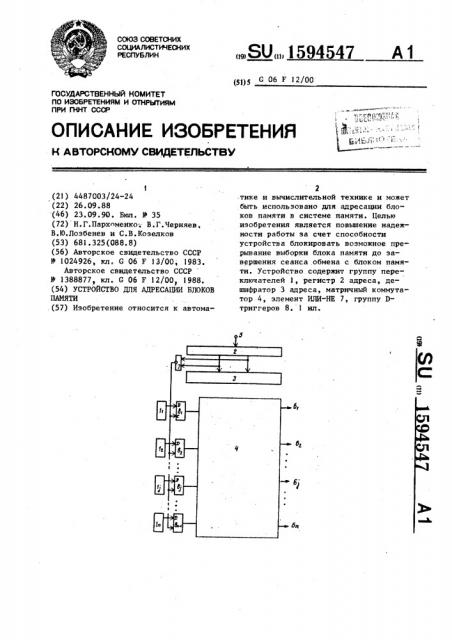

На чертеже представлена функциональная схема устройства.

Устройство для адресации блоков

; памяти содержит группу переключателей 1, регистр 2 адреса, дешифратор., 3 адреса, матричный коммутатор 4, вход 5 адреса, группу выходов б устройства, элемент ИЛИ-НЕ 7 и группу

Р"триггеров 8.

Устройство работает следующим образом.

На сеансе распределения памяти в соответствии с сигналами переключателей 1 сигнал высокого уровня на выходе переключателей 1-4 соответствует состоянию "Блок включен" (исправен), сигнал низкого уровня — "Блок выключен" (неисправен).

После сеанса распределения памяти устройство готово к работе в режиме внешних обращений. При этом j-му адресу обращения () =1,2,. ° .,и) всег да соответетвует j -й блек памяти из числа неотключенных и незанятых блоков памяти.

В режиме внешних обращений работа предлагаемого устройства не отличается от работы известного за исключением того, что при любом адресе обращения-и соответственно нри сеансе с выбранным блоком памяти переключения в матричном коммутаторе становятУстройство для адресации блоков памяти, содержащее группу из и переключателей (где и — количество адресуемых блоков памяти), регистр адреса, дешифратор адреса, матричный коммутатор, причем информационный вход регистра адреса является адресным входом устройства, выходы регистра адреса соединены с входами дешифратора адреса, выходы дешифратора адреса соединены с и входами первой группы матричного коммутатора, и выходов которого являются выходами устройства, о т л и ч а ю щ е е с я тем, .тем, что, с целью повьппения надежности работы sa счет способности устройства блокировать возможное прерывание выборки блока до завершения сеанса обмена с блоком памяти, в него введены элемент ИЛИ-НЕ и группа из п Dтриггеров, причем выходы регистра адреса соединены с входами элемента

ИЛИ-НЕ, выход элемента ИЛИ-НЕ соединен с входами синхронизации D-триггеров группы, их выходы — с соответствующими входами второй группы матричного блока коммутации, информационные входы D-триггеров соединены с выходами соответствующих переключателей группы.