Устройство для управления обменом информацией между управляющим процессором и внешним устройством

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и предназначено для управления обменом информацией в вычислительных системах, которые могут быть использованы для управления технологическими процессами, автоматическими линиями, робототехническими комплексами. Целью изобретения является повышение быстродействия и упрощение. Устройство содержит блок управления, дешифратор, мультиплексор, шинный формирователь. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИА ЛИСТ ИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1594552

А1 (51)5 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

f (21) 4479376/24-24 (22) 05.07.88 (46) 23.09.90. Бюл. 9 35 (71) Научно-производственное объединение технологии и оборудования сборочных работ в автомобильной промыш- . ленности "Автопромсборка" (72) С.А.Гороховик и И.Н.Сохина (53) 681.325(088.8) (56) Патент США Ф 4115856, кл. G 06 F 3/04, 1978 °

Авторское свидетельство СССР

У 1 208558, кл. С 06 F 13/00, 1986.

Изобретение относится к вычислительной технике и предназначено для управления обменом информацией в вычислительных системах, которые могут быть использованы для управления технологическими процессами, автоматическими линиями, робототехническими комплексами.

Целью изобретения является повышение быстродействия и упрощение устройства.

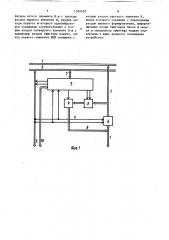

На фиг.l представлена структурная схема устройства сопряжения; на фиг.2 — структурная схема блока управления обмена.

Устройство содержит (фиг.l) вхо- ды-выходы 1 данных адреса, входы-выходы 2 управления, блок 3 управления, дешифратор 4, мультиплексор 5, шинный формирователь 6, входы и выходы 7-10.

2 (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ОБМЕН0М ИНФОРМАЦИЕЙ МЕМДУ УПРАВЛЯ10111ИМ

ПРОЦЕССОРОМ И ВНЕШНИМ УСТРОЙСТВОМ (57) Изобретение относится к вычислительной технике и предназначено для управления обменом информацией в вычислительных системах, которые могут быть использованы для управления технологическими процессами, автоматическими линиями, робототехническими комплексами. Целью изобретения является повышение быстродействия и упрощение. Устройство содержит блок управления, дешифратор, мультиплексор, шинный формирователь.

1 э,п. ф-лы, 2 ил.

Блок управления 3 обмена (фиг.2) содержит одновибраторы ll и 12, элементы И 13-17, триггер 18 блока, триггер 19 модуля, элементы ИЛИ 2021 н шинный формирователь 22.

Устройство для сопряжения работает следующим образом.

Обмен информацией между процессором (не показан) и внешними устройствами, в качестве которых могут быть блоки ввода-вывода (не показаны), происходит в асинхронном режиме.

Цикл обмена информацией начинается с выдачи адреса.

Процессор выдает сигнал "Выдача адреса" (ВА) и сигнал "Ввод-вывод" (ВВ), указывающий на то, что происходит обмен информацией между процессором и блоками ввода-вывода, а на входы -выходы 1 данных адреса — ад1594552 рс:H(>E . слово, которое поступает на вход мультиплексора 5.

Сигнал ВА поступает на вход элемента И 16 блока 3 управления, а на другой вход подается сигнал ВВ.

Выходной сигнал элемента И 16 снимает блокировку первого 11, второго 1 2 одновибраторов, триггера 18 блока и триггера 19 модуля.

Запуск первого 11 одновибратора. осуществляется сигналом "Синхронизация выдачи" (СВ), который сопровожда ет адресное слово, выдаваемое управляющим процессором. 15

На прямом выходе первого 11 одновибратора появляется импульс, который своим передним фронтом устанавливает . триггер 18 блока в состояние "1".

Сигнал с прямого выхода триггера 18 блока поступает на входы элемента

ИЛИ 20, элемента И 13 и на первый ... вход мультиплексора 5, на группе входов которого уже присутствует адресное слово. 25

По сигналу "Номер блока" мультиплексор 5 выбирает из адресного слова с шестого по девятый разряды, соответствующие номеру выбираемого блока. Выбранная информация с выходов 30 мультиплексора 5 поступает на входы дешифратора 4, на управляющий вход которого поступает сигнал с выхода элемента ИЛИ 20, разрешая дешифрацию информации. С выхода дешифратора 4

35 сигнал, несуший информацию о номере выбранного блока, поступает на соответствующий номеру блок ввода-вывода.

Блоки ввода-вывода подключаются таким образом, что каждый блок, имеющий 4 определенный номер от 0 до 15, подключен к соответствующим выходам дешифратора 4, имеющим такой же номер.

Сигнал выбора блока поступает на вход триггера подключения блока вво- 45 да-вывода (не показан). На синхровход этого триггера поступает сигнал " Номер блока" с элемента И 13, при этом задержка сигнала "Номер блока" относительно сигнала, несущего.информацию о номере блока, определяется длительностью блокирующего импульса, поступающего на вход элемента И 13 с инверсного выхода первого -одновибратора 1 1. Наличие этих двух сигналов на входах триггера подключения блока ввода-вывода устанавливают его в состояние "1", давая тем самым разрешение на обмен информацией между управляющич процессором и выбранным блоком ввода-вывода. После этого в выбранном блоке ввода-вывода формируется сигнал "Синхронизация приемап (СП), который поступает на вход триггера 1 8 блока и переводит его в исходное состояние. При этом снимается блокировка с мультиплексора 5, блокируется элемент И 13, снимается сигнал "Номер блока", а следовательно, и сигнал СП. Выбор блока ввода-вывода осуществлен.

Сигнал с инверсного выхода триггера 18 блока запускает второй одновибратор 12, импульс на прямом выходе которого своим передним фронтом устанавливает триггер 19 модуля в состояние "1". Сигнал с выхода триггера 19 модуля поступает на входы элементов ИЛИ 20, И 14 и 15 и на второй вход мультиплексора 5, который выбирает из адресного слова с третьего по пятый разряды, соответ-. ствующие номеру выбираемого модуля.

Как и в цикле выбора номера блока, сигнал с выхода элемента ИЛИ 20 разрешает дешифрацию информации, поступившей на адресные входы дешифратора 4. С выхода дешифратора 4 сигнал с дешифрированным номером модуля поступает в выбранный блок вводавывода на вход регистра номера модуля (не показан). Информация в регистр номера модуля записывается с приходом на его синхровход сигнала

"Номер модуля", поступающего с выхода элемента И 14. Задержка сигнала

"Номер модуля" относительно информационного сигнала определяется длительностью блокирующего импульса, посту- пающего на вход элемента И 14 с инверсного выхода второго одновибратора 12. Блок ввода-вывода формирует сигнал СП, указывающий на то, что модуль выбран. Этот сигнал подается в блок 3 управления обменом на вход элемента И 15, который вьщает сигнал

СП, извещающий управляющий процессор о том, что выдача адреса окончена.

Блокировка сигнала СП, вырабатываемого блоком ввода-вывода после приема номера блока, осуществляется сигналом с выхода триггера 19 модуля, так как выбор номер блока еще не является окончанием цикла выдачи адреса.

5 159

После получения сигнала СП управ-. ляющий процессор снимает адресное слово и сигналы ВА и СВ. Снятие сигнала ВА блокирует первый 11 и второй

12 одновибраторы, триггер 18 блока, триггер 19 модуля и элемент И 15. При

11 и этом снимаются сигналы Номер модуля, и CII. После окончания цикла выдачи адреса следует цикл записи информации в выбранный модуль или цикл чтения информации иэ выбранного модуля.

4552

20

25 формула изобретения

1.Устройство для управления обменом информацией между управляющим процессором и внешним устройством, со- держащее блок управления, дешифратор, мультиплексор, шинный формирователь., причем первая и вторая группы входов-выходов логического условия блока управления образуют группы входов-выходов устройства дпя подключения соответственно к группам входоввыходов синхронизации управляющего процессора, первый, второй выходы блока управления являются выходами устройства для подключения соответственно к первому, второму командным входам внешнего устройства, первая группа входов логического условия <-.: блока управления содинена с группой входой направления обмена шинного формирователя и образует группу входов устройства для подключения к группе командных выходов управляющего процессора, вход логического условия блока управления соединен с разрешающим входом шинного формирователя и является входом устройства для подключения к командному выходу управляющего процессора, при этом третий, четвертый и пятый выходы блока управления соединены соответственно с разрешающим входом дешифратора и с первым, вторым управляющими входами мультиплексора, о т л и ч а ю — . щ е е с я тем, что, с целью повыше-. ния быстродействия и упрощения, группа информационных входов мультиплексора соединена с первой группой информационных входов-выходов шинного формирователя и образует группу вхо, дов-выходов устройства для подключения к группе информационных и адресных входов-выходов управляющего процессора, вторая группа информационных

3(3

4С

55 входов-выходов шинного формирователя соединена с группой информационных выходов дешифратора н образует группу входов-выходов устройства для подключения к группе информационных и адресных входов-выходов внешнего устройства, при этом группа информационных выходов мультиплексора соединена с группой информационных входов дешифратора.

2.Устройство по п.1, о т л и ч а ющ е е с.я тем, что.блок управления содержит триггер блока, триггер модуля, шинный формирователь, два одновибратора, пять элементов И, два элемента ИЛИ, причем первая группа информационных входов-выходов шинного формирователя, выход первого элемента И и первый вход запуска первого одновибратора образуют первую группу входов-выходов логического

/ условия блока, вторая группа информационных входов-выходов шинного формирователя, синхровход триггера блока, соединенный с первым входом первого элемента И, образуют вторую группу входов-выходов логического условия блока, первый вход второго элемента

И соединен с первым входом третьего элемента И и является входом логического условия блока, второй вход второго элемента И, первый, второй входы первого элемента ИЛИ образуют группу входов логического условия блока, выходы четвертого, пятого элементов И являются соответственно первым, вторым выходами блока, выход второго элемента ИЛИ является третьим выходом блока, единичный выход триггера блока соединен с первыми входами четвертого элемента И, второго элемента ИЛИ и является четвертым выходом блока, единичный выход триггера модуля соединен с первым входом пятого элемента И, с вторыми входами первого элемента И, второго элемента ИЛИ и является пятым выходом блока, при этом в блоке управления выход второго элемента И соединен с нулевыми входами триггеров модуля и блока, с первым входом запуска второго одновибратора и с вторым входом запуска первого одновибратора, первый выход которого соединен с единичным входом триггера блока, нулевый выход которого соединен с вторым входом запуска второго одновибратора, первый выход которого соединен с вторым

1594552 входом пятого элемента И.и с третьим входом первого элемента И, вторые выходы первого и второго одновибраторов соединены соответственно с вторым входом четвертого элемента И и с единичным входом триггера модуля, выход первого элемента ИЛИ соединен с вторым входом третьего элемента И, выход которого соединен с управляюшим входом шинного формирователя, информа5 цнонные входы триггеров блока и модуля и синхровход триггера модуля пбд ключены к шине нулевого потенциала устройства.

Ф мультиплексору Ь

Р08. 2

Составитель С. Пестмал

Техред М.Дидык Корректор С.Шевкун

Редактор А.Мотыль

Заказ 2831 Тираж 566 . Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101