Устройство для нормализации сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и технической кибернетике. Цель изобретения - повышение точности нормализации сигналов при наличии шума. Устройство содержит аналого-цифровой преобразователь 1, регистры сдвига 2, 10, сумматоры 3, 7, цифроаналоговые преобразователи 4, 5, 8, делитель напряжений 6, блок 9 вычитания. В устройстве производится оценка уровня шума и вычитание значения оценки из входного сигнала, при этом автоматически регулируется уровень шума. Ограничение шумового процесса уменьшает погрешность нормализации смеси сигнала с шумом за счет уменьшения суммарной аддитивной помехи при априорно неизвестной длительности номируемого сигнала. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И) (5I)5 G 06 F 15/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И (ЛНРЫТИЯМ

ПРИ ГКНТ СССР (61) 542996

1 (21) 4610694/24-24 (22) 29.11.88 (46) 23.09.90. Б ол. N - 35 (72) О.М. Салтыковский (53) 681.3 (088.8) (56) Авторское свидетельство СССР

11 542996, кл. (" 06 F 15/36, 1974. (54) УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ СИГНАЛОВ (57) Изобретение относится к вычислительной технике и технической кибернетике. Цель изобретения — повышение точности нормализации сигналов при наличии шума. Устройство со2 держит аналого-цифровой преобразователь 1, регистры сдвига 2,10, сумматоры 3,7, цифроаналоговые преобразователи 4,5,8, делитель напряжений

6, блок 9 вычитания ° В устройстве производится оценка уровня шума и вычитание значения оценки из входного сигнала, при этом автоматически регулируется уровень шума. Ограничение шумового процесса уменьшает погрешность нормализации смеси сигнала с шумом за счет уменьшения сум- .

1 марной аддитивной помехи при априорно неизвестной длительности номируемого сигнала. 1 ил.

1594566

Изобретение относится к вычислительной технике, технической кибернетике, в частности к устройствам для распознавания сигналов, и является усовершенствованием устройства по авт,св. N 542996.

Целью изобретения является по:вышение точности при наличии шума.

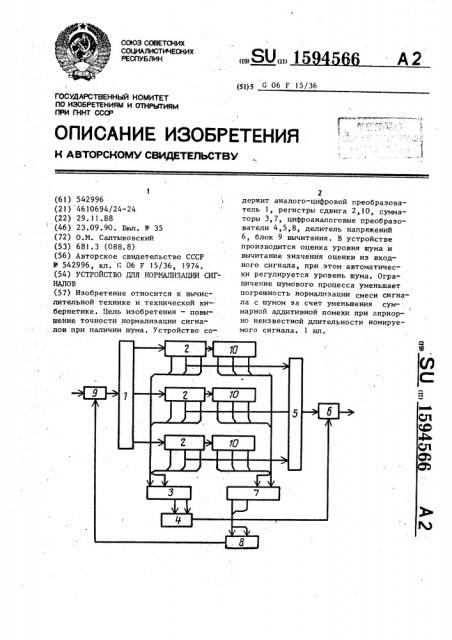

На чертеже приведена функциональная схема устройства.

Устройство содержит .аналого-цифровой преобразователь 1, регистры 2 сдвига, первый сумматор 3, первый 4 и второй 5 цифроаналоговые преобразователи, делитель 6 напряжения, второй сумматор 7, третий цифроаналоговый преобразователь 8, блок 9 вычитания, дополнительные регистры 10 сдвига.

Устройство работает следующим образом.

Входной сигнал в дискретные моменты времени преобразуется в аналого-цифровом преобразователе 1 в код, который поступает в регистры 2 сдвига, откуда он вновь преобразуется в цифроаналоговом преобразователе 5 в напряжение, поступающее на делитель 6 напряжения. Одновременно с выходов регистров сдвига импульсы кода поступают на младшие разряды сумматора 3, который производит вы=, числение площади сигнала плюс шум на удвоенном числе временных позиций, С выхода старших разрядов сумматора 3 код подается через цифроаналоговый преобразователь 4 на делитель 6 напряжений, Последний обеспечивает на выходе непрерывную во времени нормализацию сигнала относительно суммы, подсчитанной на удвоенном числе временных позиций. Задержка входного сигнала на п временных позиций (вход делителя напряжений 6.подключен через второй цифроаналоговый преобразователь 5 к и-му выходу регистров 2 сдвига) с одновременным расширением интервала определения нормы сигнала до и обеспечивает инвариантность нормированных сигналов на выходе устройства к сдвигу.

Вычисление площади сигнала (нормы сигнала) плюс шум на 2п временных позициях однако вносит погрешность в норму, определяемую шумом на п временных позициях. Особенно существенной становится эта ошибка при отличии длительности нормируемого сигнала от априорной длительности

В предлагаемом устройстве компенсация ошибки нормализации за счет паразитного шума на интервале С— где c — длительность нормируемого

7 сигнала, отличающаяся от априорной п 7

10 длительности с /2, достигается за счет вычитания из входного сигнала или шума сигнала уровня с автоматически устанавливаемого за счет цепи отрицательной обратной связи. Вычитаемый сигнал устанавливается за счет суммирования запомненных в К дополнительных разрядах регистров 2 сдвига временных отсчетов шума с последующими преобразованием кода стар20 ших разрядов сумматора 7 в напряжение в преобразователе. Уровень вычитаемого сигнала выбирается подключением соответствующего числа разрядов сумматора 7 и номинальным значе25 нием напряжения третьего цифроаналогового преобразователя 8.

Нормированный на выходе делителя 6 напряжений сигнал может быть выражен в виде

n(t) — шумовой процесс на входе устройства

1!ри с 7i 2 „вторым интегралом

$ (и(1:)-c)dt можно пренебречь.

Ь7

Тогда нормированный сигнал

x(t) — с

y(t) =

Г

Ь1

) (x(t)-comdt

С прямоугольного импульса x(t)=

E jo„ 7), что является нормибеэ ошибки

Для

=А, ровкой

y(t) ь1

Таким образом, вся ошибка нормиро55 вания определяется величиной второго интеграла, в котором событие n(t)7c происходит с вероятностью Р= g n(t)dt, о что при выборе достаточно высокого

30 x(t) — с у (t) = -- ——

I (x(c7 -cjdt + g (c(c7-c)dc

rye — длйтельность сигнала;

С - 0„— интервал, з анимаемый шумом

35 . в регистре 2 сдвига .

Составитель В. Орлов

ТехРед Л.Олийцьпс

Редактор M. Бланар

Корректор Лончакова

Заказ 2832

Тираж 566

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. гагарина, 101

5 1594566 6 порога приводит к уменьшению погреш- тор, третий цифроаналоговый преобра ности нормализации по сравнению с зователь и блок вычитания, причем известным устройством для сигналов i-й вход (i = 1,...,K) j-f,(j i,..., с априорно неизвестной дпнтеиьностью, и) группы второго сумматора соединен находящейся в некотором заданном ин- с i-м разрядным выходом j-ro дополнитервале. тельного регистра сдвига, информационный вход которого соединен с выФ о р м у л а и з о б р е т е н и я ходом j ro регистра сдвига, выход

Устройство для нормализации сиг- 1g группы старших разрядов второго сумналов по авт.св. N 542996, о т л и- матора соединен с входом второго ч а ю щ е е с я тем, что, с целью цифроаналогового преобразователя, повышения точности, в него введены выход которого соединен с входом

1 и (п — заданное число разрядов отсче- вычитаемого блока вычитания, выход тов сигнала) К-разрядных (К вЂ” задан- 15 коуорого соединен с входом аналогоное число отсчетов шума) дополнитель- цифрового преобразователя, а вход ных регистров сдвига, второй сумма- . является входом устройства.