Преобразователь угла поворота вала в код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством. С целью повышения динамической точности путем повышения быстродействия обработки входного воздействия в преобразователь, содержащий фазовращатель 4, компаратор 5, дифференцирующий элемент 6, элемент И 12, реверсивный счетчик 14, формирователь 15 синусоидального сигнала и сумматор 16, введены компаратор 7, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 8, блок 9 управления, триггер 10 элемент И 11, формирователь 13 опорного напряжения. Преобразователь работает в режиме фазовой следящей системы. На компараторе 5 производится сравнение по фазе выходного сигнала фазовращателя 4 с синусоидальным сигналом обратной связи, сформированным из кода реверсивного счетчика 14. Выходной код формируется в сумматоре 16 путем вычитания из кода реверсивного счетчика 14 опорного кода счетчика 2, включенного между генератором 1 и формирователем 3, вырабатывающим напряжение питания фазовращателя 4. Блок 9 и формирователь 13 выравнивают амплитуду сигнала обратной связи по отношению к выходному сигналу фазовращателя 4. 1 з.п. ф-лы, 2 ил.

(1% (ll) СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

y))5 Н 03 М 1/48, 1/64

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BT0PCHGMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4457698/24-24 (22) 11. О?, 88 (46) 23,09.90.Бюл, ¹- 35 (71) Омский политехнический институт (72) А, В,Бубнов, В. Г, Кавко, А,N.Мудрик и А.М.Сутормин (53) 681. 325 (088,8) (56) Авторское свидетельство СССР № 595755 ° кп. Н 03 М 1/64, 1976, Петропавловский В,П, и др, Фазовые цифровые преобразователи угла, M,:

Машино строение, 19 84, с, 33, рис. 3? ° (54) ПРЕОБРАЗОВАТЕЛЬ УГЛА ПОВОРОТА

ВАЛА В КОД (57) Изобретение относится Fc автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством, С целью повышения динамической точности путем повышения быстродействия обработки входного воздействия в преобразователь, содержащий фазовращатель 4, 2 компаратор 5, дифференцирующий элемент 6, элемент И 12, реверсивный счетчик 14, формирователь 15 синусоидального сигнала 4, сумматор 16, введены компаратор 7, элемент ИСКЛЮ"

ЧАЮЩЕЕ ИЛИ 8, блок 9 управления, триггер 10 элемент И ll формирователь

13 опорного напряжения, Преобразова- тель работает в режиме. фазовой следящей системы, На компараторе 5 производится сравнение по фазе выходного сигнала фазовращателя 4 с синусоидальным сигналом обратной связи, сформированным из кода реверсивного счетчика 14. Выходной код формируется в сумматоре 16 путем вычитания из кода реверсивного счетчика 14 опорного кода счетчика 2, включенного между генератором 1 и формирователем 3, вырабатывающим напряжение питания фазовращателя 4 ° Блок.9 и формирователь 13 выравнивают амплитуду сигнала обратной связи.по отношению к .;выходному сигналу фазовращателя,4 °

1 3 II ф-лы, 2 HJI

1594689

Изобретение относится к автоматике и вычислительной технике и может быть использовано для связи аналоговых источников информации с цифровым вычислительным устройством, Целью изобретения является повышение динамической точности преобразователя путем повышения быстродействия отработки входного воздействия, 19

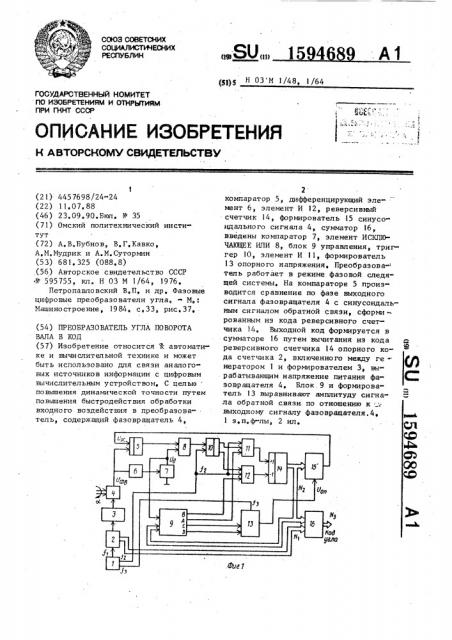

На фиг. l показана структурная схема преобразователя; на фиг.2 — структур-. ная схема блока управления.

Преобразователь угла поворота вала 15 в код (фиг.1) соцержит генератор 1 импульсов, счетчик 2, формирователь

3 синусоидального сигнала, фазоврацатель 4, компаратор 5, дифференцирующий элемент 6, компаратор 7;, элемент ИСКЛЮЧАЮЩЕЕ ИПИ 8, блок 9 управления.Ä 1 О, элементы И 11 и 12, формирователь 13 опорного напряжения, реверсивный счетчик 14, формирователь 15 синусоидального сигнала, сумматор 16, Блок 9 управления 1 фиг. 2 } содержит элемент ИСКЛЮЧАЮlllEE ИЛИ 17, инверторы 18 — 21, элементы И-НЕ 22 и 23, элементы И 24 и 25, триггер 26.

ЗО

Преобразователь работает следующим образом.

На вход счетчика 2 от генератора импульсов поступает сигнал частоты f Формирователь 3 синусоидального сигнала преобразует выходной сигнал счетчика 2 в синусоидальные напряжения, число которых определяется числом фаз фазовращателя 4 (при двухфазном питании фазовращателя 4 4п в формирователе 3 формируют два сдвинутых на 90" относительно друг друга синусоидальных сигнала) . Фазовращатель 4 преобразует угол оС поворота вала в фазу выходного напряжения

U фазовращателя, после чего сигнал U поступает на один из входов ув компаратора 5 и на вход дифференцирующего элемента 6. В компараторе 5 происходит непрерывное сравнение выходного сигнала У > фазовращателя

4 с сигналом U обратной связи.

Если выходное напряжение U фазовращателя 4 больше напряжения U, в цели обратной связи, на выходе компа-. ратора 5 будет получен сигнал, соответствующий логической 1", в противном случае выходной сигнал компара- . тора 5 станет равным уровню логического "0", В дифференцирующем элементе 6 формируют производную выходного сигнала фазовращателя 4, а компаратор ? преобразует данное напряжение в импульсный сигнал U3 поступающий на один вход элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ 8. На второй вход элемента 8 приходит выходной сигнал компаратора 5.

На участке возрастания выходного сигнала фазовращателя 4 его производная имеет положительный знак и вы ходной сигнал компаратора 7 равен логической "1". Нулевой уровень напряжения на выходе компаратора 5 показывает, что выходной сигнал U>z фазовращателя 4 отстает по фазе от сигнала У обратной связи, а уровень, равный уровню логической "1," соответствует опережению по фазе сигнапом U > сигнала U обратной связи, На участке убывания выходного сигнала фазовращателя 4 выходной сигнал компаратора 7 равен логи ческому "0", Нулевой уровень напря— жения на выходе компаратора 5 показывает опережение по фазе выходным сигналом U фазовращателя 4 сигнала

U обратной связи, а уровень, равный уровню логической "1", эквивалентен отставанию по фазе сигнала U от сигнала U обратной связи, Соответственно и выходной сигнал элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 8 равен "1" при отставании по фазе сигнала U вот сигнала U обратной связи и "0" при опережении по фазе сигналом Ц сигнала U обратной связи, С выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

8 сигнал поступает на информационный вход триггера 10, который переключается импульсами частоты f, формируемыми в генераторе I, Единйчный сигнал на прямом выходе триггера 10 разрешает прохождение через элемент

И 12 импульсов частоты Е на вычитаю-; щий вход реверсивного счетчика 14 (при условии отсутствия сигналов зап-. рета на выходе В блока 9), Уменьшение выходного кода N> счетчика 14 приво дит к соответствующему фазовому сдвигу аналогового сигнапа U обрат" ной связи, формируемому на выходе фор. мирователя .15, в результате чего устраняется отставание по фазе выходного сигнапа ц, фазовращателя 4 от сигнала U обратной связи, Таким образом осуществляют снижение сигна5 15 ла U обратной связи за выходным сигналом U фазовращателя 4, Аналогично происходит и в случае прихода единичного сигнала с инверсного выхода триггера 10, При этом откры вается элемент И 11 (при отсутствии сигнала запрета на выходе А блока 9) и разрешает прохождение импульсного сигнала частоты f< на суммирующий вход реверсивного счетчика 14 ° Выходной код N счетчика 14 увеличивается, вызывая изменение в формирователе 15 фазы сигнала Ц обратной связи, и устраняя тем са+ым опережение по фазе выходным сигналом U 8ôàçîâðàщателя 4 сигнала U: обратной связи, Так как сигнал U обратной связи преобразователя угла отслеживает из-: менения выходного сигнала U вфазовращателя 4, то код N реверсивного счетчика 14, эквивалентный фазе сигнала U обратной связи, соответствует и фазе (,в — — Qлt + A выходного н а УФв ф Оврщат я 4

Цифровой код N поступает на вход сумматора 16, где из него вычитают код N4, формируемый счетчиком 2 и эквивалентный фазе g =ó„t сигнала, питающего входные обмотки фазовращателя 4. В результате на выходе сумматора 16 получают код N = N — Я, пропорциональный углу оС поворота вала фазовращателя 4 °

Блок 9 и формирователь 13 предназначены для выравнивания ампнитуды сигнала Бц по отношению к сигналу

Upped Если выходнои THBJI формирователя 13 меньше амплитуды сигнала U

Т то при подходе к вершине сигнала U

Ф8 и увеличения кода N< сигнала Ugq не хватает амплитуды для слежения за сигналом U<<. Это приводит к даль» нейшему увеличению кода N<,переходу сигнала Uq через максимум и снижению .сигнала Uoñ при увеличении кода N2.

Для исключения поступления импульсов на суммирующий вход реверсивного счет-, чика 14 блок 9 управления вырабатывает сигнал А запрета, поступающий на вход элемента И 11, .Для исключения поступления импульсов на вычитан|ций вход реверсивного счетчика 14 блок 9 вырабатывает сигнал В запрета, поступающий на вход элемента И 12 °

Формирование сигналов з апрета осуще-. ствляется в блоке 9 путем логического сравнения двух старших разрядов реверсивного счетчика 14 и знака про94689 6 ного сигнала D с выхода блока 9 код в реверсивном счетчике формирователя

13 уменьшается, что приводит к уменьшению сигнала на выходе ЦАП формирователя 13 и уменьшению амплитуды сигнала Ц по сравнению с амплитудой сигнала U 8.

Таким образом, осуществляется непре» рывное отслеживание выходного кода сумматора 16 за изменением фазы вы ходкого сигнала фазовращателя 4 с одновременной регулировкой по амппиту» де сигнала обратной связи, который изводной сиги "а UФв ° Элемент 17 блока 9 вырабатывает единичный сигнал при несовпадении значений старшего. разряда кода N и выходного сигнала компаратора 7 ° Элемент И-HE 22 вырабатывает нулевой сигнал А запрета при совпадении единичных сигналов с выхо» дов элемента 17 и предпоследнего

1О старшего разряда реверсивного счетчика 14, Элемент И НЕ 23 вырабатывает нулевой сигнал В запрета при совпадении нулевых сигналов с этих же элементов, Нулевой сигнап А запрета с выхода элемента 22 инвертируется инвертором

20 и поступает в виде единичного сиг" нала С на вход формирователя 13, представляющего собой последовательно включенные реверсивный счетчик и цифроаналоговый преобразователь ЦАП, При единичном сигнале С импульсы частоты

f > с выхода генератора 1 поступают на суммирующий вход реверсивного счетчика формирователя 13, увеличивая его содержимое, что приводит к увеличению амплитуды опорного сигнала с вы хода формирователя 13 и увеличению амплитуды сигнала U

Аналогичные рассуждения можно про-. вести и для случая превышения по амплитуде сигнапом Ua сигнала U

Для уменьшения по амплитуде выходного сигнала формирователя 13 блок 9 вырабатывает единичный сигнал Э по совпадению нулевого сигнала В запрета с нулевым состоянием триггера 26, которое обеспечивается установкой его в "0" выходным сигналом элемента

40 И 24 по совпадению единичного сигна» ла с выхода предпоследнего старшего разряда реверсивного счетчика 14 и нулевого сигнала элемента 17 при отсутствии выходных импульсов С с выхо

45 да инвертора 20. При наличии единич! 594689 сравнивается по фазе с выходным сигналом фазовращателя 4, Ф О р м у л а и 3 О б p e т е н и я

1, Преобразователь угла поворота вала в код, содержащий генератор импульсов, первый выход которого соединен с входом счетчика, выход старшего 10 разряда счетчика соединен с входом первого формирователя синусоидального сигнала„выход которого соединен с входом фазовращателя, вап фазовращателя является входом преобразовате- )5 ля,,а выход фазовращателя соединен с первым входом первого компаратора, первый элемент И, выход которого соединен с первым входом реверсивного счетчика, выходы реверсивного счет- 20 чика соединены с первой группой входов сумматора, второй формирователь синусоидального сигнала, дифференцирующий элемент, о т л и ч а ю щ и йс я тем, что, с целью повышения ди намической точности преобразователя, в него введены блок управления, фор мирователь опорного напряжения, второй компаратор, элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ, триггер и второй элемент И, вы- 30 ход фазовращателя через дифференцирумций эл еме нт соедине н с одним входом второго компаратор а, другой: вход которого подключен к офцей шиче, а выход соединен с пеРвым вхо" дом блока управления и одним входсм элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, другой вход которого подключен к выходу первого компаратора, а выход соединен с информационным входом триггера, пря- 40 мой и инверсный выходы триггера соединены с первыми входами соответственно первого и второго элементов И, выход второго элемента И соединен с вторь|м входом Реверсивного счетчика, 45 выходы которого соединены с группой входов второго формирователя синусоидального сигнала, выходы двух старших разрядов Реверсивного счетчика соединены соответственно с BTopbtM u третьим входами блока управления, первый и второй выходы блока управления соединены с вторыми входами соответственно второго и первого элементов

И-, а третий и четвертый выходы соединены с первым и вторым входами формирователя опорного напряжения, выход которого соединен с входом второ го формирователя синусоидапьного сигнала, выход которого соединен с вторым входом первого компаратора, второй выход генератора импульсов соединен с входом синхронизации триггера и третьими входами первого и второго элементов И, а третий выход генератора импульсов соединен с третьим входом формирователя опорного напряжения, выходы разрядов счетчика соединены с второй группой входов сумматора, выходы которого являются выходами преобразователя, 2, Преобразователь по п, 1, о тл и ч а ю шийся тем, что блок управления содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре инвертора,,два рлемента И-НЕ, два элемента И и триггер, входы. элемента ИСКЛЮЧАК1ЦЕЕ ИЛИ являются первым и вторым входами блока управления, а выход элемента ИСКЛЮ»

ЧАЮЩЕЕ ИЛИ соединен с первым входом первого элемента И-НЕ и через первый инвертор с первыми входами второго элемента И-НЕ и первого элемента И, вход второго инвертора является третьим входом блока управления и соединен с вторыми входами первого элемента И-НЕ и первого элемента И, выход второго инвертора соединен с вторым входом второго элемента И-НЕ, выходы первого и второго элементов И- НЕ являются первым и вторым выходами блока управления и соединены с входами соответственно третьего и четвертого инверторов, выход третьего инвертора является третьим выходом блока управления и соединен с входом синхронизации триггера, информационный вход которого подключен к шине единичного потенциала, вход сброса - к выходу первого элемента И, а инверсный выход соединен с одним входом второго элемента И, другой вход второго элемента И подключен к выходу четвертого инвертора, а выход является четвертым выходом блока управления, l594G89

I

I

I !

Составитель А,Смирнов

Редактор Н,Лазаренко Техред Л.Олийнык Корректор М, Кучерявая

Заказ 2838 Тираж 671 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101