Устройство для измерения отношения частот последовательностей импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано для повышения точности измерения отношения частот последовательностей импульсов. Цель изобретения достигается за счет введения в устройство сумматора 8, датчика 9 единичного кода и новых функциональных связей. Кроме того, устройство содержит реверсивный счетчик 3, формирователь 4 разностной частоты, управляемый делитель 5 частоты и элемент 6 блокировки. Инверсия младшего разряда кода реверсивного счетчика 3, поступающего на управляющие входы управляемого делителя 5 частоты, и инкрементирование на единицу в сумматоре 8 прямого выходного кода реверсивного счетчика 3 приводит к образованию гистерезисных циклов в зависимости выходного кода устройства от отношения входных частот, что за счет устранения неопределенности представления выходного результата приводит к повышению точности измерения. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) (111 (g) G 01 R 23/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCROMV СВИДКтЕЛЬСтВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР. (21) 4470048/24-21 (22) 01.08.88 (46) 30.09 ° 90.Бюп, N- 36 (?2) N,Н.Зайкин, В,Ф.Брагинский, И.И,Четверкин, В,И.Журавский и И.A,Êàðïîâè÷ (53) 681,317 (088, 8) (56) Авторское свидетельство СССР

Р 1262405, кл. G 01 R 23/00, 1985 ° (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОТНО1!1ЕНИЯ ЧАСТОТ ПОСЛЕДОВАТЕЛЬНОСТЕЙ

ИМПУЛЬСОВ (57) Изобретение относится к импульсной технике и может быть использовано для повышения точности измерения отношения частот последовательностей импульсов, Цель изобретения достигается за счет введения в устройство

Изобретение относится к импульсной технике и может быть использовано для измерения частот следования импульсных сигналов, Целью изобретения является повышение точности измерения за счет устранения неопределенности представления результата измерения.

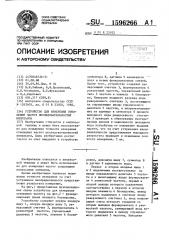

На фиг, 1 представлена функциональная схема устройства дпя измерения отношения частот; на фиг,2 - функциональная схема элемента блокировки, Устройство содержит первую входную шину 1, вторую входную шину 2, реверсивный счетчик 3, формирователь 4 разностной частоты, управляемый делитель 5 частоты, элемент 6 блоки2 сумматора 8, датчика 9 единичного кода и новых функциональных связей, Кроме того, устройство содержит реверсивный счетчик 3, формирователь 4 разностной частоты, управляемый делитель 5 частоты и элемент 6 блокировки, Инверсия мпадшего разряда кода реверсивного счетчика 3, поступакицего на управляющие входы управляемого .делителя 5 частоты, и инкрементирова ние на единицу в сумматоре 8 прямого выходного кода реверсивного счетчика 3 приводит к образованию гистерезисных циклов в зависимости выходного кода устройства от отношения входных частот, что за счет устранения неопределенности представления выходного результата приводит к повышению точности измерения, 2 ил, ровки, выходную шину 7, сумматор 8 и датчик 9 единичного кода.

Первая и вторая входные шины 1 и. 2 подключены соответственно ко входу управпяемого делителя 5 частоты и к вычитающему входу формирователя 4 разностной частоты, первый и второй выходы которого подключены соответственно к первому и второму входам элемента 6 блокировки, выход которого подключен к счетному входу реверсивного счетчика 3, вход направления счета которого соединен со вторым выходом формирователя 4 разностной частоты, суммирукщий вход которого подключен к выходу управляемого делителя 5 частоты, Выходная

159 шина 7 подключена к группе выходов всех разрядов сумматора 8, кроме младшего, Выходы датчика 9 единичного кода подключены к входам первого слагаемо ro сумматора 8, входы второ ro слагаемого которого подключены к выходам реверсивного счетчика 3, группа разрядных выходов которого, кроме младшего разряда, подключена к информационным входам элемента 6 блокировки и к группе управлякщих входов управляемого делителя 5 частоты, упраапякщий вход которого подключен к инверсному выходу мпадшего разряда реверсивного счетчика 3.

Элемент 6 блокировки содержит элемент ИЛИ 10 элемент И-НЕ 11, коммутатор 12 и элемент И-НЕ 13, Информационные входы элемента

6 блокировки подключены ко входам элемента ИЛИ 10 и элемента И-HE 11, выходы которых подключены соответственно к первому и второму входам коммутатора 12, выход которого подключен к первому входу элемента И 13, выход которого является выходом эле- . мента 6 блокировки ° Первый и второй входы элемента 6 блокировки подключены соответственно к управлякщему входу коммутатора 12 и ко второму входу элемента И-НЕ 13>

Устройство работает следукяцим образом, Последовательности импульсов делимого и делителя с частотами К и f соответственно поступают с первой и второй входных шин 1 и 2 йа вход управляемого делителя 5 частоты и вычитакщнй вход формирователя 4 разностной частоты, На выходе управляемого делителя 5 частоты формируется последовательность с частотой

f

11 К поступакщая на суммирун|ций вход формирователя 4 разностной частоты, где К-коэффициент деления управлямого делителя 5 частоты, задаваемый числовым кодом К на его информационных входах, поступаклцим с информационных выходов реверсивного счетчика 3, При этом минимальному коэффициенту деления К=1 соответствует числовой код K =* (0; 0; 0;...

0; 0) на информационных входах управляемого делителя 5 частоты, т,е, К= К +

6266

С первого выхода формирователя 4 разностной частоты на первый вход элемента 6 блокировки поступает последовательность импульсов с частотой.

f 1 г f„4 (2) 30 К =2-1 К =2 г 1> (3) где и - целое число, Значениям числовых кодов К и

К на прямых информационных выходах

1 реверсивного счетчика 3 будут соответствовать, с учетом инверсного информационного выхода первого разряда, коэффициенты деления К, и К управляемого делителя 5 частоты:

К,, 2 п-1; Кz = 2„+2, (4) удовлетворякщие условию

45 (5) 2 К К у соответствующему установившемуся режиму работы устройства.

При условии

f1 (c ——

f1 (6)

2 правая часть выражения (2) отлична от нуля, поэтому числовой код К на пряьых информационных выходах реверсивного счетчика 3 колеблется внутри измерительного интервапа в

10 а уровень напряжения на втором выходе формирователя 4 разностной частоты, поступакщий на вход направления счета реверсивного счетчика 3, оп.ределяет знак разности частоты в !

5 формуле (2), причем уровень логической 1 соответствует неравенству

f1 fг

Импульсы разностной частоты поступают с первого выхода формирователя

4 разностной частоты через элемент 6 блокировки на счетный вход реверсив ного счетчика 3 и изменяют его состоя. ние до тех пор, пока на прямых информационных выходах реверсивного счетчика 3 не появится одно из двух значений числового кода К, соответствукщих границам измерительного интервала, равных

1596266 6 и поочеред- находящемся в пределах измерения устК 2, а при ройства, 1У Ь

В то же время числовои код К с (7) прямых информационных выходов ревер5 сивного счетчика 3 поступает на информационные входы сумматора 8, где к

II u нему прибавляется код числа 1, т.е, числовой код К" на информационных выходах сумматора определяется как: пределах одного разряда но принимает значения К условии

f, К1

f. к

1 или Г2

К"= К + 1 — а(К ° К

f1

- 1>

2 (8) Ц II

К /О

2 (12) 35 ся интервал (9) разностная частота f, = О и числовой код К принимает одно из значений

К или К2 соответственно, 10

Из условия (5) следует, что величина измеряемого отношения средних значений частот f, и f находится в интервале

15 соответствующем интервапу t K1; числового кода К на прямых информа20 ционных выходах реверсивного счетчика 3, При выходе из меря емо го о тнош ения средних значений частот f 1 и Е за пределы измерительного интервала (8)

«25 например, вследствие изменения среднего значения одной из частот f, или состояние реверсивного счетчика

3 изменяется и.формируется новый. измерительный интервал, определяющий границы измеряемого отношения сред30 них значений частот f, и f, Так, например, при увеличении отноше 1 ния частот .при — — )K формируетf- z

Операция сложения видоизменяет числовой код К таким образом, что каждому описанному интервалу измерения отношения средних значений частот f u f заключенному между

1 2 двумя состояниями числового кода К, отличающимися на "1", соответствуют два состояния числового кода К" на информационных выходах сумматора 8,, старшие разряды которых„начиная со второго разряда, остаются неизменными в пределах любого отдельно взятого измерительного интервала, Это позволяет получить на информационных выходах старших разрядов, начиная со второго разряда, сумматора 8 числовой код К", равный причем каждому из описанных измерительных интервалов соответствует только одно значение числового кода К" или с учетом (4), (8), (11), (12) причем

40 (10) К=2+1 К=2+4

3 и 4 и

Процесс происходит до тех пор, пока устройство не перейдет в новый установившийся режим, соответствую- 45 щий новой величине отношения средних . . -значений частот f иГ

Из сопоставления выражений (4 ) и (10 1 следует, что измерительные интервалы, образованные числовым кодом 50

К, частично перекрывают друг друга, Образовавшиеся таким образом гисте, резисные циклы в зависимости

t f!

К () исключают кол еб ательные

ft 55 переходы из одного измерительного ин тервала в соседний в установившемся режиме работы при любом соотношении средних значений частот f, и f<, 2К (13) 2

При выходе величины числового кода К за предельные значения работа управляемого делителя 5 частоты, имеющего N разрядов, будет нарушена,Поэтому с целью ограничения изменения числового кода К в указанных пределах информационные выходы старших разрядов, начиная со второго разряда реверсивного счетчика 3, соединены с информационными входами элемента б блокировки, который блокирует реверсивный счетчик 3 при достижении числовым кодом К указанных . пределов, Блокирование реверсивного счетчика 3 происходит следующим образом.

На второй вход реверсивного счетчика 3 и на второй вход элемента 6

?596266 блокировки со второго выхода формирователя разностной частоты 4 поступает уровень напряжения, соответствующий, например» вычитающему режиму работы реверсивного счетчика 3, на первый вход которого с выхода элемента 6 блокировки поступают импульсы разностной частоты, При этом состояние реверсивного счетчика 3 изме- 0 няется в сторону уменьшения до тех пор, пока на всех его информационных выходах старших разрядов, начиная со второго разряда, не появлятся "О", что соответствует предельному значе- 15

1 нию К, При этом поступление имммн пульсов разностной частоты с выхода элемента блокировки 6 на первый вход реверсивного счетчика 3 прекращается до тех пор, пока на втором входе gp элемента 6 блокировки не установится уровень напряжения, поступающий со второго выхода формирователя 4 раэностной частоты, соответствующий суммирующему режиму работы реверсивного счетчика 3, Аналогичным образом реверсивный счетчик 3 блокируется при появлении

"!" на всех его информационных выходах старших разрядов, начиная со второ- 30 го разряда что соответствует пре- . ! дельному значению К „ „

В предложенном устройстве по сравнению с устройством-прототипом уст-. раняется неопределенность представления результата измерения при дробном соотношении частот f и f, что приводит к повышению точности измерения, Формул а из обретения 40

Устройство для измерения отношения частот последовательностей импульсов, содержащее первую и вторую входные шины, элемент блокировки, управляемый делитель частоты, выходную шину и реверсивный счетчик, группа разрядных выходов которого подкпючена к группе управляющих входов управляемого делителя частоты, вход которого подключен к первой входной шине, формирователь разностной частоты, суммирующий и вычитающий входы которого подключены соответственно к выходу управляемого делителя частоты и к второй входной шике, о т л и ч а ю щ е е с я тем, что, с целью повышения точности измерения за счет устранения неопределенности представления результата измерения, в него введены сумматор и датчик единичного кода, выходы которого подключены к входам первого слагаемого сумматора, входы второго слагаемого которого подключены соответственно к прямому выходу младшего разряда реверсивного счетчика и к группе разрядных выходов реверсивного счетчика, инверсный выход младшего разряда которого подключен к управляющему входу управляемого делителя частоты, первый и второй выходы формирователя разностной частоты подключены соответственно к первому и второму входам элемента блокировки, выход которого подключен к счет" нОму входу реверсивного счетчика, вход направления счета которого подключен. к второму выходу формирователя разностной частоты, информационные. входы которого соединены с группой разрядных выходов реверсивного счет" чика, группа разрядных выходов сум", матора подключена к выходной шине устройства, 1

1596266

Фиг.1

Ин рврмационные

ЬоГЬ

Составитель А„Перфильев

Редактор Н,Горват Техред Л.Олийнык

Корректор Н,Король

Заказ 2907 Тираж 561 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 101