Устройство для возведения в квадрат двоичных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть применено в специализированных вычислительных устройствах для оперативного вычисления функции Y=ΣA IX I и других функций, сводящихся к ней, например в системах автоматического управления быстропротекающими процессами. Цель изобретения - расширение класса решаемых задач за счет вычисления функций Y=ΣA IX I при одновременном сокращении аппаратных затрат. Устройство содержит две группы элементов И, две группы счетчиков, две группы сумматоров, квантователь, преобразователи код - временной интервал, регистры операндов X I, X I, A I с соответствующими связями. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 7/552

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4443239/24-24 (22) 19.05.88 (46) 30.09.90. Бюл. ¹ 36 (71) Хмельницкий технологический институт бытового обслуживания (72) В.Ф.Бардаченко, В.Н.Локазюк, А.А.Магера и Г.С.Носовицкий (53) 681.325(088,8) (56) Авторское свидетельство СССР № 911520, кл. G 06 Г 7/552, 1982,.

Авторское свидетельство СССР

¹ 628487, кл, G 06 F 7/552, 1978. (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В

КВАДРАТ ДВОИЧНЫХ ЧИСЕЛ (57) Изобретение относится к вычислительной технике и может быть применено в специализированных вычислительных

Изобретение относится к вычислительной технике и может быть применено в специализированных вычислительных устройствах для оперативного вычисления

2 функции у = а Xi .и других функций, сво-! =1 дящихся к ней, например в системах автоматического управления быстрои ротекающими процессами.

Цел b изобретения — расширение . класса решаемых задач за счет обеспечения, возможности вычисления функции у = а Xi при одновременном сокраще2

1=1 нии аппаратурных затрат.

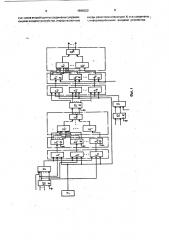

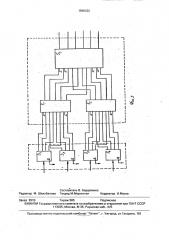

На фиг. 1 представлена блок-схема устройства для возведения в квадрат двоичных . чисел; на фиг. 2 — схема соеДинения сумматоров в первой и второй группах.!

Ж, 1596322 А1 устройствах для оперативного вычисления функции у =,) a Xi и других функций, сво2

1 =1 дящихся к ней, например в системах автоматического управления бь<стропротекающими процессами. Цель изобретения — расширение класса решаемых задач за счет вычисления

2 функций у = g aiXi при одновременном со-!

=1 кращении аппаратных затрат. Устройство содержит две группы элемента И, две группы счетчиков, две группы сумматоров, квантователь, преобразователи код — временной интервал, регистры операндов Хь Х, а; с

2 соответствующими связями. 2 ил.

При и = 4 устройство содержит группы элементов И 11 — 1> и 21 — 2, группы счетчиков 31 — Зп. и 41 — 4, группы сумматоров 51—

5л-1 и 61 — 61-1, квантователь 7, преобразователи 8 и 9 код — временной интервал и регистры 10-12 соответственно операндов

Х,Х .аь .2

УстройСтво работает следующим образом.

Перед началом работы сбрасываются все регистры и сумматоры устройства, По входу данных значение Xi "-асылается в параллельном коде в регистр 10 и подается на .. входы первого преобразователя 8 код — временной интервал. На выходе первого преобразователя 8 образуется аналоговый таймерный сигнал, соответствующий цифровому операнду Хь который поступает на пеРвые вхоДы элементов И 11 — 1л пеРвой группы элементов И, на третьи входы элементов И 11 — 1л подается серия эаполняю1596322 щих импульсов из квантователя 7 с такой частотой, что при равенстве разряда операнда Х1 "1н на выходах элементов И образуется количество импульсов, равное двоичному коду операнда Хь подаваемому с выхода первого преобразователя 8, а при равенстве разряда н0и импульсы не образуются. На вторые входы элементов И 11 — 1П с регистра 10 подаются разряды операнда

Х1, причем младший разряд подается на элемент 11, следующий разряд — на элемент

12 и т,д., а старший разряд подается на элемент 1л. Импульсы с выходов элементов

И 11 — 1л поступают на последовательные счетные входы счетчиков 31 — Зп, где они суммируются и представляются на выходах счетчиков 31 — 3 в параллельном коде. Суммирование частичных произведений со сдвигом на один разряд влево осуществляется первой группой сумматоров 51 — 5п-1.

Первый выход счетчика 31 соединен с первым входом сумматора 51 второй вход которого соединен с нулевой шиной, второй выход счетчика 31 соединен с третьим входом сумматора 51, четвертый вход которого соединен с первым выходом счетчика 32 и т,д., (2п — 1)-й вход сумматора 51 соединен с нулевой шиной, а 2п-й вход сумматора 51— с и-м выходом счетчика 32. Таким образом, на выходе сумматора 51 устанавливается сумма частичных произведений со сдвигом на один разряд влево со счетчиков 31 и 32 и т.д. Таким образом, на выходе сумматора

5П-1 устанавливается результат суммирования частичных произведений Хь начиная с первого, со сдвигом каждого последующего влево на один разряд, далее записываемый в регистре 11. На шине данных выставляется значение операнда аь которое засылается в параллельном коде в регистре 12 и подается на входы второго преобразователя 9 код — временной интервал, который запускается управляющим входом, На вы-. ходе второго преобразователя 9 образуется аналоговый таймерный сигнал, соответствующий цифровому операнду аь который поступает на вторые входы элементов 21 — 2, на первые входы элеме,i1os И 21 — 2 по;- даются разряды операнда Х с регистра 11, причем младший разряд подается на элемент И 21, следующий разряд — на элемент

И 22, а старший разряд — на элемент И 2, на третьи входы элементов И 21 — 2k подается серия заполняющих импульсов из квантователя 7. Импульсы с выходов элементов И 21 — 2 подаются на последовательные счетные входы счетчиков 41 — 4, где суммируются, и сумма представляется на выходах счетчиков 41 — 4 в параллельном коде. Суммирование со сдвигом частичных

15 произведений происходит так как и в группе сумматоров 5, посредством группы сумматоров 61 — 6k-1. Таким образом, на выходе сумматора 6к-1 устанавливается значение функции а Х . Для следующего цикла сбрасывается содержимое регистров

10 — 12, первой группы 3 счетчиков, группа

4 счетчиков остается в прежнем состоянии и после вычисления значения агХ2 сумми2 рует значение а1Х1 + a2X22 и т.д. По окончании вычисления функции у = Zp1Xi .Ь г

1=1 результат считывается с выхода сумматора

6К-1

Формула изобретения

Устройство для возведения в квадрат двоичных чисел, содержащее регистр операнда Хь регистр операнда Х, первую и вторую группы элементов И, о т л и ч а ю щее с я тем, что, с целью расширения класса решаемых задач за счет возможности вы25 числения функции у= а Х при одноереI=i менном сокраи ении аппарауурных затрат, в него введены регистр операнда аь первый и второй преобразователи код — временной

30 интервал, квантователь, первая и вторая группы сумматоров, первая и вторая группы счетчиков, счетные входы которых подключены к рыходам элементов И первой и второй групп соответственно, первые, вторые и

35 третьи входы элементов И первой группы соединены с выходами первого преобразователя код — временной интервал, регистра операнда Х и квантователя соответственно, выходы счетчиков первой группы подключе40 ны " входам сумматоров одноименной группы, выходы последнего сумматора первой группы соединены с входами регистра операнда Х, выходы которого подключены к первым входам элементов И второй группы, 45 вторые и третьи входы элементов И которой соединены соответственно с выходами второго преобразователя код — временной интервал и квантователя, выходы регистров операндов Xi и э соединены с входами со50 ответственно первого и второго преобразователей код — временной интервал, выходы счетчиков второй группы подключены к входам сумматоров одноименной группы, выходы последнего сумматора которой

55 . являются выходами устройства, входы сброса регистров операндов Хь Х, а и счетчиков .

2 первой группы объединены и подключены к входу сброса устройства, управляющие входы первого и второго преобразователей код — временной интервал и входы сброса 1

1596322 счетчиков второй группы соединены суправляющими входами устройства, информационные входы регистров операндов Xi u at соединены = с информационными входами устройства.

1596322

Редактор

Заказ 2910 Тираж 565 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

f

f !

l

i

l

l !

f ! !

I

1 ! !

) Ф !

l !

I а

Составитель 8. Бардаченко

М. Шелобанова Техред M.Ìoðãåíòàë Корректор И.Муска