Устройство для вычисления логарифмической функции

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах для воспроизведения логарифмических функций. Цель изобретения - расширение области применения за счет увеличения диапазона изменения аргумента. Поставленная цель достигается тем, что устройство содержит вход начального значения аргумента, блок формирования коэффициента, первый и второй блоки нормирования, три вычитателя, два умножителя, сумматор, выход результата, два шинных коммутатора, два регистра, вход задания констант, блок памяти констант, блок сравнения, блок синхронизации, вход сигнала "пуск", накапливающий сумматор, первый и второй элементы ИЛИ. Блок синхронизации содержит генератор тактовых импульсов, триггер, первый и второй элементы И, элемент ИЛИ, сдвиговый регистр. Блок формирования констант содержит генератор, элемент И, триггер, первый и второй сдвиговые регистры. Блок нормирования содержит генератор, элемент И, триггер, первый и второй сдвиговые регистры. Работа устройства основана на соотношении Y I+1 = (2 - X I/Α I) Y I - (1- X I/Α I) Y I-1 + H/Α I, I= 1,2 ...,K Y 0, Y 1, X 1, H, X K - заданные значения. 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (s3)5 G 06 F 7/556

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4379448/24-24 (22) 15.02.88 (46) 30.09.90. Бюл. М 36 (71) Таганрогский радиотехнический институт им. В.Д.Калмыкова (72) В, Ф.Арсе ни, М.Е. Бородянский, И.Ф.Сурженко, И.Н.Волков и Г,И,Браиловский (53) 681.325(088.8) (56) Авторское свидетельство СССР

М 448459, кл. G 06 F 7/38, 1974, Авторское свидетельство СССР

hL 930314, кл. G 06 F 7/556, 1980. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМИЧЕСКОЙ ФУНКЦИИ (57) Изобретение относится к вычислитель. ной технике и может быть использовано в цифровых вычислительных машинах для воспроизведения логарифмических функций. Цель изобретения — расширение области применения за счет увеличения диапазона изменения аргумента. Поставленная цель достигается тем, что устройство

Изобретение относится к вычислитель-ной технике и может быть использовано в цифровых вычислительных машинах воспроизведения логарифмических функций.

Цель изобретения — расширение обла сти применения за счет увеличения диапазона изменения аргумента.

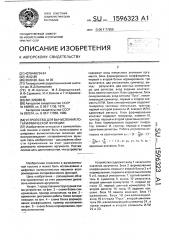

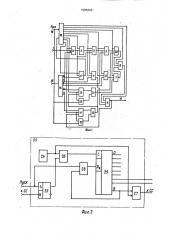

На фиг. 1 представлена структурная схема устройства; на фиг. 2 — схема блока синхронизации, пример исполнения; на фиг. 3— временная диаграмма работы блока синхронизации; на фиг. 4 — схема блока формирования коэффициента, пример исполнения;., .на фиг. 5 — схема блока нормирования, пример исполнения, Ы, 1596323 А1 содержит вход начального значения аргумента, блок формирования коэффициента, первый и второй блоки нормирования, три вычитателя, два умножителя, сумматор, выход, результата, два шинных коммутатора, два регистра, вход задания констант, блок памяти констант, блок сравнения. блок синхронизации, вход сигнала "Пуск", накапливающий сумматор, первый и второй элементы ИЛИ. Блок синхронизации содержит генератор тактовых импульсов, триггер, первый и второй элементы И, элемент ИЛИ, сдвиговый регистр. Блок формирования констант содержит генератор, элемент И, триггер, первый и второй сдвиговые регистры. Блок нормирования содержит генератор, элемент И, триггер, первый и второй Б сдвиговые регистры. Работа устройства осх нована на соотношении у +1 = (2 — — )у -(1—

СЦ х h — @)у -1 +@, 1 = 1,2...,1с; уо. у1, xi, h, хк— заданные значения. 5 ил, Устройство, содержит вход 1 начального значения аргумента, блок 2 формирования . коэффициента, первый и второй блски 3 и 4 нормирования, первый и второй вычитатели

5 и 6, первый умножитель 7, третий вычитатель 8, сумматор 9, выход 10 результата, второй шинный коммутатор 11, первый регистр 12, первый шинный коммутатор 13. второй регистр 14, вход 15 задания констант, блок 16 памяти конс. ант, блок 17 сравнения, блок 18 синхронизации, вход 19 сигнала "Пуск", второй умножитель 20, накапливающий сумматор 21, а также первый и второй элементы ИЛИ

22 и 23.

1596323

Б лок синхронизации образуют генератор 24 тактовых импульсов, триггер 25, первый и второй элементы И 26 и 27, элемент

ИЛИ 28 и сдвиговый регистр 29.

Блок формирования коэффициента включает генератор 30, элемент И 31, триггер 32, а также первый и второй сдвиговые регистры 33 и 34.

Блок нормирования содержит генератор 35, элемент И 36, триггер 37, первый и второй сдвиговые регистры 38 и 39, Устройство работает следующим образом.

Для воспроизведения значений функции у = Inx использован модифицированный алгоритм Эмбла

dy =ф(а„— х) dy+ dx), (1) где а — определенный параметр, Решением (1) является функция у = Inx.

Уравнению (1) соответствует разностный аналог ун- = (2 — — )у» — (1 — — )у»-> + —,, х» х» а» Ol Q

i = 1,2...,N; (2)

Каноническая форма (2) имеет вид у» + 1 = Ai )i +т» у0 задан где х» — 2 ——

A> = а»

1 х»

-1 + Т=

О. (3) Параметр а вырабатывается в устройстве согласно условию 11 х 11 > Ql, поэтому в интервале(а,Ь) норма оператора Аь определяемая по формуле (3), не превосходит единицы, С целью увеличения быстродействия (2) параметр а» должен быть числом, бли жайшим к х и кратным 2 . Например, х=0,126, а=0,125=2 3,k=3.

Формула методической погрешности для (2) имеет вид

13 (х 1} . (4)

8 х

В исходном состоянии по входу 15 задания констант заносятся величины h, у, у, хр. Шинные коммутаторы 13 и 11 устанавливаются в состояние, обеспечивающее подключение выходов блока 16 памяти констант к входам регистров 14 и 12 соответственно. По приходу импульса по входу

19 сигнала "Пуск" в регистры 14 и 12 соответственно заносятся величины уо.и у1, а блок 18 синхронизации начинает вырабатывать последовательность импульсов. В блоке 2 формирования коэффициента по

Ф ормула изобретения

Устройство для вычисления логарифми- ческой функции, содержащее первый и второй регистры, первый и второй элементы

ИЛИ; сумматор и блок синхронизации, причем вход запуска блока синхронизации соединен с входом "Пуск" устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет увеличения диапазона изменения аргумента, оно содержит блок формирования коэффициента, первый и второй блоки нормирования, первый и второй шинные коммутаторы. блок сравнения, первый, второй и третий вычитатели, первый и второй умножители, накапливающий сумматор и блок памяти констант, причем вход задания констант успервому импульсу осуществляется формирование коэффициента а, по второму импульсу в блоках 3 и 4 нормирования формируются величины х/а и h/da по

5 третьему импульсу в вычитателе 5 формирух» ется величина (2 = ), а в вычитателе 6—

Q х» величина (1 — — ), по четвертому импульсу в

10 умножителе 20 формируется произведение х» у (2 — — ), а в умножителе 7 — произведение а» х у0(1 — — ), по пятому импульсу в вычитателе

15 xi x»

8 формируется разность у (2 — — ) - у (1-@) а» по шестому импульсу в сумматоре 9 формируется значение у2, по седьмому импульсу шинный коммутатор 13 переключается в по20 ложение, при котором выход регистра 12 подключается к входу регистра 14 и информация из регистра 12 заносится в регистр

14, т,е. вместо у0 записывается yi. По восьмому импульсу шинный коммутатор 11 пе25 реключается в положение, при котором выход сумматора 9 подключается к входу регистра 12 и происходит перезапись значения уг в регистр 12 вместо у . Одновременно в накапливающем сумматоре 21 осуществ30 ляется увеличение числа xi на величину 1», которая на девятом такте сравнивается с.хк в блоке 17 сравнения. Если выполняется равенство xi< = Ih + х, то на выходе блока сравнения появляется сигнал, останавлива.

35 ющий устройство и являющийся признаком окончания вычислений. В противном случае блок 18 синхронизации вырабатывает новую последовательность из девяти импульсов, причем по шестому импульсу на выходе

40 10 результата формируется очередное значение функции согласно алгоритму (1).

1596323 тройства соединен с информационным входом блока памяти констант, выход конечного значения аргумента которого соединен с первым информационным входом, блока. сравнения, выход которого соединен с вхо- 5 дом останова блока синхронизации, вход задания константы два устройства соединен с первым информационным входом первого вычитателя, вход задания константы один устройства соединен с первым ин- 10 формационным входом второго вычитателя, второй информационный вход которого соединен с вторым информационным входом первого вычитателя и с выходом первого блока нормирования, первый информаци- 15 онный вход которого соединен с первым информационным входом второго блока нормирования и с выходом блока формирования коэффициента, информационный вход которого соединен с вторым информа- 20 ционным входом первого блока нормирования, с вторым информационным входом блока сравнения и с выходом накапливающего сумматора, установочный вход которого соединен с входом начального 25 значения аргумента устройства, информационный вход накапливающего сумматора соединен с выходом значения шага аргумента блока памяти констант и с вторым информационным входом второго 30 блока нормирования, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом третьего вычитателя, первый информационный вход ко- 35 торого соединен с выходом первого умножителя, первый информационный вход которого соединен с выходом второго регистра, информационный вход которого соединен с выходом первого шинного 40 коммутатора, первый информационный вход которого соединен с выходом значения функции в нулевой точке блока памяти констант, второй информационный вход первого шинного коммутатора соединен с первым входом второго умножителя и с выходом первого регистра, информационный вход . которого соединен с выходом второго шинного коммутатора, первый информационный вход которого соединен с выходом значения функции в первой точке памяти констант, второй информационный вход второго шинного коммутатора соединен с выходом сумматора и с выходои результата устройства, выход первого вычитателя соединен с вторым информационным входом второго умножителя, выход которого соединен с вторым информационным входом третьего вычитателя, выход второго вычитателя соединен с вторым информационным входом второго умножителя, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока синхронизации соединены соответственно с входом управления блока формирования коэффициента, входами управления первого и второго блоков нормирования, с входами управления первого и второго вычитателей, с входами управления первого и второго умножителей, с входом управления третьего вычитателя, с входом управления первого шинного коммутатора и первым входом первого элемента ИЛИ, с входами управления накапливающего сумматора и второго шинного коммутатора и с первым входом второго элемента ИЛИ, с входом управления блока сравнения, вход управления первого регистра — с выходом второго элемента ИЛИ, второй вход которого соединен с входом "Пуск" устройства и с вторым. входом первого элемента ИЛИ, выход которого соединен с входом управления второго регистра.

1596323

Фиг. 2

1596323

Пуск 21

Ю 0

0) 2

Тг 25 иг. юг.4

1596323

Составитель М. Кауль

Техред M.Mîðãåíòàë Корректор С. Шекмар

Редактор А.Огар

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

Заказ 2910 Тираж 566 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5