Устройство для контроля сумматоров

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике, может быть использовано при проверке многоразрядных арифметических узлов и является усовершенствованием устройства по а.с. N1312575. Цель изобретения - повышение достоверности контроля устройства. Устройство содержит сумматор 3, делитель 4, две группы 5,6 сумматоров по модулю два, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент И 8, регистратор 9 ошибки, в состав которого входят триггеры, формирователь импульсов, элемент И и индикатор ошибки. Кроме того, устройство содержит генератор 10 тактовых импульсов и формирователь импульсов 11. На входы контролируемых сумматоров 1,2 поступают сигналы с прямых и инверсных выходов делителя 4 соответственно. Для повышения достоверности контроля устройства сигналы на вход контролируемого сумматора 2 подаются через сумматоры по модулю два группы 5, а снимаются с его выхода через сумматоры по модулю два группы 6. Выход старшего разряда делителя 4 подключается ко вторым входам сумматоров групп 5 и 6, обеспечивая либо прямую передачу сигнала, либо его инвертирование. Инвертирование входного и выходного сигнала контролируемого сумматора 2 и повышает достоверность контроля. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 11/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Фиг.1

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (61) 1312575 (21) 4430115/24-24 (22) 15.04.88 (46) 30.09.90. Бюл. М 36 (71) Харьковский политехнический институт им. В.И.Ленина (72) А.О.Городкова, О.Г.простаков и А.В.Шкилер (53) 681.3(088.8) (56) Авторское свидетельство СССР

М 1312575, кл. G 06 F 11/00, 1985. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ СУММАТОРО В (57) Изобретение относится к автоматике и вычислительной технике, может быть .использовано при проверке многоразрядных арифметических узлов и является усовершенствованием устройства по а.с.

М1312575. Цель изобретения — повышение достоверности контроля устройства. Устройство содержит сумматор 3, делитель 4, две группы 5, 6 сумматоров по модулю два, „„. Ы„„1596331 А2 элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент

И 8, регистратор 9 ошибки, в состав которого входят триггеры, формирователь импуль-. сов, элемент И и индикатор ошибки. Кроме того, устройство содержит генератор 10 тактовых импульсов и формирователь 11 импульсов, На входы контролируемых сумматоров 1, 2 поступают сигналы с прямых и инверсных выходов делителя 4 соответственно. Для повышения достоверности контроля устройства сигналы на вход конт. ролируемого сумматора 2 подаются через сумматоры по модулю два группы 5, а сни- маются с его выхода через сумматоры по модулю два группы 6. Выход старшего разряда делителя 4 подключается к вторым входам сумматоров групп 5 и 6, обеспечивая либо прямую передачу сигнала, либо его инвертирование. Инвертирование входного и выходного сигналов контролируемого сум-. матора 2 и повышает достоверность контроля. 3 ил.

1596331

Изобретение относится к автоматике и вычислительной технике, может быть использовано при проверке многоразрядных арифметических узлов и является усовершенствованием изобретения по авт,св. М

1312575. Цель изобретения — повышение достоверности контроля устройства.

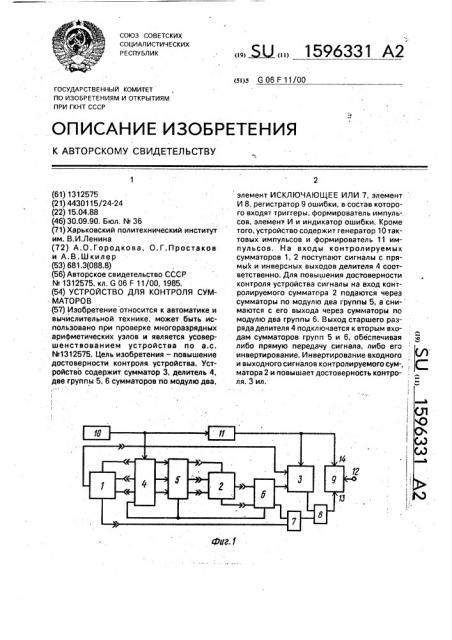

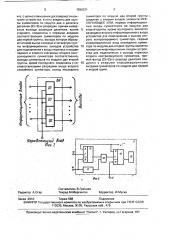

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 и 3 — схемы регистратора ошибки и группы сумматоров по модулю два соответственно, примеры исполнения.

На фиг. 1 обозначены контролируемые сумматоры 1 и 2 (не входят в состав устройства), сумматор 3, делитель 4, группы 5 и 6 сумматоров по модулю два, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7, элемент И 8, регистратор 9 ошибки, генератор 10 тактовых импульсов, формирователь 11 импульсов, установочный вход 12 устройства, а также шины 13 и 14 регистрирующего и читающего сигналов устройства соответственно.

Регистратор 9 ошибки (фиг. 2) содержит триггеры 15 и 16, формирователь 17 импульсов, элемент И 18 и индикатор 19 ошибки.

Каждая из групп 5 и 6 сумматоров по модулю два состоит (фиг. 3) из сумматоров

20 по модулю два, Устройство работает следующим образом.

Контролируемые сумматоры 1 и 2 (празрядные комбинационные) подключают входами к(2п+1) прямым и инверсным выходам делителя 4, обеспечивающего перебор возможных 2(2n+1) комбинаций на выходах этих сумматоров, Первый контролируемый сумматор 1 соединяют с прямыми выходами делителя 4 непосредственно, второй контролируемый сумматор 2 соединяют с.инверсными выходами делителя 4 через сумматоры по модулю два первой группы 5.

По установочному входу 12 устройства происходит выключение индикации ошибки регистратора 9.

Тактовые импульсы с выхода генератора 10 обеспечивают формирование всевозможных комбинаций на выходах делителя 4, . с помощью последнего(2п+2)-го разряда которого происходит изменение режима работы устройства . Группы 5 и 6 сумматоров по модулю два содержат соответственно (2п+1) и (и+1) сумматоров.

При нулевом сигнале на последнем выходе делителя 4 они работают как повторители,.при единичном сигнале — как инверторы.

В первом режиме работы устройства сумматоры по модулю два групп 5 и 6 передают входные сигналы без искажения. В этом случае на выходе результата первого

5 контролируемого сумматора 1 присутствует код, равный сумме кода младшего разряда делителя 4, кода группы младших разрядов делителя 4, начиная с второго, и кода группы старших разрядов делителя 4.

10 На выходе контролируемого сумматора

2 должен быть код, обратный результату на выходе сумматора 1. °

На выходе сумматора 3, складывающего прямой и обратный коды, присутствуют еди15 ничные сигналы во всех разрядах, При добавлении на вход переноса сумматора 3 сигнала с выхода формирователя

11 импульсов, задерживающего тактовый импульс на время срабатывания суммато20 ров 1 — 3, на выходе результата сумматора 3 устанавливается нулевой код и формируется единичный перепад на выходе переноса.

Выходы переноса контролируемых сумматоров 1 и 2 поступают на входы элемента

25 ИСКЛЮЧАЮЩЕЕ ИЛИ 7, на выходе которого при правильной работе сумматоров 1 и 2 устанавливается единичный сигнал, так как на выходах переноса этих сумматоров должны присутствовать противоположные сиг30

55 налы.

Таким образом, на выходе элемента И 8 при появлении единичного перепада на выходе. переноса сумматора 3 устанавливается единичный сигнал, свидетельствующий о нормальной работе устройства, и индикатор

19 ошибки регистратора 9 не включается.

Во втором режиме работы устройства (старший разряд делителя 4 — в единичном состоянии) на вход контролируемого сумматор 2 поступает прямой код с выхода делителя 4 (группа 5 сумматоров по модулю два инвертисует его инверсные выходы) и на выходах обоих сумматоров 1 и 2 присутствуют прямые коды. Но сумматоры группы 6 еще раз инвертируют код на выходе сумматора 2, и на входах сумматора 3 снова присутствуют прямой и обратный коды, как и в первом режиме, Если в сумматорах 1 и 2 происходит ошибка, то единичный сигнал на выходе элемента И 8 не появляется, триггер 15 регистратора 9 не устанавливается в единичное состояние и сигнал с выхода формирователя

11 через формирователь 17 и элемент И 18 устанавливает в единичное состояние триггер 16 регистратора 9, включая индикатор

19 ошибки, Ф-ормула изобретения

Устройство для контроля сумматоров по авт.св. М 1312575, о т л и ч а ю щ е е с я тем, 159б331 что, с целью повышения достоверности контроля устройства, в него введены две группы сумматоров по модулю два и делитель дополнен (2п+2)-м разрядом, причем инвер- . сные выходы разрядов делителя, кроме 5 старшего, соединены с первыми входами соответствующих сумматоров по модулю два первой группы, выходы которых образуют второй выход и вторую и четвертую группы информационных выходов устройства 10 для подключения к входу переноса и входам первого и второго слагаемых второго контролируемого сумматора соответственно, выходы сумматоров по модулю два второй группы, кроме последнего, соединены с со- 15 ответствующими разрядами входа второго слагаемого сумматора, выход последнего

Упра3ляюи ий 5ход

Фиг. 1

Составитель В.Гречнев

Техред М.Моргентал

Корректор И.Муска

Редактор А.Orap

Заказ 2910. Тираж 568 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР, 113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

3

Ь

Ъ сумматора по модулю два второй группы . соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первые информационные входы сумматоров по модулю два второй группы, кроме последнего, являются разрядами второго информационного входа устройства для подключения к выходу второго контролируемого сумматора, первый информационный вход последнего сумматора по модулю два второй группы является четвертым инфомационным входом устройства для подключения к выходу переноса второго контролируемого сумматора, прямой-выход (2п+2 -го разряда делителя соединен с вторыми информационными входами сумматоров по модулю два первой и второй групп.