Устройство для формирования контрольного кода по модулю два

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах сопряжения цифровых вычислительных машин с внешними абонентами. Цель изобретения - повышение быстродействия устройства. Устройство содержит регистр 1, регистр 2 свдига, триггер 3, элементы ИЛИ 4, 5, элементы И 6, 7, блоки 8, 9 приоритета, группу N триггеров 10, группы N И элементов 11-13, группу N ИЛИ элементов 14. Контролируемый код записывается на регистр 1. Первый блок 8 приоритета выделяет крайнюю правую единицу контролируемого кода и с помощью элементов И 12 записывается единица в соответствующий разряд регистра 2 сдвига. Второй блок 9 приоритета выделяет крайнюю левую единицу контролируемого кода и через элементы И 13 устанавливается в единичное состояние соответствующий триггер 10. Начинается продвижение "единицы" по регистру 2 сдвига, сопровождающееся появлением единичных сигналов на нулевых входах триггеров 10. По обнулении соответствующего триггера 10, установленного в единичное состояние элементом И 13, формируется единичный сигнал на выходе 20 устройства, а с выхода 19 устройства снимается контрольный код по модулю два. Количество тактов, необходимое для формирования контрольного кода по модулю два, равно числу разрядов между крайними "единицами" кода. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 06 F 11/10

ГОСУДАРСТВЕН ЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4405260/24.24 (22) 06.04.88 (46) 30.09.90, Бюл, М 36 (72) В.А.Панюшкин, Ю,В.Панюшкин

t и Н.В.Мильчаков (51) 681.3(088. 8) (56) Авторское свидетельство СССР

N 553300333322,, к лп, G 06 F 11/10, 1975.

Авторское свидетельство СССР

М 1310824, кл. G 06 F 11/10, 1986. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

КОНТРОЛЬНОГО КОДА ПО МОДУЛЮ ДВА (57) Изобретение относится к автоматике и . вычислительной технике и может быть использовано в устройствах сопряжения цифровых вычислительных машин с внешними абонентами. Цель изобретения — повышение быстродействия устройства. Устройство содержит регистр 1, регистр 2 сдвига, триггер 3, элементы ИЛИ 4, 5, элементы И 6, 7, блоки 8, 9 приоритета, группу п триггеров

10, группы п элементов И 11-13, группу и

„„Ы „„159á335 А1 элементов ИЛИ 74, Контролируемый код записывается на регистр 1. Первый блок 8 приоритета выделяет крайнюю правую единицу контролируемого кода, и с помощью элементов И 12 записывается единица в соответствующий разряд регистра 2 сдвига.

Второй блок 9 приоритета выделяет крайнюю левую единицу контролируемого кода, и через элементы И 13 устанавливается в единичное состояние соответствующий триггер 10, Начинается продвижение единицы по регистру 2 сдвига, сопровождающееся появлением единичных сигналов.на нулевых входах триггеров 10. По обнулении соответствующего триггера 10, установленного в единичное состояние элементом И )

13, формируется единичный сигнал на выходе 20 устройства. а с выхода 19 устройства снимается контрольный код по модулю два.

Количество тактов, необходимое для формирования контрольного кода по модулю два, равно числу разрядов между крайними единицами када. 1 ил, 1596335 состоянии любого из триггеров 10 группы. разрешает прохождение тактовых импуль- 40 сов с входа 17 через первый элемент И 6 на

50

Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах сопряжения циф- ровых вычислительных машин с внешними абонентами.

Цель изобретения — повышение быстродействия устройства;

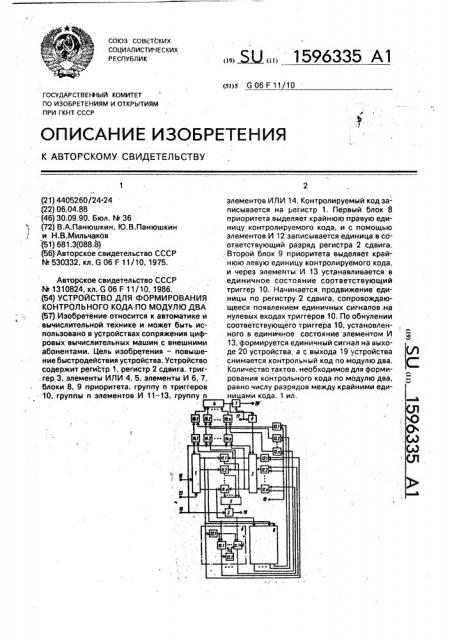

На чертеже приведена функциональная схема устройства.

На схеме обозначены регистр 1, регистр

2 сдвига, триггер 3, элементы ИЛИ 4 и 5; элементы И 6 и 7, блоки 8 и 9 приоритета, группа триггеров 10, группы элементов И

11 — 13, группа элементов ИЛИ 14, информационный вход 15 устройства, установочный вход 16 устройства, тактовый вход l7 устройства, вход"18 запуска устройства, выход

19 контрольного кода устройства, выход 20 окончания формирования контрольного кода устройства, группы элементов И 21 блоков 8 и 9 приоритета, группы элементов НЕ

22 блоков 8 и 9 приоритета и вход 23 записи контролируемого кода устройства.

Регистр 1 обеспечивает хранение контролируемого и-разрядного кода, принимаемого в устройство по входу 15.

Блок 8 приоритета предназначен для выделения крайней слева единицы е слове, хранящемся в регистре 1, и ее пересылку через вторую группу элементов И 12 в соответствующий разряд регистра 2 сдвига.

Блок 9 приоритета служит для выделения крайней справа единицы в слове, хранящемся в регистре 1, и ее пересылку через третью группу элементов И 13 в соответствующий триггер 10 группы.

Первый элемент ИЛИ 4 при единичном тактовый вход регистра 2 сдвига; э при их нулевом состоянии разрешает прохождение через второй элемент И 7 на выход 20 сигнала окончания формирования контрольного кода.

Регистр 2 сдвига обеспечивает сдвиг единицы от разряда, в котором записана первая слева единица в регистре 1, до разряда, в котором в регистре 1 записана последняя справа единица. При сдвиге единицы сигналы с выходов регистра 2 сдвига через элементы ИЛИ 14 группы последовательно подаются на входы установки в "0" триггеров 10 группы.

Первая группа элементов И 11 служит для формирования единичных сигналов через второй элемент ИЛИ 5 на счетный вход триггера 3 при совпадении единичных кодов в одноименных разрядах регистра 1 и

35 регистра 2 сдвига в процессе сдвига единичного кода в регистре 2 сдвига.

При подаче сигнала на вход 16 обеспечивается приведение в исходное состояние триггеров 10 группы, регистров 1 и 2 и триггера 3.

Сигнал на входе 18 разрешает пересылку единицы из блока 8 приоритета в регистр

2 сдвига и единицы из блока 9 приоритета на единичный вход соответствующего триггера 10 группы. По окончании работы устройства на выходе 19 формируется контрольный код.

Устройство работает следующим образом.

По сигналу начальной установки на входе 16 устройства происходит обнуление регистра 1, регистра 2 сдвига, триггера 3 и триггеров 10 группы. По сигналу на входе 23 записи контролируемого кода устройства в регистр 1 через информационный вход 15 устройства записывается контролируемый код. Блок 8 приоритета определяет самую левую единицу в контролируемом коде, а блок 9 приоритета — самую правую единицу.

Блоки 8 и 9 приоритета работают одинаково.

Рассмотрим выделение самой левой единицы. Если единица находится в самом левом разряде, то она проходит на выход блока 8 приоритета и через первый элемент .

НЕ 22.1 на вторые входы всех элементов И

21, блокируя прохождение через них на выход блока 8 приоритета других единиц. Если в,первом разряде записан нуль, то он, пройдя через элемент НЕ 22,1, разрешает прохождение единицы через первый элемент И

21;1 при наличии единицы нэ его первом входе. Сигнал с выхода первого элемента И

21.1, пройдя через второй элемент НЕ 22,2, закрывает все оставшиеся элементы И 21 (21.2 — 21.(n — 1))и т,д. Таким образом. на выход блока 8 приоритета проходит единица первого слева, отличного от нуля разряда.

По сигналу запуска, подаваемому по входу 18 устройства, единица с одного из выходов блока 8 приоритета записывается через соответствующий элемент И 12 второй группы в регистр 2 сдвига, а единица с одного из выходов блока 9 приоритета через соответствующий элемент И 13 третьей группы устанавливает триггер 10 группы,. соответствующий разряду контролируемого кода, в котором записана последняя справа единица, в единичное состояние. При этом выходным сигналом этого триггера через первый элемент ИЛИ 4 открывается первый элемент И б и сигналы тактовой частоты с входа 17 устройства поступают нэ тактовый вход регистра 2 сдвига. Сдвиг единицы в

1596335

Составитель В.Гречнев

Техред М.Моргентал КорректорС.Шекмар

Редактор А.Огар

Заказ 2910 Тираж 568 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб„4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 регистре 2 сдвига происходит до тех пор, пока выходным сигналом с соответствующего разряда регистра 2 с сдвига не будет установлен через элемент ИЛИ 14 группы в. нулевоесостояние триггер, находившийся в 5 единичном состоянии. При этом на выходе элемента ИЛИ 4 устанавливается нулевое значение сигнала, которое запрещает прохождение тактовых сигналов через элемент

И 6 с тактового входа 17 устройства. Одно- 10 временно открывается элемент И 7 и на выходе 20 устройства появляется сигнал окончания формирования контрольного кода. Устройство готово к приему следующего кода. 15

В формировании контрольного кода на выходе 19 принимает участие в процессе сдвига единицы в регистре 2 сдвига первая группа элементов И 11, каждый из которых сравнивает содержимое одноименных раз- 20 рядов регистра 1 и регистра 2 сдвига. При наличии единиц в одноименных разрядах через элемент ИЛИ 5 на счетный вход триггера 3 подается управляющий сигнал, переводящий триггер 3 в противоположное 25 состояние. После окончания сдвига единицы в регистре 2 сдвига триггер 3 содержит контрольный код, который выдается на выход 19 устройства.

Таким образом, предлагаемое устрой- 30 ство обеспечивает формирование контрол ьного кода без пересылки контролируемого кода в регистр сдвига.

Формула изобретения

Устройство для формирования конт- 35 рольного кода по модулю два, содержащее регистр, регистр сдвига, двафлока приоритета, два элемента И, два элемента ИЛИ и триггер, причем первый вход первого элемента И и прямой вход второго элемента И 40 подключены к тактовому входу устройства, выход первого элемента ИЛИ соединен с вторым входом первого элемента И и с инверсным входом второго элемента И. выход которого является выходом окончания фор- 45 мирования контрольного кода устройства, .; выход первого элемента И соединен с тактовым входом ре-истра сдвига, установочные входы регистра, регистра сдвига и нулевой вход триггера подключены к установочному входу устройства, выход триггера является выходом контрольного кода устройства, информационный вход регистра является информационным входом устройства, тактовый вход регистра является. входом записи контролируемого кода устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены группа триггеров, три групйы элементов И и группа элементов

ИЛИ, причем выходы регистра соединены с первыми входами соответствующих элементов И первой группы и соответствующими информационными входами первого и второго блоков приоритета, выходы первого блока приоритета соединены с первыми входами соответствующих элементов И второй группы,. выходы которых соединены с соответствующими информационными входами регистра сдвига, выходы которого соединены с вторыми входами соответствующих элементов И первой группы и первыми входами соответствующих элементов ИЛИ группы, вторые входы которых подключены к установочному входу устройства, выходы элементов И первой . группы соединены с входами второго элемента ИЛИ, выход которого соединен со счетным входом триггера, выходы элементов ИЛИ группы соединены с нулевыми входами соответствующих триггеров группы, прямые выходы которых соединены с соответствующими входами первого элемента

ИЛИ, выход второго блока приоритета соединены с первыми входами соответствующих элементов И третьей группы, выходы которых соединены с единичными входами соответствующих триггеров группы, вторые входы элементов И второй и третьей групп подключены к входу запуска устройства.