Устройство для тестового контроля временных соотношений

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики цифровых схем. Целью изобретения является повышение достоверности контроля. С этой целью в устройство, содержащее блок памяти тестов, счетчик адреса, группу из N ключей, блок сравнения, блок индикации, элемент ИЛИ и генератор тактовых импульсов, введены регистр выдачи тестов, регистр результата, блок синхронизации, таймер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. 5 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю 6 06 F 11/22

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4347409/24-24 (22) 22.12.87 (46) 30.09.90. Бюл. ¹ 36 (72) Ю.Т.Галиев, Ю.М.Далецкий, В.И,Ким, В.В.Кирпиченко и А.Я,Прохоренко (53) 681.3(088.8) (56) Авторское свидетельство СССР № 1269141, кл. G 06 F 11/22, 1985.

Авторское свидетельство СССР № 1260962, кл, G 06 F11/22,,1985. (54) УСТРОЙСТВО ДЛЯ ТЕСТОВОГО КОНТРОЛЯ ВРЕМЕННЫХ СООТНОШЕНИЙ

Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики цифровых схем.

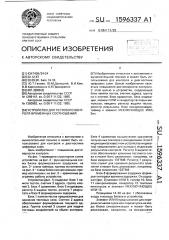

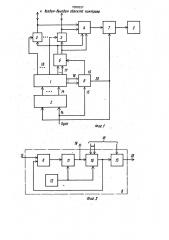

Цель изобретения — повышение достоверности контроля, На фиг. 1 приведена структурная схема устройства; на фиг. 2 — функциональная схема блока формирования задержки; на фиг. 3 — схема таймера, пример исполнения; на фиг. 4- схема блока синхронизации, пример исполнения; на фиг. 5 — временные диаграммы работы устройства.

Устройство (фиг. 1) содержит блоМ 1 памяти тестов, счетчик 2 адреса, группу ключей 3, блок 4 сравнения, блок 5 индикации, регистр 6 выдачи тестов, регистр 7 результата и блок 8 формирования задержки.

Блок 1 памяти тестов предназначен для хранения тестовых слов, Счетчик 2 адреса обеспечивает формирование текущего ад-. реса. Группа ключей 3 служит для подачи тестовых воздействий на объект контроля, „„ Ы „„1596337 А1 (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики цифровых схем, Целью изобретения являеться повышение достоверности контроля, С этой целью в устройство, содержащее блок памяти тестов, счетчик адреса, группу из и ключей, блок сравнения, блок индикации, элемент ИЛИ и генератор тактовых импульсов, введены регистр выдачи тестов, регистр результата, блок синхронизации, таймер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ.

5ил.

Блок 4 сравнения осуществляет сраэнение полученных откликов с ожидаемыми, Блок 5 индикации (в известном устройстве индикатор) предназначен для вывода и индикации результатов контроля. Регистр 6 выдачи тестов обеспечивает хранение тестового слова и может быть реализован, например, на базе микросхем 133ТМ8. Регистр 7 результата служит для хранения результата сравнения и может быть реализован, например, на базе микросхем 133ТМ8.

Блок 8 формирования задержки формирует интервал времени задержки. Он содержит (фиг. 2) элемент ИЛИ 9, таймер 10, блок

11 синхронизации, генератор 12 тактовых

: импульсов и элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 13.

Позициями 14 — 20 на фиг, 1 обозначены. входы и.выходы блоков и устройства.

Элемент ИЛИ 9 предназначен для передачи сигналов пуска или перезапуска на входы блока синхронизации и может быть реализован, например, на микросхеме

1596337

20

30

40

45 тервалов до половины периода тактовой частоты

Х200 1 1

133ЛЛ1, Таймер 10(формирователь временных интервалов) служит для формирования заданного интервала времени, кратного-периоду тактовых импульсов, и может быть реализован, например, на микросхемах серии 133. Таймер 10 (фиг. 3) образуют триггер

21, элемент И 22 и счетчик 23.

Блок 11 синхронизации предназначен для формирования импульсов записи и может быть реализован, например, на микросхемах серии 133. Согласно фиг. 4 блок 11 выполнен на триггере 24 и элементе И 25.

Генератор 12 тактовых импульсов генерирует импульсы тактовой частоты и может быть реализован, например, на-микросхемах 533ГГ1. Элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 13 служит для работы в качестве управляемого инвертора и может быть реализован, например, на микросхеме 133ЛП5. Устройство работает следующим образом.

Сигналом "Пуск", который поступает на вход 14 счетчика 2 адреса и на вход 15 блока

8, в счетчик 2 адреса заносится адрес перcoro тестового слова и запускается блок 8.

При этом с выхода счетчика 2 адреса на вход блока 1 памяти тестов поступает адрес первого тестового слова и блок 1 выдает первое тестовое слово, которое состоит из трех частей. Каждая часть тестового слова выдается на соответствующий выход блока 1, Выходы 16 блока 1 управляют работой ключей 3. Ключи 3, которые открываются сигналами с группы выходов 16, пропускают через себя сигналы воздействий, подаваемые на объект контроля. На выходах 17 группы формируются сигналы воздействий и сигналы ожидаемого отклика, а на выходах 18 — код времени задержки. Кроме того, блок 8 через заданный интервал времени (определяемый временем задержки в счетчике 2 адреса и временем выборки иэ блока

1 памяти) на выходе 19 формирует сигнал записи в регистр 6, который формируется по переднему фронту тактового импульса, поступающего с выхода генератора 12, По сигналу записи в регистр 6 с выходов

17 блока 1 памяти тестов записываются сигналы воздействий, которые через ключи 3 поступают на объект контроля, а сигналы 5 отклика поступают на вход блока 4 сравнения. На выходе 20 блока 8 через интервал времени(относительно сигнала записи в регистр 6), определяемый кодом задержки, формируется сигнал записи в регистр 7 ре- 5 зультата. По сигналу записи в регистр 7 с выхода блока 4 сравнения записывается результат сравнения, Этот же сигнал подается на счетный вход счетчика 2, в котором по нему формируется адрес следующего тесто-. ваго слова, Результат сравнения с выхода регистра 7 результата поступает на вход блока 5 индикации. По адресу следующего тестового слова на выходе блока 1 памяти тестов формируется следующее тестовое слово.

Блок 8 формирования задержки работа-. ет следующим образом, Сигнал, пришедший на первый или второй вход элемента

ИЛИ 9, через этот элемент поступает на вход пуска блока 11 синхронизации. На синхровход блока 11 синхронизации поступают тактовые импульсы с генератора 12 тактовых импульсов. Блок 11 синхронизации по переднему фронту импульса после фиксации поступления на его вход сигнала пуска формирует сигнал записи в регистр 6. По этому же сигналу в таймер 10 записываются старшие разряды кода интервала времени задержки. Старшие разряды кода интервала времени задержки соответствуют числу периодов тактовых импульсов генератора

12.

Через время, определяемое старшими разрядами кода времени задержки относительно сигнала записи в регистр 6, на выходе таймера 10 формируется сигнал переноса, который поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и на второй вход элемента ИЛИ 9. На второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 поступает младший разряд кода интервала времени задержки, В случае равенства его

"0" на выходе элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ 13 формируется прямой сигнал переноса и фиксация момента сравнения (т.е.. запись в регистр 7 результата) происходит по его переднему фронту, а в случае равенства его "1" на выходе элемента ИСКЛЮЧАЮТЫ ЕЕ ИЛИ 13 формируется инверсный сигнал переноса и фиксация момента сравнения (т.е, запись в регистр 7) происходит по его заднему фронту, что позволяет уменьшить дискрет задаваемых временных инВ таблице приведен пример, иллюстрирующий работу устройства в режиме проверки логического элемента 2И вЂ” НЕ, а на фиг. 5 — временные диаграммы, поясняющие принцип работы устройства.

Таблица истинности работы элемента

2И вЂ” НЕ имеет вид

Х10110

У1101

Предположим, что входы Х1 и Х2 подключены,соответственно к контактам 1 и 2 (первый и второй ключи устройства), а выход

Y — к контакту 3 (третий ключ устройства).

1596337

Кон.|акт 4 и последующие не используются.

Под циклом будем понимать одну элементарную проверку (один импульс на счетном входе счетчика 2 в цикле контроля).

Полную проверку элемента 2И-НЕ на 5 функционирование можно провести за четыре цикла.

При поступлении сигнала "Пуск" через время т (время задержки на счетчике 2 и время выборки из блока 1 памяти) на выходах 16 — 18 блока 1 памяти появляется тестовое сло о (фиг. 5, момент времени t1). При этом код маски на выходе 16 блока 1 открывает все ключи, кроме третьего (строка 3 таблицы). При поступлении тактового импульса с генератора 12 блок 8 формирует импульс записи в регистр 6 и первый набор тестовой информации поступает через открытые ключи 3 на объект контроля, .а эталон ожидаемого отклика поступает на соответствующий разряд первого входа блока 4 сравнения. B то же время в таймер

10 записывается код задержки, который в данном примере постоянен (строки 9 — 11 таблицы). Переход из одного состояния в другое должен происходить не более чем через время, равное т,д (время задержки на логическом элементе). Время т,д задается кодом на выходе 18 блока 1 памяти. В циклах 1 и 2 (см. таблицу) выход логического элемента не переключается, проверка на допустимое время переключения осуществляется в циклах 3 и 4, В, цикле 3 на входы логического элемента подаются две единицы (следовательно, выход элемента через время г д, заданное кодом на выходе 18 блока 1, должен переключиться в "0"), В таблице (строка 19) для исправного элемента показано, что в момент выдачи воздействия на объект контроля (с2) выход его не переключился, а через время тэд (с3) уже переключился. Происходит сравнение отклика (строка 19) с ожидаемым результатом (строка 7), следовательно, в регистр 7 результата 45 записывается ноль. Для неисправного объекта контроля (строки 23 — 25), у которого время переключения превышает г;д, такого сравнения не |роисходит, и B регистр 7 результата записывается единица в том раз- 50 ряде, где сравнения не произошло. В .строках 20 — 22 таблицы показано содержимое регистра 7 результата при проверке исправного элемента, а в строках 26 — 28 — при: проверке неисправного элемента.

Формула изобретения

Устройство для тестового контроля временных соотношений, содержащее блок памяти тестов, счетчик адреса, группу из и ключей, блок сравнения, блок индикации, элемент ИЛИ и генератор тактовых импульсов, причем установочный вход счетчика адреса и первый вход элемента ИЛИ соединены с входом начальной установки устройства, выход счетчика адреса подключен к адресному входу блока памяти тестов, i-й разряд первого информационного выхода которого (1 < i < и) соединен с управляющим входом i-го ключа группы, выход которого и i-й разряд первого входа блока сравнения образуют i-й вход-выход устройства для подключения к i-му входу-выходу объекта контроля, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, оно содержит регистр выдачи тестов, регистр результата, блок синхронизации, таймер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к синхровходу регистра результата и счетному входу счетчика адреса, синхровход и i-й разряд информационного входа регистра выдачи тестов соединены соответственно с выходом блока синхронизации и i-м разрядом второго информационного выхода блока памяти тестов, l-й разряд выхода регистра выдачи тестов подключен к информационному входу i-го ключа группы и i-му разряду второго входа блока сравнения, информационный вход и выход регистра результата соединены соответственно с выходом блока сравне-. ния и входом блока индикации, выход генератора тактовых импульсов подключен к синхровходам блока синхронизации и таймера, второй вход и выход элемента ИЛИ соединены соответственно с выходом таймера и входом пуска блока синхронизации, выход которого подключен к входу управления записью таймера, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом таймера, а второй вход элемента

ИСКЛЮЧАЮЩЕЕ ИЛИ и вход начальной установки таймера подключены к третьему информационному выходу блока памяти тестов.

1596337

1596337

1596337

М

Составитель Г. Виталиев

Техред М.Моргентал

Редактор А. Огар

Корректор Т.Палий

Заказ 2910 Тираж 570 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035. Москва, Ж-35, Раушская наб.. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Фю Ъ Д

Фф в

Ъ, Ф д < :з ь4

Q, М. фк р

cs к и с @ фэ

0а и +