Дешифратор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к дешифраторам для микросхем памяти с резервированием. Цель изобретения - упрощение дешифратора - достигается тем, что дешифратор содержит мажоритарный элемент 3, инвертор 5 и в каждой логической ячейке 4 - первый 9 и второй 10 формирователи записи и развязывающие элементы 7 и 8 с соответствующими связями. Это позволяет подавать напряжение пережигания раздельно на плавкие перемычки 6, соответствующие "нулям" и "единицам". В результате упрощаются инверторы 1,2 и отпадает необходимость подачи на адресные входы специальных управляющих сигналов повышенного уровня. 1 ил.

. СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)5 G 11 С 11/40

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ, ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР <

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4602744/24-24 (22) 09.11.88 (46) 30,09.90. Бюл. ¹ 36 (72) С,А.Королев и С.А.Фастов (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

¹ 11339999881166, кл. G 11 С 11/40, 1986, Патент США ¹ 4250570, кл. 365-200, опублик. 1981.

„„. Ж„„1596393 А1 (54) ДЕШИФРАТОР (57) Изобретение относится к вычислительной технике, а именно к дешифраторам для микросхем памяти с резервированием.

Цель изобретения — упрощение дешифратора — достигается тем, что дешифратор содержит мажоритарный элемент 3, инвертор

5 и в каждой логической ячейке 4 — первый

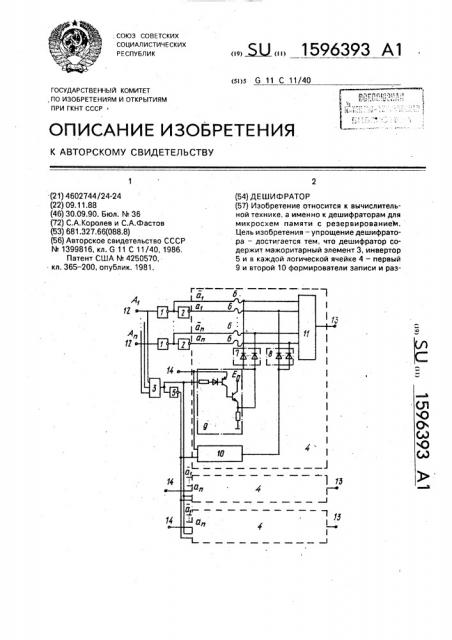

9 и второй 10 формирователи записи и раэ1596393 вяз ывающие элементы 7 и 8 с соответствующими связями. Это позволяет подавать напряжение пережигания раздельно на плавкие перемычки 6, соответствующие "нулям" и "едиИзобретение относится к вычислительной технике и может быть использовано при проектировании дешифраторов .для микросхем памяти с резервированием, Цель изобретения — упрощение дешифратора, На чертеже приведена схема дешифратора.

Дешифратор содержит инверторы первой 1 и второй 2 групп, мажоритарный элемент 3, логические ячейки 4, инвертор 5, Каждая логическая ячейка 4 состоит из элементов памяти на плавких перемычках 6, развязывающих элементов первой 7 и второй 8 групп, первого 9 и второго 10 формирователей записи, элемента И 11.

На чертеже показаны также адресные входы 12, выходы 13 и входы 14 разрешения записи дешифратора.

Предлагаемый дешифратор является резервным дешифратором микросхемы памяти и предназначен для выборки из резервного накопителя строк или столбцов.

Основной дешифратор (не показан) состоит из логических ячеек на элементах И, входы которых соединены с выходами соответствующих инверторов 1 и 2, а выходы подключены, например, к адресным шинам основного накопителя (не показан). При появлении на адресных входах микросхемы памяти в рабочем режиме адреса, по которому в основном накопителе или основном дешифраторе имеется неисправность, не приводящая к постоянной выборке соответствующего выхода основного дешифратора, основной дешифратор должен блокироваться, а в резервном накопителе резервным дешифратором должна быть проведена выборка. Какой из логических элементов 4 резервного дешифратора сработает определяется запрограммированными перемычками 6. Блокировка основного дешифратора может быть проведена так же, как в прототипе, Дешифратор может быть использован прежде всего для борьбы с дефектами, выявленными в процессе изготовления микросхемы памяти, Однако при наличии у пользователя средств программирования резервного дешифратора и оставшихся неиспользованными логических ячеек 4 после ницам". В результате упрощаются инверторы 1, 2 и отпадает необходимость подачи на адресные вх ды специальных управляющих сигналов повышенного уровня. 1 ил. устранения технологических дефектоЪ можно заменить неисправные строки (столбцы) на резервные и в процессе эксплуатации.

Для установления соответствия между

5 адресом неисправной строки основното накопителя и выбранной резервной строкой в соответствующую логическую ячейку 4 дешифратора необходимо записать адрес неисправной строки основного накопителя

10 путем пережигания плавких перемычек 6, В режиме пережигания перемычек 6 на вход

11 соответствующей ячейки 4 подается высокий уровень напряжения. Перемычки 6 пережигаются большим током, поэтому в

15 каждый момент времени может пережигаться только одна из них. Пережигание перемычек 6 каждой ячейки 4 производится пОследовательно, например, начиная с раз- . ряда А1 адреса и кончая разрядом An, Для

20 определенности рассмотрим работу устройства при пережигании перемычки 6, соответствующей разряду AI. В этом случае на адресный вход А подается логический сигнал, соответствующий значению i-ro разря25- да "адреса. На все остальные входы, кроме

I-го, подаются сигналы, инверсные сигналу на входе Ai, При этом на входе мажоритарного элемента 3 оказывается большинство сигналов, инверсных сигналу Аь поэтому на

30 его выходе будет сигнал А, а на выходе инвертора 5 — Аь Эти сигналы через соответствующие формирователи 9 и 10 записи и развязывающие элементы 7 и 8 поступают на первые входы соответствующих плавких

35 перемычек 6. В результате на обоих выводах перемычек 6 всех разрядов, кроме i-ro, оказывается одинаковый потенциал, поэтому в данный момент времени они не пережжены.

На две перемычки 6 I-го разряда подано

40 напряжение. Однако та из перемычек 6 I-го разряда, на которую с инвертора 1 или 2 подан высокий потенциал, не перегорает, так как закрывается связанный с ней диод соответствующего развязывающего эле45 мента 7 или 8. Вторая из перемычек 6 I-го разряда перегорает, что и свидетельствует о значении I-ro разряда, записываемого в данную ячейку 4 адреса.

После программирования (в рабочем

50 режиме) на входы 14 всех ячеек 4 подается низкий уровень напряжения, отключающий

1596393

Составитель А.Дерюгин

Редактор Н,Киштулинец Техред М.Моргентал Корректор М.Самборская

Заказ 2913 Тираж 487 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 формирователи 9 и 10 записи, которые в рабочем режиме на функционирование дешифратора не влияют. В результате программирования входы элемента И 11 с помощью непережженных перемычек 6 оказываются подключенными к выходам инверторов 1 и 2 в соответствии с тем адресом, по которому данная ячейка 4 дешифратора срабатывает, При появлении на адресных входах адреса, записанного в данной ячейке 4, на всех входах элемента И 11 оказываются "1".

Сигнал "1" на выходе данного разряда дешифратора является сигналом выборки данной строки резервного накопителя (не показан).

Формула изобретения

Дешифратор, содержащий первую и вторую группы инверторов, причем входы инверторов первой группы являются соответствующими адресными входами дешифратора, а выходы соединены с входами соответствующих инверторов второй группы, логические ячейки, каждая из которых состоит из элемента И, элементов памяти на плавких перемычках, развязывающих элементов первой и второй групп, первого формирователя записи, вход выборки которого является соответствующим входом разрешения записи дешифратора, а выход соединен с входами развязывающих элементов первой группы, выходы которых соединены с входами элемента И первой группы, входы

5 второй группы которого соединены с выходами развязывающих элементов второй группы, первые выводы плавких перемычек элементов памяти соединены с выходами инверторов первой и второй групп, а вторые

10 выводы — с входами элемента И соответствующих групп, выход элемента И является соответствующим выходом дешифратора, отличающийся тем, что, с целью упрощения дешифратора, он содержит ма15 жоритарный элемент, инвертор, а каждая логическая ячейка — второй формирователь записи, вход выборки которого соединен с входом выборки первого формирователя записи, а выход — с входами развязывающих

20 элементов второй группы, информационные входы первого и второго формирователей записи каждой логической ячейки соединены соответственно с выходами мажоритарного элемента и инвертора, вход

25 которого соединен с выходом мажоритарного элемента, входы которого соединены с входами первого, второго и третьего инверторов первой группы.