Ячейка регистра сдвига

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении регистров сдвига. Цель изобретения - сокращение аппаратурных затрат и снижение потребляемой мощности. Поставленная цель достигается за счет параллельной загрузки новой информации во все разряды регистра сдвига с одновременным стиранием старой информации без увеличения потребляемой мощности. При работе ячейки в составе регистра сдвига на входы 15, 17, 18, 21 подаются соответствующие опорные потенциалы, на входы 16 и 22 - сигналы синхронизации соответственно сдвига и загрузки, на вход 20 - сигнал загружаемой информации, на вход 19 - информация с выхода 24 предыдущего разряда регистра, с выхода 23 информация поступает на внешние устройства. Выход 24 подключается ко входу 19 следующего разряда или (если данная ячейка является замыкающей в регистре) к шине 13. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУ6ЛИН (51)5 С 11 С 19/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К Д ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

ПО И306РЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4496643/24-24 (22) 19.10.88 (46) 30.09.90. 6юл. М - 36 (71) Московский физико-технический институт (72) А.И.Малинин, А.П. Коваленко и И,Ю.Щетинин (53) 681.327.66 (088.8) (56) Макаев Е.И. Основы радиоэлектроники, M. Радио и связь, 1985,, с. 365-372.

Заявка ФРГ М - 2113727, кл. G 11 С,,19/28, 1978. (54) ЯЧЕЙКА РЕГИСТРА СДВИГА (57) Изобретение относится к вычислительной технике и может быть использовано при построении регистров сдвига.Цель изобретения — сокращение апнаратурных затрат и снижение потреб„„80„„1596394 А 1

2 ляемой мощности. Поставленная цель достигается за счет параллельной загрузки новой информации во все разряды регистра. сдвига с одновременным стиранием старой информации беэ увеличения потреблямой мощности, При работе ячейки в составе регистра сдвига на входы 15, !7, 18 и 21 подаются соответствующие опорные потенциалы, на входы 16 и 22 — сигналы синхронизации соответственно сдвига и загрузки, на вкод 20 — сигнал загружаемой информации, на вход 19 информация с выхода 24 предыдущего разряда регистра, е выхода 23 информация поступаетна внешние устройства.

Выход 24 подключается к входу 19 следующего разряда или (если данная ячейка является замыкающей в регистре) к шине 13. 1 ил.

1596394

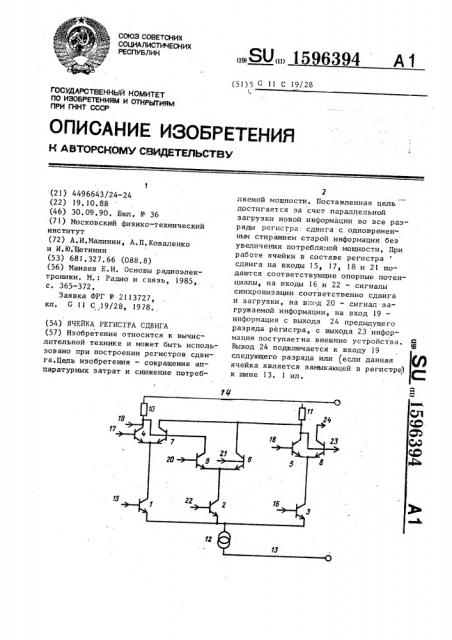

Изобретение относится к вычислительной технике и может быть использовано при построении регистров сдвига, Цель изобретения - сокращение аппаратурных затрат и снижение потребляемой мощности, На чертеже представлена схема ячейки.

Ячейка содержит выполненные на и-р-и транзисторах первый 1, второй

2 и третий 3 ключевые элементы, первый 4, второй 5 и третий 6 опорные элементы, первый 7, второй 8 и третий 9 переключательные элементы, первый 10 и второй 11 элементы смещения на резисторах, источник 12 тока, первая 13 и вторая 14 шины питания ячейки, информационные входы 15-22 ячейки, информационные вьпсоды 23 и

24 ячейки. Вход 19 подключен к выходу 24 ячейки предыдущего разряда, выход 24 подключен . к входу 19 ячейки следующего разряда. С выхода 23 25 снимается сигнал для подачи на внешние устройства.

Работа происходит следующим образом.

На шины 13 и 14 поданы низкий и

sbv окий потенциалы питания U и U, на входы 15, li 18 и 21 поданы опорные потенциалы U, Ulg, Б1б, такие, что Бц (Ц (П (Б, 35

Б!5(U21 (Бч что необходимо для работоспособности ячейки. На вход 16 подается сигнал синхронизации сдвига, на вход 22-сигнал синхронизации загрузки, на вход 20 — потенциал загружаемого сигнала.

В режиме сдвига ячейка работает следующим образом.

На вход 22 подается низкий уро-..

4 вень U сигнала синхронизации за22. „..р рузки, TaKoH,что U (. U15, а на

22 вход 16 подается сигнал синхронизации сдвига, при этом высокий и низ-! .D кий уровни 146 и L< этого сигнала ,о должны удовлетворять условию U< (1

16

Когда на входе 16 низкий уровень, открыт элемент 1 и первая ячейка памяти на элементах 4 и 7 хранит

55 некоторую информацию, для чего необходимо, чтобы П .И вЂ” Щ „о(U<>, где I — ток источника 12 тока;

R lр — сопротивление элемента 10, При этом коллекторный ток элемента 7 загружает через элемент 11 ETO чую ячейку памяти на элементах 5 и 8.

При смене потенциала на входе 16 на открывается элемент 3, информация захватывается второй ячейкой памяти, для чего необходимо, чтобы

U yq — iR ) < U t8, где I - ток источника 12 тока;

R<< — сопротивление элемента 11.

В это время коллекторным током элемента 8 через выход 24 информация поступает на вход 19 ЯРС следующего разряда регистра, а через вход 19 первая ячейка памяти данной ЯРС загружается новой информациеч от ЯРС предыдущего разряда регистра. При подаче на вход 16 U 6 новая информа )) ция захватывается первой ячейкой памяти и цикл повторяется. Если ЯРС является замыкающей в регистре, то ее выход 24 подключается к шине 13.

В режиме загрузки на вход 16 по9 дан U<, на вход 22 подается потенf циал 1122 такой, что

Ч,5-(1 22

В этом случае открыт элемент 2 и в зависимости от потенциала U, или

1),2р на входе 20, таких что ,о

02р<Пг„(U2o ток протекает через элемент 9 либо 6.

По окончании загрузки на вход 22 подается U информация в ЯРС поддерживается первой ячейкой памяти.

Ф.о р м у л а и з о б р е т е н и я

Ячейка регистра сдвига, содержа) щая выполненные на транзис горах первый, второй и третий ключевые элементы, первый и второй опорные элементы, первый и второй переключательные элементы, первый и второй элементы смещения на резисторах, источник тока, выход которого подключен к эмиттерам транзисторов первого и третьего ключевых элементов, вход источника тока подключен к первой шине питания ячейки, коллектор транзистора первого ключевого элемента подключен к эмиттерам транзисторов первых опорного и переключательного элементов, коллекторы которых подключены соответственно к первым выводам резисторов первого и второгб элементов смещения, вторые выводы которых подключены к второй шине питания ячейки, коллектор транзисСоставитель А. Ершова

Редактор М,Недолуженко Техред Л.Олийнык Корректрр И.Муска

Тираж 486

Подписное

Заказ 3902

ВНИИПИ Государственного комитета по изобретениям и открытиям при i ééÒ СССР

113035, Москва, Ж-35, Раушская наб. ° д. 4/5

Лроиэводственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

Ъ .

5 159 тора второго ключевого элемента подключен к эмиттерам транзисторов вторых опорного и переключательного элементов, коллектор транзистора второго опорного элемента подключен к первому выводу резистора второго элемента смещения и базе транзистора второго переключательного элемента и является первым информационным выходом ячейки, коллектор транзистора второго переключательного элемента является вторым информационным выходом ячейки, база транзисторов первого и третьего ключевых, первого и второго опорных и коллектор транзистора первого опорного элементов являются соответственно первым, вторым, третьим, четвертым и пятым информационными входами ячейки, о т л и ч а ю q а я с я тем, что, 6394 6 с целью упрощения и сохранения по,требляемой мощности ячейки, в нее введены третьй опорный и переклю чательный элементы на транзисторах, эмиттеры которых подключены к коллектору транзистора второго ключевого элемента, эмиттер которого подключен к выходу источника тока, база

10 Ъранз ;стора первого и коллектор транзистора третьего переключательных элементов подключены к пятому информационнрму входу ячейки, коллектор транзистора второго и коллектор транзистора третьего опорных элементов объединены, базы транзисторов третьих переключательиого и опорного и второго ключевого элементов являются соответственна шестым, седьмым и восьмым ин20 формационными входами ячейки.