Устройство тактовой синхронизации псевдослучайных последовательностей

Иллюстрации

Показать всеРеферат

Изобретение относится к технике электросвязи. Цель изобретения - повышение точности синхронизации. Устройство тактовой синхронизации псевдослучайных последовательностей (ПСП) содержит согласованный фильтр 1, пороговый блок 2, накопитель 3,делитель 4 частоты, дискриминатор 5, интегратор 6, шифратор 7, управляемую линию 8 задержки, генератор 9 тактовых импульсов. Входной сигнал в виде ПСП поступает на согласованный фильтр 1, на другой вход которого от управляемой линии 8 задержки поступает последовательность тактовых импульсов. На выходе согласованного фильтра 1 формируется сжатый сигнал, который записывается в регистры дискриминатора 5. По стробам, формируемым в ожидаемые моменты окончания ПСП, производится сравнение содержимого регистров дискриминатора 5 в моменты действия соседних стробов и при их неравенстве производится воздействие на управляемую линию 8 задержки, обеспечивая подстройку фазы тактовых импульсов. Цель достигается за счет обеспечения точной подстройки фазы тактовых импульсов, которая производится по сжатому сигналу в моменты превышения им порогового значения с накоплением фактов превышения порога. 1 з.п. ф-лы, 3 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Л0„„1596473 (51) 5 Н 04 ? 7/02

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К А ВТОРСНОМ У СВИДЕТЕЛЬСТВУ (21) 4359283/24-09 (22) 05.01.88 (46) 30.09.90. Вюл. Ф 36 (71) Л.M.Ãîðtoíîâà, И).С.Парижский, И.Н.Титова и А.H.Øïoëÿíñêèé (53) 621.394.662(088.8) (56) Авторское свидетельство СССР

Ф 1272475, кл. Н 03 Н 17/00, 1985.

Авторское свидетельство СССР и 1092744, кл. Н 04 L 7/02, 1983. (54)УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ (57) Изобретение относится к технике электросвязи. Цель изобретения — повьппение точности синхронизации. Устройство тактовой синхронизации псевдослучайных последовательностей (ПСП) содержит согласованный фильтр 1, пороговый блок 2, накопитель 3, делитель 4 частоты, дискриминатор 5, интегратор 6, шифратор 7, управляемую линию 8 задержки, генератор 9 тактс- .

2 вых импульсов. Входной сигнал в виде ПСП поступает на согласованный фильтр 1, на другой вход которого от управляемой линии 8 задержки поступает последовательность тактовых импульсов. На выходе согласованного фильтра 1 формируется сжатый сигнал, который записывается в регистры дискриминатора 5. По стробам, формируемым в ожидаемые моменты окончания

ПСП, производится сравнение содержимого регистров дискриминатора 5 в моменты действия соседних стробов и при их неравенстве производится воздействие на управляемую линию 8 задержки, обеспечивая подстройку фазы тактовых импульсов. Цель достигается за счет обеспечения точной подстройки фазы тактовых импульсов, которая производится по сжатому сигналу в моменты превышения им порогового значения с накоплением фактов превышения порога. 1 s.ï. ф-лы, 3 ил.

1596473

Изобретение относится к технике электросвязи и может быть использовано для тактовой синхронизации в системах связи с фаэовой манипуляцией или относительной фазовой манипуляцией

5 и сжатием сигнала.

Цель изобретения — повышение точности синхронизации.

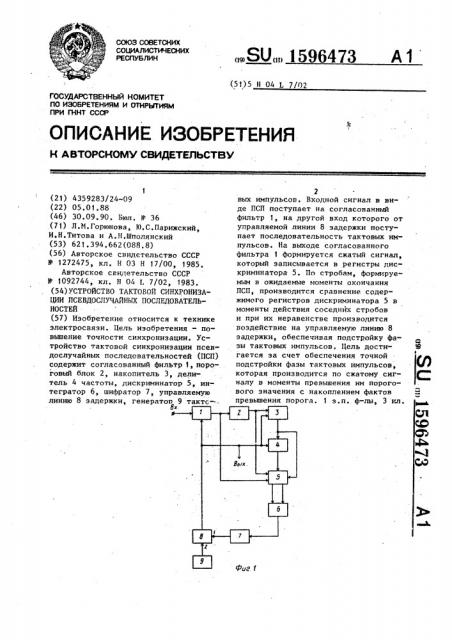

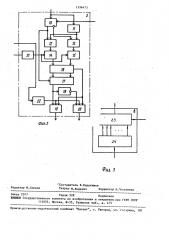

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 — показана схема дискриминатора; фиг.3 — пример выполнения управляемой линии задержки.

Устройство содержит согласованный фильтр 1, пороговый блок 2, накопитель 3, делитель 4 частоты, дискриминатор .5, интегратор 6, шифратор 7, управляемую лйнию 8 задержки, генератор 9 тактовых импульсов. Дискриминатор 5 содержит счетный триггер

10, элемент 11 задержки, элементы

И 12 и 13, регистры 14 и 15, блок 16 сравнения, коммутатор 17, инвертор

18, элементы И 19 и 20, блок 21 элементов задержки, элемент 22 задержки. Управляемая линия 8 задержки содержит коммутатор 23 и распределитель

24 импульсов.

Устройство работает следующим образом.

До подачи информационных слов на вход устройства из системы связи поступает последовательность синхронйзирующих кодовых посылок. Каждая посылка представляет собой псевдослу-: чайную последовательность (ПСП). !(аждый элемент ПСП имеет одно из двух возможных значений 0" или 1 в течение времени, равного одному такту. gg .Эти последовательности поступают на вход цифрового согласованного фильтра 1, который тактируется импульсами, поступающими с выхода управляемой линии 8 задержки.

На выходе фильтра 1 формируется сжатый сигнал в цифровом коде, величина которого определяется степенью соответствия принимаемой посылки эталонной ПСП. Это, в свою очередь зависит от отношения сигнала к шуму в

Ю канале связи и от того попадают ли тактовые импульсы на фронты или на плоские части входного сигнала. Полярность сжатого сигнала на выходе

5S фильтра 1 зависит от начальной фазы входной ПСП и может быть как положительной, так и отрицательной.

В блоке 2 сжатый сигнал сравнивается по модулю с пороговым значением. В случае превышения порога. на выходе блока 2 вырабатывается сигнал превышения порога. Накопитель 3 обеспечивает накопление фактов превышения порога и вырабатывает логический сигнал, когда накопленный сигнал превышает внутренний порог накопителя 3. Логический сигнал с выхода накопителя 3 поступает на установочный вход делителя 4 частоты, на счетный вход которого подаются тактовые импульсы. Коэффициент деления делителя 4 выбирается равным длине ПСП. Делитель 4 частоты представляет собой счетчик с дешифратором, на выходе которого формируются стробирующие импульсы в момент, когда состояние счетчика нулевое. Стробирующие импульсы поступают на вход счетного триггера 10 дискриминатора 5 и через элемент 11 задержки на входы элементов И 12 и 13, поочередно формирующих сигналы записи в регистры 14 или

15 в зависимости от состояния счетного триггера 10. На информационные входы регистров 14 и 15 через блок 21 поступает сжатый сигнал с выхода согласованного фильтра 1. Задержка каждого из элементов блока выбирается такой, чтобы к моменту записи код уже был установлен на информационных входах регистров 14 и 15. В регистр 14 записывается информация по нечетным стробам, а в регистр 15 по четным.

Содержимое регистров сравнивается с помощью блока 16 сравнения и в случае неравенства формируется единичный сигнал на выходах "Больше" или "Меньше". При этом,на выходе "Равно".блока

16 сравнения — единичный сигнал. При равенстве сравниваемых чисел на выходах "Больше", "Меньше" и Равно" нулевые сигналы.

Сигналы с выходов "Больше " или

Меньше" элемента 16 проходят на выход коммутатора 17 в зависимости от состояния счетного триггера 10, с выхода которого потупает управляющий сигнал для коммутатора 17. В моменты совпадения по времени выходного сигнала коммутатора 17 или его инверсии с сигналом, поступающим через элемент

22 задержки с выхода блока 2 и при отсутствии нулевого сигнала на выходе

"Равно" блока 16 на выходах элемента

И 19 и 20 возникают соответственно

5 159 единичный и нулевой сигналы. Эти выходные сигналы дискриминатора S посту пают в интегратор 6, При этом, число, накопленное интегратором 6, увеличивается на единицу, если сжатый сигнал в очередном такте меньше, чем в предыдущем и уменьшается на единицу в противоположном случае. Двоичное число с выхода интегратора 6 поступает на шифратор 7, где происходит его преобразование в код управления линией 8 задержки. В соответствии с кодом управления цифровая линия 8 задержки обеспечивает задержку тактовых импульсов, вырабатываемых генератором 9. ! С выхода генератора 9 импульсыпоступают на распределитель 24 импульсов управляемой линии 8 задержки (фиг.3), на выходах которого формируются и тактовых последовательностей одинаковой частоты и сдвинутых по фазе относительно друг друга. Эти последовательности поступают на соответствующие входы коммутатора 23 управляемой линии 8 задержки. В зависимости от управляющего сигнала коммутатора 3, поступающего с выхода шифратора 7, на выходе коммутатора

23 появляется одна из последовательностей, которая и является выходным сигналом устройства.

Таким образом, предлагаемое устройство обеспечивает по сравнению с устройством-прототипом более высокую точность синхронизации за счет того, что на вход схемы точная подстройка фазы тактовых импульсов производится по сжатому сигналу в моменты превышения им порогового значения с накоплением фактов превьппения порога. Формула из обретения

1. Устройство тактовой синхронизации псевдослучайных последовательностей, содержащее согласованный фильтр, гене.Ратор тактовых импульсов, пороговый блок, вход которого соединен с вы|ходом согласованного фильтра, делитель частоты и дискриминатор, о т л и ч а ю щ е е с я тем, что, с целью повьппения точности синхронизации1 в ! него введены накопитель, а также последовательно соединенные интегратор, шифратор и управляемая линия задержки, тактовый вход которой со6473 6 единен с выходом генератора тактовых импульсов, а выход подключен к тактовым входам согласованного фильтра, накопителя и делителя частоты, при этом первь|й вход дискриминатора соединен с выходом согласованного фильтра, второй вход подключен к выходу порогового блока и информационному входу накопителя, выход которого соединен с установочным входой делителя частоты: и третьим входом дискриминатора, четвертый вход которого подключен к выходу делителя частоты, а выходы соединены с входами интегратора.

2. Устройство по п.1, о т л и— ч а ю щ е .е с я тем, что дискриминатор содержит счетный триггер, два элемента задержки, четыре элемента

И, два регистра, блок сравнения, ком" мутатор, инвертор и блок элементов задержки, вход которого является первым вхсдом дискриминатора, а выход соединен с информационными входами первого и второго регистров, входы записи которых соединены соответственно с выходами первого и второго элементов И, первые входы которых подключены соответственно к прямому и инверстному выходам счетного триггера, тактовый вход которого является четвертым входом дискриминатора и через первый элемент задержки соединен с вторыми входами первого и вто35 рого элементов И, при этом выходы регистров соединены с соответствующими входами блока сравнения, выходы Больше" и "Меньше" которого подключены к

40 информационным входам коммутатора, управляющий вход которого соединен с прямым выходом счетного триггера, а выход коммутатора подключен к первому входу третьего элемента И не45 посредственно и через инвертор — к первому входу четвертого элемента И, при этом вторые входы третьего и четвертого элементов И через второй элемент задержки соединены с вторым вхо5О дом дискриминатора, а третьи входы третьего и четвертого элементов И подключены к выходу "Равно" блока сравнения, при этом установочный вход счетного триггера является третьим входом дискриминатора, а выходы третьего и четвертого элементов И являются выходами дискриминатора.

1596473

Фиг. s

"Составитель В.Евдокимов

Техред M,уоданич Корректор А.Осауленко

Редактор Ю,Середа

Заказ 2917 Тираж 528 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

1 13035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул. Гагарина, 101