Цифровой трансверсальный фильтр

Иллюстрации

Показать всеРеферат

Изобретение относится к технике обработки сигналов и может быть использовано для фильтрации электрических колебаний в широком диапазоне частот. Целью изобретения является упрощение устройства и расширение области применения. Цифровой трансверсальный фильтр содержит преобразователи кодов, буферные регистры, элемент задержки. При этом каждый I-й (при I=1,2...,N) преобразователь кода объединен с I-м буферным регистром в I-й блок памяти. Возможные варианты выполнения блоков приведены в описании изобретения. Изобретение позволяет уменьшить, стоимость фильтра, повысить его функциональные возможности, повысить его быстродействие. 1 з.п. ф-лы, 3 ил.

СООЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

Р1)У Н 03 Н 15/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

7 2-а Ь еп

Я

Юд/х 0fl

1-йЙИ

ФдЕ f

ГОСУДАРСТВЕННЫЙ НОМИТЕТ.

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К А BTOPCHOlVIY СВИДЕТЕЛЬСТВУ (21) 4275000/24-2.1 (22) 02.07.87 (46) 07.10.90. Бюл. Р 37 (72) А.В.Чепурных и В.Г,Михайлов (53) 621.318 (088.8) (56) Авторское свидетельство СССР

Р 1045384, кл. H 03 H 15/00, 1982. (54) ЦИФРОВОИ TPAHCBEPCAJIbHblA ФИЛЬТР (57) Изобретение относится к технике обработки сигналов и может быть использовано для фильтрации электрических колебаний в широком диапазоне час тот. Целью изобретения является упро„„SU„„1598119 А 1

2 щение устройства и расширение области применения. Цифровой трансверсальный фильтр содержит преобразователи кодов, буферные регистры, элемент задержки. При этом каждый i-й (при

1, 2...,N) преобразователь 1 кода объединен с i-м буферным регистром 2 в i-й блок 4 памяти. Возможные варианты выполнения блоков приведены в описании изобретения. Изобретение позволяет уменьшить стоимость фильтра, повысить его функциональные воэможности, повысить его быстродействие. 2 з.п. ф-лы, 3 ил.! 59811

Изобретение относится к технике обработки сигналов и может быть использовано для фильтрации электрических колебаний в широком диапазоне частот.

Цель изобретения — упрощение устройства и расширение области применения.

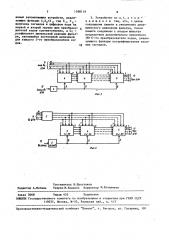

На фиг. 4 изображена структурная электрическая схема предлагаемого цифрового трансверсального фильтра; на фиг. 2 — схема выполнения блоков памяти; на фиг. 3 — схема усовершенствованного фильтра.

Цифровой трансверсальный фильтр (фиг. 1) содержит преобразователи 1 кодов, буферные регистры 2, элемент

3 задержки, каждый i-й (при i = 1,.

2,...,N) преобразователь 1 кода объединены с i-м буферным регистром 2 в

i-й блок 4 памяти. Кроме того, в фильтр введен (N+1)-й преобразователь

5 кода (фиг. 3).

Блок 4 памяти (фиг. 2) содержит преобразователь 1 кода, выходные шины 1,...,р которого подключены к соответствующим входным шинам 1,...,р буферного регистра 2. Первая группа входных шин 1,...,р преобразователя

1 кодов является первым входом 6 блока 4 памяти, а вторая группа входных шин 1,...,m является вторым входом

7 блока 4 памяти. Вход управления буферного регистра 2 служит входом

8 управления блока 4 памяти, а выход- 35 ные шины буферного регистра 2 служат выходом 9 блока 4 памяти..Выход 9 каждого i-ro блока 4 памяти (фиг. 2)

1 подключен к первому входу 6 (i+1)-го блока 4 памяти, а выход 9 N-го блока 40

4 памяти служит выходом 10 фильтра, Вторые входы 7 блоков 4 памяти соединены параллельно и служат информационным входом 11 фильтра. Синхронизирующий вход 12 фильтра через элемент 3 задержки подключен к управляю щим входам 8 блоков 4 памяти.

На фиг. 3 представлена схема выполнения фильтра по третьему пункту формулы изобретения. В данном случае вход фильтра 11 соединен с вторыми входами 7 блоков 4 памяти посредством (N+1)-ro преобразователя 5 кодов.

Цифровой трансверсальный фильтр работает следующим образом. „55

На вход 11 фильтра (фиг. 1) поступает информационный сигнал а в виде параллельного двоичного кода. Одно9

4 временно с ним на вход 12 синхронизации фильтра поступает сигнал синхронизации в виде периодических импульсов,.соответствующих смене информации на входе фильтра. Частота смены информации на входах 11 и 12 фильтра соответствует полосе обрабатываемых сигналов F F = 2f., где fc - частота следования информационных сигналов.

Входной m-разрядный сигнал с входа 11 фильтра поступает на вторые входы 7 блоков 4 памяти, реализующих функцию С;Х, + Х, в результате чего на входах буферных регистров 2 (фиг. 1) в блоках памяти 4 появляется р-разрядный код, соответствующий свертке входных сигналов с весами С ..

Сигнал синхронизации через время задержки, определяемое элементом 3 задержки, и равное времени распространения сигнала через преобразователь

1 кода появляется на управляющих входах буферных регистров 2.

По этому сигналу в буферные регистры 2 заносятся коды, присутствующие на их входах. Таким образом, в любой момент времени на выходах -го буферного регистра 2 присутствует код, соответствующей следующему выражению:

t где а „ — входная последовательность информационных сигналов.

На выходе 6 N-ro блока 4 памяти присутствует код, соответствующий полной свертке предыдущих входных сигналов с коэффициентами импульсной реакции фильтра (весовыми коэффициентами), определяющими амплитудно-частотную характеристику фильтра. Таким образом, каждое появление на входах

8 блоков 4 памяти синхросигнала сопровождается появлением на выходе

10 фильтра новой свертки, т.е. нового выходного сигнала.

Быстродействие фильтра определяется в основном временем задержки элемента 3 задержки, которое, в свою очередь, выбирается равным времени распространения сигнала через преобразователь 1 кода. Количество ячеек памяти V в N преобразователях кода определяется следующим выражением:

ttt t. p

Ч = N.р 2

Для N = 4, m = р = 6, V =. 105 тогда как для прототипа V = 10, т.е.

5 1598 в 1000 раз меньше. При памяти в 1011 бит можно обеспечить следующие характеристики предлагаемого фильтра:

N = 100, m = p = 10. Быстродействие предлагаемого фильтра должно быть 5 выше, так как время распространения сигнала через память в 10 бит (для прототипа) должно быть значительно больше, чем время распространения сигнала через один преобразователь кода, имеющий (для И = 100) в 100 раз меньше ячеек памяти. К тому же предлагаемый фильтр позволяет одновременно получать выходной сигнал со всех выходов 11 блоков памяти 4, т.е. реализовать многоканальную обработку сигналов. При этом на выходе каждого

i-го блока памяти 4 постоянно присутствует сигнал, подвергнутый фильтра- 20 ции в фильтре i-ro порядка. В фильтр (фиг. 3) введен (N+1)-й преобразователь 5 кода. 11ри этом количество разрядов информационного сигнала, поступающего на входы блоков 4 памяти, 25 можно значительно сократить. Количество разрядов (m ) кода второго сигнала в логарифмическом виде можно определить по следующей зависимости:

m = Iog (log„a ), где К - основание логарифма в преобразователе 5 кода.

При использовании целых чисел значение К определяет точность представ- З5 ления сигнала г в логарифмическом виде, которая вычисляется по следующей зависимости:

Для сигналов с динамическим диапазоном в 120 дБ и необходимой точностью в 1Х количество разрядов

45 уменьшится с 20 до 11 разрядов и соответственно объем памяти фильтра

3 сокРатитсЯ в — 2 раз,и в „ М

20 (о - r1 < раз.

11

В данном случае преобразователи

1 кодов реализуют функцию К" С . + К . х, 1

Конструкция блока памяти, содержащая только элементы памяти и обла55 дающая однородностью структуры, позволяет изготовлять их в интегральном исполнении с большой степенью интеграции. Коэффициенты С могут зано119 ситься заранее в процессе изготовления. Имея набор блоков памяти в микросхемном исполнении с различными С

1 можно быстро строить фильтры различного порядка или быстро перестраивать их характеристики. Изготовление фильтра не требует специальной подготовки, так как структура их предельно проста (последовательное включение элемен тов с заранее известными С ).

Таким образом, изобретение позволяет упростить схему и расширить область применения предлагаемого фильтра..

Экономический эффект от применения предлагаемого фильтра может быть получен путем уменьшения стоимости фильтра, повышения его функциональных возможностей (увеличение порядка фильтра и разрядности используемых сигналов), простоты изготовления, построения многофункциональных устройств обработки (за счет упрощения перестройки фильтра), а также путем увеличения быстродействия и, следовательно, области его применения. формула изобретения

1. Цифровой трансверсальный Фильтр

N-го порядка, содержащий преобразователь кода, отличающийся тем, что, с целью расширения области применения и упрощения, в него введены N-1 преобразователь кода, N буферных регистров и элемент задержки, причем преобразователи кодов объединены попарно с буферными регистрами посредством подключения своих выходных шин к соответствующим входным шинам буферных регистров в М блоков памяти, первая и вторая группы входных шин преобразователей кодов являются первым и вторым входами блоками памяти, а вход управления и выходные шины буферных регистров являются соответственно входом управления и выходом блоков памяти, выход каждого i-ro блока памяти подключен к первому входу (i+1)-ro блока памяти, а выход N-ro блока памяти является выходом фильтра, вторые входы блоков памяти соединены параллельно и являются информационным входом фильтра, синхронизирующий вход фильтра через элемент задержки подключен к управляющим входам блоков памяти.

2. Устройство по и. 1, о т л ич а ю щ е е с я тем, что преобразователи кодов выполнены в виде посто! 598119 у М нищ. 6к., ЯТФ

10 ги.йТФ

7Z иикр, 6»

«тФ

Фиг. г

6к. цТФ

l0 йи.

Ц1ф

Составитель В.Простаков

Редактор А.Мотыль Техред М.Ходанич Корректор M.Кучерявая

Заказ 3068 Тираж 652 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СЧСР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 яниых запоминающих устройств, реализующих функцию С; Х +Х „ где Х„ Х величина сигналов в цифровом «оде на первой и второй группе щин преобразо- 5 вателей кодов соответственно, а С1.,коэффициент импульсной реакции фильтра, являющийся постоянной величиной для каждого д-го преобразователя ко;. .дов.

3. Устройство по и. 1, о т л и ч а ю щ е е с я тем, что, с целью сокращения памяти и увеличения дина" мнческого диапазона фильтра, блоки памяти соединены с входом фильтра посредством дополнительно введенного (N+1)-го преобразователя кодов, реализующего функцию логарифмирования входных сигналов,