Самозащищенный транзисторный ключ

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в автономных инверторах. Цель изобретения - повышение КПД самозащищенного транзисторного ключа за счет исключения из силовой цепи датчика тока. Во время открытого состояния транзистора 1 на первый вход компаратора 3 поступает напряжение с блока 5 моделирования, а на второй вход - с измерителя 4 напряжения. При увеличении тока в силовой цепи транзистора 1 выше допустимого значения напряжение на втором входе компаратора 3 превышает напряжение на его первом входе. Компаратор 3 вырабатывает сигнал блокировки. Формирователь 2 тока выключает транзистор 1. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)я Н 03 К 17/60

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4456547/24-21 (22) 08.07.88 (46) 07.10.90. Бюл. М 37 (71) Специальное конструкторско-технологическое бюро автоматизации тяжелого металлорежущего оборудования (72) Г.В, Рязановский, Я;В. Чупин и А.П. Усачев (53) 621.382(088.8) (56) Авторское свидетельство СССР

К. 1283960, кл. Н 03 К 17/60, 1987, Машуков Е.В. Транзисторные устоойства коммутации и защиты сетей постоянного тока. Электронная техника в автоматике./Под ред. Ю.И. Конева, вып. 9 — М.: Советское радио, 1977, с, 28, рис. 9.

„„ 4 „„1598151 А1 (54) САМОЗАЩИЩЕННЫЙ ТРАНЗИСТОРНЫЙ КЛЮЧ (57) Изобретение относится к импульсной технике и может быть использовано в автономных инверторах. Цель изобретения — по-. вышение КПД самозащищенного транзисторного ключа за счет исключения из силовой цепи датчика тока. Во время открытого состояния транзистора 1 на первый вход компаратора 3 поступает нап ряжение с блока 5 моделирования, а на второй вход — с измерителя 4 напряжения. При уве-личении тока в силовой цепи транзистора 1 выше допустимого значения напряжение на втором входе компаратора 3 превышает напряжение íà его первом входе. Компаратор 3 вырабатывает сигнал блокировки. Формирователь 2 тока выключает транзистор 1. 3 ил, 1

1598151

40

Изобретение относится к импульсной технике и может быть использовано в автономных инверторах.

Цель изобретения — повышение КПД самозащищенности транзисторного ключа за счет исключения из силовой цепи датчика тока.

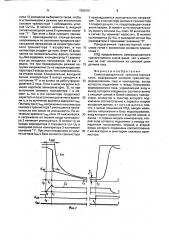

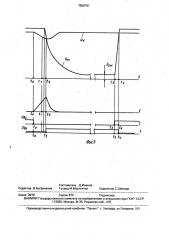

На фиг. 1 представлена схема самозащищенного транзисторного ключа; на фиг.

2 — 3 — диаграммы напряжений и токов, характеризующие работу предлагаемого устройства.

Самозащищенный транзисторный ключ содержит силовой транзистор 1, формирователь 2 тока, компаратор 3, измеритель 4 напряжения и блок 5 моделирования, причем выход компаратора 3 подключен к входу блокировки формирователя 2 тока, управляющий вход и выход которого соединены соответственно с входной шиной 6 и базой силового транзистора 1, коллектор и эмиттер которого подключены соответственно к первой и второй выходным шинам 7 и 8, вход блока 5 моделирования соединен с входной шиной 6, а выход — с первым входом компаратора 3, второй вход которого подключен к выходу измерителя 4 напряжения, первый и второй входы которого соединены соответственно с коллектором и эмиттером силового транзистора 1.

На фиг. 1 приведен также пример выполнения блока 5 моделирования процесса включения силового транзистора 1, в состав которого входят элемент 9 задержки, ключ

10, конденсатор 11, резистор 12 и источник

13 ЗДС смещения. При использовании ненасыщенного режима работы силового транзистора 1 он может иметь дополнительные связи с формирователем 2 тока (фиг. 1}.

Самозащищенный транзисторный ключ работает следующим образом.

В исхоцном состоянии на управляющий вход формирователя 2 тока поступает напряжение U»<, уровень которого соответствует уровню логической единицы. При этом с выхода формирователя 2 тока к базе силового транзистора 1 прикладывается отрицательное напряжение относительно эмиттера и силовой транзистор 1 заперт.

На его коллекторе присутствует высокое напряжение относительно эмиттера, а ток коллектора равен нулю, Выходное напряжение измерителя 4 напряжения, пропорциональное напряжению на коллекторе силового транзистора 1, поступает на второй вход компаратора 3. Напряжение 0вх с входной шины 6 поступает также на вход блока 5 моделирования. При этом ключ 10 включен и конденсатор 11 заряжен до разности между напряжением положительной шины "+" питания и ЭДС Ес источника 13 смещения.

Напряжение положительной обкладки конденсатора 11, являющееся выходным напряжением U блока 5 моделирования, прикладывается к первому входу компаратора 3. Коэффициент передачи измерителя

4 напряжения выбран таким, что в исходном состоянии напряжение UM на первом входе компаратора 3 больше, чем напряжение U< на втором входе (фиг. 2). При этом уровень сигнала Ug на выходе компаратора 3 соответствует логическому нулю. Т,е. воздействие управляющего сигнала U<> на управляющий вход формирователя 2 тока не блокировано, и силовой транзистор 1 может быть включен. При переходе в момент to сигнала Uâx из состояния "1" в состояние "0" к базе силового транзистора 1 прикладывается положительное напряжение и в его коллекторе начинает нарастать ток. Темп нарастания коллекторного тока определяется задаваемым формирователем 2 тока темпом нарастания тока базы. Напряжение на коллекторе силового транзистора 1 и сигнал

U< измерителя 4 напряжения при этом остаются постоянными или незначительно уменьшаются. В блоке 5 моделирования выключение ключа 10 задержано с помощью элемента 9 задержки на время д, относительно отрицательного фронта сигнала О».

Поэтому напряжение на первом входе компаратора 3 в течение времени тзд остается постоянным. По окончании рассасывания носителей в обратном диоде, шунтирующем нагрузку (не показаны), в момент t> ток коллектора перестает нарастать и становится равным току нагрузки 1н. Напряжение на коллекторе силового транзистора 1 уменьшается до величины примерно равной падению напряжения от тока I< нагрузки на динамическом сопротивлении коллекторного слоя в момент t>. Пропорционально уменьшается и выходное напряжение U< измерителя 4 напряжения до величины 0, Время задержки т, д выбирается большим, чем расчетное время t1, поэтому после спада коллекторного напряжения силового транзистора 1 и сигнала 0 по истечении времени задержки з д ключ 10 выключается и конденсатор 11 разряжается на резистор

12. При этом выходное напряжение блока 5 моделирования снижается, в данном примере реализации, по экспоненте, приближенно моделируя процесс безаварийного включения силового транзистора по напряжению. С течением времени сопротивление коллекторного слоя уменьшается, и напряжение на коллекторе силового транзистора 1 также уменьшается, достигнув к моменту времени установившегося значения. ЭДС Есм источ-, 1598151 ника 13 смещения выбирается такой, чтобы в установившемся режиме при включенном силовом транзисторе 1 соблюдалось условие U<

0вх без задержки, и конденсатор 11 заряжается до исходного напряжения. Из фиг. 2 видно, что при безаварийном режиме на- 15 грузки напряжение UM на первом входе компаратора 3 всегда выше, чем напряжение U< на втором входе. Следовательно, выходной сигнал компаратора 3 всегда находится в состоянии "0" и не влияет на работу форми- 20 рователя 2 тока. Если в цепи нагрузки возникло короткое замыкание (фиг. 3), то при включении силового транзистора 1 в момент to ток в его коллекторе продолжает нарастать и по истечении расчетного време- 25 ни t1, и по истечении времени задержки taaA.

Поэтому при 1>Ьзд напряжение на коллекторе силового транзистора 1 уменьшается незначительно или вовсе не уменьшается. По истечении времени т д ключ 10 выключается, 30 . и напряжение на первом входе компаратора 3 начинает уменьшаться. В момент tz на входах компаратора 3 становится UK> UM u выходной сигнал компаратора 3 принимает значение "1". При этом независимо от уров- 35 ня сигнала Ua> к базе силового транзистора

1 прикладывается отрицательное напряжение. Ток в коллекторе силового транзистора

1 снадаетдо нуля. т.е. предотвращается развитие аварии. В момент а по отрицательному фронту сигнала U»< ключ 10 включается, и сигнал U> начинает нарастать. В момент и становится 0 <0, и выходной сигнал Usa компаратора 3 принимает значение "0".

Предлагаемый транзисторный ключ снова готов к включению силового транзистора 1, КПД предлагаемого самозащищенного транзисторного ключа выше, чем у известных за счет исключения из силовой цепи датчика тока.

Формула изобретения

Самозащищенный транзисторный ключ, содержащий силовой транзистор. формирователь тока и компаратор, выход которого подключен к входу блокировки формирователя тока, управляющий вход и выход которого соединены соответственно с входной шиной и базой силового транзистора, коллектор и змиттер которого подключены соответственно к первой и второй выходным шинам, отличающийся тем, что; с целью повышения КПД, введен измеритель напряжения и блок моделирования, вход которого соединен с входной шиной, а выход — с первым входом компаратора, второй вход которого подключен к выходу измерителя напряжения, первый и второй входы которого соединены соответственно с коллектором и змиттером силового транзистора.

Составитель Д.Иванов

Редактор В.Бугренкова Техред М.Моргентал Корректор С,Шекмар

Заказ 3070 Тираж 670 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101