Трехзначный элемент

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано при построении вычислительных и управляющих систем с трехзначным алфавитом. Цель изобретения - расширение функциональных возможностей за счет формирования обратных связей. Устройство содержит входную шину 1, шины 3, 4, 5 питания, выходную шину 6, КМДП-инверторы 7, 12, 14, 16. Для реализации режима хранения введены КМДП-инверторы 8, 9, 10, 11, 13, 15 и вторая входная шина 2. При работе устройства на входную шину 1 поступает управляющий сигнал "Запись-хранение", а на входную шину 2 - информационный сигнал в трехзначном алфавите. В режиме записи на выходной шине 6 формируется сигнал, значение которого совпадает со значением сигнала на входной шине 2. Этот выходной сигнал сохраняется на все время "хранения". 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s Н 03 К 19/094

ГОСУДАРСТВЕННЫИ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ. ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

1 (21) 4629065/24-21 (22) 30.12,88 (46) 07.10,90. Бюл. М 37 (71) Институт прикладной математики им. M.В. Келдыш.а (72) Ю.А. Виноградов (53) 621 ..374(088.8) (56) Авторское свидетельство СССР

bh 1336227, кл. Н 03 К 19/094, 30.08.85, (54) ТРЕХЗНАЧНЫЙ ЭЛЕМЕНТ (57) Изобретение относится к импульсной технике и может быть использовано при построении вычислительных и управляющих систем с трехзначным алфавитом, Цель изобретения — расширение функциональных Ы „1598160 Al возможностей за счет формирования обратных связей. Устройство содержит входную шину 1, шины 3, 4, 5 питания, выходную шину 6, КМДП-инверторы 7, 12, 14, 16. Для реализации режима хранения введены

КМДП-инверторы 8, 9, 10, 11, 13, 15 и вторая входная шина 2, При работе устройства на входную шину 1 поступает управляющий сигнал "Запись-хранение". а на входную шину 2 — информационный сигнал в трехзначном алфавите. В режиме записи на выходной шине 6 формируется сигнал, значение которого совпадает со значением сигнала на входной шине 2, Этот выходной сигнал сохраняется на все время "хранения". 1 табл. 2 ил.

1598160

40

Изобретение относится к импульсной технике и может быть использовано при построении вычислительных и управляющих систем с трехзначным алфавитом.

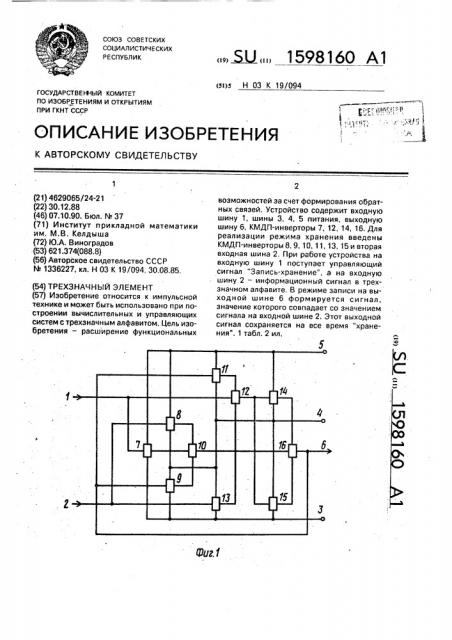

Цель изобретения — расширение функциональных возможностей за счет формирования, обратных связей и выполнения функции памяти, На фиг, 1 представлена электрическая схема устройства;.на фиг. 2 — схема КМДПинвертора.

Устройство содержит первую 1 и вторую

2 входные шины, первую 3, вторую 4 и третью 5 шины питания, выходную шину 6, КМДП-инверторы,.7-16, В таблице приведены данные истинности трехзначного элемента.

Входы инверторов 7 и 12 соединены с первой входной шиной 1, выход инвертора

16 — с выходной шиной.6, выход инвертора

14 — с выходом инвертора 12, выход инвертора 14 — с истоком р-канального транзистора инвертора 16, исток и-канального транзистора инвертора 7 соединен с первой шиной 3 питания, исток и-канального транзистора инвертора 14 — с второй шиной 4 питания, истоки р-канальных транзисторов инверторов 7 и 14 — с третьей шиной 5 питания, с второй входной шиной 2 соединены входы инверторов 8 и 13, выход инвертора

13 соединен с истоком и-канального транзистора инвертора 12, выход инвертора 8 — с истоком р-канальноготранзистора инвертора 10, входы инверторов 9 и 11 соединены с выходной шиной 6, выход инвертора 9 соединен с истоком и-канального транзистора инвертора 10, выход инвертора 11 — с истоком р-канального транзистора инвертора

12, вход инвертора 15 — с выходом инвертора 12, выход инвертора 15 — с истоком и-канального транзистора инвертора 16. С первой шиной 3 питания соединены истоки п-канальных транзисторов инверторов 9, 13, 15, с второй шиной питания соединены истоки и-канальных транзисторов инверторов 8 и 11 и исток р-канального транзистора инвертора 9, с третьей шиной питания 5 соединены истоки р-канальных транзисторов инверторов 7, 8 и 11.

Рассмотрим функционирование элемента. Пусть электрические потенциалы шин питания 3, 4 и 5 — соответственно Ео, Е1 и Ег представляют собой логические 0 1 и 2, причем

Б-EH > Опор, Ц1, 2} (1) где Unop, — пороговое напряжение МДПтранзистора.

При таких условияхэлектрический notevqrean на выходе КМДП-пары связей с электрическим потенциалом на ее входах а (затворы)„В (р-исток). и y (n-исток) следующим образом;

f(Ea ЕР, Ey) =

Ео,приЕ у = Eo,Е а > ЕО,Ер 9 Е а .

EP = Е1,E а = Ео,EP > Е2;

Е = Е1 Е а — — Е2 ЕР Ео;

Е2приЕP = Е2,Еа(Ег,Еу «) Еа, Разорвем связь выходной шины 6 с входом инвертора 9. Объединенные входы инверторов 9 и 11 будем рассматривать в качестве третьего входа устройства. Примем обозначение: z — сигнал на шине 1, х— сигнал на шине 2, у — сигнал на объединенных входах инверторов 9 и 11; ft — сигнал. на выходе I-го инвертора. Рассмотрим все возможные входные наборы из х, у 6(0, 1, 2), Данные истинности позволяют судить о функционировании любого фрагмента устройства и устройства в целом. Заметим, что

F(x, у, z=0) =у и F(x, у, z=2) =x, где F — сигнал нв выходе элемента(F— = f>g). Тоесть, водном случае на выходе схемы формируется сигнал в точности совпадающий с у, а в другом

=от у не зависящий. Это означает, что восстановив связь выходной шины элемента с входами инверторов 9 и 11 получают корректную схему, реализующую трехзначную ную функцию "тождественный Х" при z=2 (режим записи) и сохраняющую любое иэ трех возможных здесь значений при г=0 (режим хранения результата).

Формула изобретения

Трехзначный элемент, содержащий первую входную шину, соединенную с входами первого и второго инверторов, выходную шину, соединенную с выходом третьего инвертора, четвертый инвертор, вход кото- . рого соединен с выходом первого инвертора, а его выход — с истоком р-канального транзистора третьего инвертора, первую, вторую и третью шины питания, соединенные соответственно с истоком и-канального транзистора второго инвертора, с истоком и-канального четвертого инвертора и истоками р-канальных транзисторов второго и четвертого инверторов, от л ич а ю щи йс я тем, что. с целью расширения функциональных возможностей, в него введены пятый, шестой, седьмой, восьмой, девятый и десятый инверторы., и вторая входная шина, 1598160 с которой соединены входы шестого и девятого инверторов, выходы которых соединены соответственно с истоком р-канального транзистора седьмого инвертора и истоком и-канального транзистора первого инверто- 5 ра, входы пятого и восьмого инверторов соединены с выходной шиной, выход пятого инвертора соединен с истоком р-канального транзистора первого инвертора, выход восьмогоинвертора-систокомп-канально- 10 го транзистора седьмого инвертора, вход седьмого инвертора соединен с выходом второго инвертора, выход седьмого инвертора — с входом третьего инвертора, вход десятого инвертора соединен с выходом первого инвертора, выход десятого инвертора — с истоком и-канального транзистора третьего инвертора, с первой шиной питания соединены истоки и-канальных транзисторов восьмого, девятого и десятого инверторов, с второй шиной питания соединены истоки р-канальных транзисторов восьмого, девятого, десятого инверторов и исток п-канального транзистора пятого инвертора, с третьей шиной питания соединены истоки р-канальных транзисторов пятого и шестого инверторов, f8 т14 f15 т16 т9

Фи.2

Составитель А.Цехановский

Редактор В.Бугренкова Техред М.Моргентал Корректор С.Шекмар

Заказ 3070 Тираж 661 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101

О

О

О.

О

О

О

2

2

2

2

О

О

1

2

2

0

О

1

2

0

2 .О

2

1

О

О

2

О

2

2

2

1

1

2

2

2

1

0

1

О

0

О

0

1

О

0

0

1

О

О

О.

2

2

2

2

1

2

2

1

2

2

2

1

2

2

1

1

0

0

1

1

О

0

0

1 .1

0

О

О

1

1

2

1

2

2

2

2

0

0

О

О

О

0

0

1

1

О

2

О

2

О

2

О

1

1

2