Устройство для подавления негауссовых помех в приемнике с бинарным квантованием сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - повышение эффективности подавления помех с симметричным бимодальным распределением вероятности и произвольной шириной спектра. Устройство для подавления негауссовых помех в приемниках с бинарным квантованием сигнала состоит из жесткого ограничителя 2, первого и второго компараторов 1 и 3, сумматора 5 и блока 4 пороговых напряжений. Устройство осуществляет нелинейное преобразование входного сигнала с регулировкой пороговых напряжений компараторов 1 и 3. Пороговые напряжения определяются блоком 4 пороговых напряжений путем оценки положительной моды распределения вероятности отсчетов входного сигнала, что обеспечивает максимальное подавление помехи после нелинейного преобразования входного сигнала. Дана ил. выполнения блока 4 пороговых напряжений. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 Н 04 В 1/10

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4432271/24-09 (22) 30.03.88 (46) 07.10.90.Бюл. М 37 (72) И.Ю.Асписов, В.Г.Валеев и Е,А.Ривелис (53) 621.396,669(088.8) (56) Авторское свидетельство СССР

М 1427453, кл. Н 04 В 1/10, 1986. (54) УСТРОЙСТВО ДЛЯ ПОДАВЛЕНИЯ НЕГАУССОВЫХ ПОМЕХ В ПРИЕМНИКЕ С БИНАРНЫМ КВАНТОВАНИЕМ СИГНАЛА (57) Изобретение относится к радиотехнике.

Цель изобретения — повышение эффективности подавления помех с,симметричным бимодальным распределением вероятности и произвольной шириной спектра. Устройство для подавления негауссовых помех в, Ы,, 1598178 А1 приемниках с бинарным квантованием сигнала состоит из жесткого ограничителя 2, первого и второгор компараторов 1 и 3, сумматора 5 и блока 4 пороговых напряжений.

Устройство осуществляет нелинейное преобразование входного сигнала с регулировкой пороговых напряжений компараторов 1 и 3. Пороговые напряжения определяются блоком 4 пороговых напряжений путем оценки положительной моды распределения вероятности отсчетов входного сигнала, что обеспечивает максимальное подавление помехи после нелинейного преобразования входного сигнала. Дана ил, выполнения блока 4 пороговых напряжений. 2 ил.

1598178

10

30

Изобретение относится к радиотехнике и может быть использовано в радиотехнических и гидроакустических системах с обработкой бинарно квантованных сигналов.

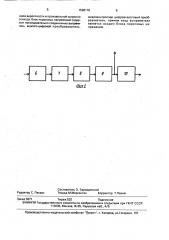

Цель изобретения — повышение эффективности подавления помех с симметричным бимодальным распределением вероятности и произвольной шириной спектра, На фиг.1 представлена структурная электрическая схема устройства; на фиг.2— структурная схема блока пороговых напряжений.

Устройство для подавления негауссовых помех в приемниках с бинарным квантованием сигнала содержит первый компаратор 1, жесткий ограничитель 2, второй компаратор 3, блок 4 пороговых напряжений, сумматор 5, выпрямитель 6, аналого-цифровой преобразователь 7, микроконтроллер 8, цифроаналоговый преобразователь 9, инвертирующий повторитель

10.

Устройство работает следующим обра-. зом.

Входные сигналы поступают на входы первого 1 и второго 3 компараторов, жесткого ограничителя 2, которые совместно с сумматором 5 осуществляют нелинейное преобразование с характеристикой

f(x)=s ig п(х+А >)-s ig n(x)+s ig п(х-А 1), где -A> и Ai — величины пороговых напряжений, вырабатываемых блоком 4 пороговых напряжений 4; х — входной сигнал, Если входной сигнал содержит полезный сигнал и мощную помеху с симметричным бимодальным распределением вероятности мгновенных значений W(x), то коэффициент подавления помех с нелинейным преобразованием. определяется соотношением ,и(А ) = 4 i nPW(A>)-W.ß, где Pn — мощность помехи.

Из этого выражения следует, что максимальное подавление помехи посла нелинейного преобразования достигается при значении порогового напряжения А>, равном положительной моде распределения вероятности помехи W(A>)=maxW(x). Блок 4 пороговых напряжений вычисляет эту величину порога А, что и обеспечивает настройку первого и второго компараторов на максимальное подавление помехи. Величины порогов А> и -A< подаются с выходов блока 4 пороговых напряжений на управляющие входы первого 1 и второго 3 компараторов.

Входной сигнал х подается на вход блока 4 пороговых напряжений.

При этом предполагается, что мощность помехового сигнала значительно превышает мощность полезного сигнала. Поскольку распределение помехи предполагается симметричным, то в блоке 4 пороговых напряжений анализируется распределение абсолютных значений сигнала, получаемых на выходе выпрямителя 6 и подаваемых на вход аналого-цифрового преобразователя

7. Микроконтроллер 8 осуществляет накапливающую запись в ячейки оперативной памяти единиц в соответствии с двоичным кодом сигнала с аналого-цифрового преобразователя 7, трактуя этот двоичный код как адрес ячейки оперативной памяти. После выборки заданного числа входных отсчетов сигнала микроконтроллер 8 осуществляет поиск максимального числа в ячейках памяти и на вход цифроаналогового преобразователя 9 поступает двоичный код адреса ячейки с максимальным числом. Таким образом микроконтроллер 8 формирует двоичный код оценки моды распределения помехи для формирования пороговых напряжений. Полученный код хранится во входном регистре цифроаналогового преобразователя 9, а цикл работы микроконтроллера 8 повторяется, Пороговое напряжение

А> с выхода цифроаналогового преобразователя 9 подается на инвертирующий повторитель 10 для формирования отрицательного порогового напряжения — А, Определение наилучших пороговых напряжения А и -A) нелинейного преобразования для помех с симметричным бимодальным распределением вероятности и произвольной шириной спектра позволяет повысить эффективность их подавления.

Формула изобретения

Устройство для подавления негауссовых помех в приемнике с бинарным квантованием сигнала, состоящее из жесткого ограничителя. первого и второго компараторов, сумматора и блока пороговых напряжений с инвертирующим повторителем, причем вход и выход инвертирующего повторителя являются выходами блока пороговых напряжений и соединены соответственно с управляющими входами первого и второго компараторов, выходы которых подключены к соответствующим входам сумматора, входы жесткого ограничителя, первого и второго компараторов и блока пороговых напряжений объединены, а выход жесткого ограничителя подключен к инвертирующему входу сумматора, выход которого является выходом устройства, о тл и ч а ю щ е е с я тем, что, с целью повышения эффективности подавления помех с симметричным бимодальным распределе" .

1598178

Составитель О. 3арощинский

Техред M.Ìîðãåíòàë . Корректор Т,Палий

Редактор С. Пекарь

З,аказ 3071 Тираж 532 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул.Гагарина, 101 нием вероятности и произвольной шириной спектра, блок пороговых напряжений содержит последовательно соединенные выпрямитель, аналого-цифровой преобразователь. микроконтроллер, цифроаналоговый преобразователь, причем вход выпрямителя является входом блока пороговых наи ряжений.