Устройство для разделения сигналов в многоканальных системах передачи

Иллюстрации

Показать всеРеферат

Изобретение относится к связи и может найти применение в многоканальных системах для передачи двоичного кода с временным разделением сигналов. Целью изобретения является повышение скорости и помехоустойчивости передачи. Поставленная цель достигается за счет введения на передающей стороне блока 12 регистров, блока 7 дешифрации, блока 6 элементов И, сумматора 11 и цифроаналогового преобразователя 8, а на приемной стороне - блока 17 регистров, сумматора 18, блока 24 дешифрации, генератора 13 тактовых импульсов, выделителя 16 синхроимпульсов, аналогоцифрового преобразователя 22, блока 14 вычитания, запоминающего блока 21, блока 15 счетчиков, порогового блока 23 и блока 25 элементов И.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСН ИХ

РЕСПУБЛИМ

В))5 H 04 J /00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ

flQ ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯЦ

ПРИ ГНИТ СССР (21) 4491745/24-09 (22) 10.10.88 (46) 07.10.90. Бюл. 1 37 (71) Минский радиотехнический институт (72) А.Г.Саперов и Л.N.Tðóáèöûí (53) 621.394.4(088.8) (56) Баева Н ° и др. Основы многоканальной связи. — М.: Связь, 1975, с. 26-30. (54) УСТРОЙСТВО ДЛЯ РАЗДЕЛЕНИЯ СИГНА.

ЛОВ В МНОГОКАНАЛЬНЫХ СИСТЕМАХ ПЕРЕДАЧИ (57) Изобретение относится к связи и может найти применение в многоканальных системах для передачи двоичного

Изобретение относится к связи и может найти применение 8 многоканальных системах для передачи двоичного кода с временным разделением сигналов.

Целью изобретения является повышение скорости и помехоустойчивости передачи.

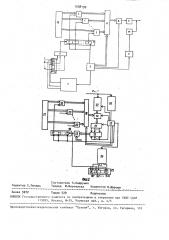

На фиг. 1 изображена структурно-. электрическая схема передающей стороны устройства; на фиг. 2 - структурно-электрическая схема приемной стороны устройства.

Устройство содержит на передающей стороне перемножитель 1, задающий генератор 2, регистр 3 сдвига, элемент ИЛИ 4, Формирователь 5 синхроимпульсов, блок 6 элементов И. блок 7 дешифрации, цифроаналоговый преоб„„SU„„15 8190 А1

2 кода с временным разделением сигналов. Целью изобретения является повышение скорости и помехоустойчивости передачи. Поставленная цель достигается за счет введения на передающей стороне блока 12 регистров, блока 7 дешифрации, блока 6 элементов И, сумматора 11 и цифроаналогового преобразователя о, а на приемной стороне — ; блока 17 регистров, сумматора 18, блока 24 дешифрации, генератора 13 тактогых импульсов, выделителя 16 синхроимпульсов, аналого-цифрового преобразователя 22, блока 14 вычитания, запоминающего блока 21, блока

15 счетчиков, порогового блока 23 и блока 25 элементов И. 2 ил. разователь 8 первый 9 и второй 10 фильтры нижних частот сумматор 11 и блок 12 регистров, а на приемной стороне - генератор 13 тактовых импульсов, блок 14 вычитания, блок 15 ©©

=четчиков, выделитель 16 синхроим" пульсов, блок 17 регистров, сумматор CO

18, регистр 19 сдвига. перемножитель 4Р

20, запоминающий блок 21,аналого-цифровой преобразователь 22, пороговый блок 23, блок 24 дешифрации и блок

25 элементов И.

Устройство работает следующим образом. ° Зь

Передвигаемый двоичный код от каждого источника подается последовательно на первые входы блока 6 элементов И. Блок 7 дешифрации поочеред но с интервалом времени

1598190

Т л/Q

Up! U k 4м

35 с ъ)1

Я, 2 х,„,; (т), =1 где . - длительность импульса — число интеРвалов, на которое 5 делится разрешает прохождение каждого разряда источников сообщений на вход элемента ИЛИ 4, Получаемая в результате двоичная последовательность с выхода элемента ИЛИ 4 последовательно поступает в регистр 3 сдвига и сдвигается в нем с интервалом времени Т. Значения функции Y(t) для моментов времениt,, t„+T, t,+2Т, ..., t+Qt (Q = 1, 2, 3...) вычисляются предварительно по Формуле

Y(t) = А, - Ytt — (и — 1) Т3 °

111 I хехр (- /З T (m — 1) 3, где m — - порядковый номер импульса, Y(t) = Во. cosy>(t) a(t), a(t) = ехр(-p t ), 4

q(t) = ) cd(t) -dt, u(t) о

= cd exp(- p ), 41пс

6 л л

t

2 2 с — число раз, в которое изменяется a(t) и ы(е), Еo — средняя частота спектРа Y(t). 40 и хранятся в виде параллельных M-разрядных кодов в блоке 12 регистров.

Значения функции вычисляются начиная с момейта времени, соответствующе1

ro dY(t )/dt = max и равного

Esp причем Функция синуса для Y(t) в этой точке равна нулю. В результате этого в перемножителе 1 происходит поразрядное перемножение двоичной последо- 50 вательности на соответствующие значения функции Y(t). Иноговходовый сумматор 11 в течение каждого Т выдает в канал через цифроаналоговый пре образователь 8 и первый фильтр 9 55 нижних частот сигнал где Х - значение р-зряда i ro источ1 ника.

Для обеспечения синхронизации передаваемых и принимаемых значений

U ; задающий генератор 2 в каждом тактовом интервале Т генерирует импульс синхронизации, который поступает на вход формирователя 5 синхроимпульсов, который формирует из импульса прямоугольной формы сигнал синхронизации для передачи по каналу связи и передает через второй фильтр

10 нижних частот в определенной полосе частот s канал. Выходы задающего генератора служат для синхронизации работы блоков передающей стороны устройства.

На входе приемной стороны выдели" тель 16 синхроимпульсов формирует сигнал синхронизации, который запускает генератор 13 тактовых импульсов. На выходе генератора 13 тактовых импульсов появляется импульс,. Разрешающий работу аналого-цифрового преобразователя 22, который преобразует сигнал U > ., в цифровую форму и передает на блок 14 вычитания. Блок 14 вычитания производит вычитание из сигнала U ; значения моделируемого сигнала П „;

Так как речь идет о двоичном коде, то в каждом Т могут присутствовать 2 различных значений U p„ °

При поступлении в очередном Т .на вход запоминающего блока 21 одного из кодов U „ на информационном его выходе после считывания появится двоичный параллельный код, число разрядов которого означает наличие

"1" .в соответствующем разряде двоичной последовательности. В каждом Т с выхода запоминающего блока 2l единицы соответствующих разрядов добавляются (или не добавляются в случае нуля) к содержимому соответствующих счетчиков. Перед началом следующего такта содержимое каждого j-ro счетчика (где j = 1,2,3....,?.) переписывается в (j + 1) счетчик, после чего первый счетчик обнуляется.

Таким образом, после L тактов в крайнем левом L-м счетчике накопится число единиц, равное числу случаев, когда данный разряд определен как единичный. Если это число единиц

15981 больше Ь/2, то пороговый блок 23 формирует на выходе единицу, если меньше либо равно Ь/2 — ноль, С выхода порогового блока 23 значение -сформированного разряда зано5 сится в регистр 19 сдвига, после чего перемножители 20 производят операцию X Y(k Т) и подают данные зна1 чения на многовходовый сумматор 18.

Работа блоков 19, 20, 17, 18 приемной части полностью аналогична работе блоков 3, 1, 25 и 21 передающей стороны. Код с выхода порогового блока 23 подается на второй вход блока 14 вычитания, который в каждом Т производит вычитание этого кода из кода с аналого-цифрового преобразователя 22.

Значения двоичной последователь- 20 ности с выхода порогового блока 23 поступают одновременно на первые входы блока 2 элементов И, в котором происходит разделение принятых разрядов по соответствующим каналам. Ге- 25 нератор 13 тактовых импульсов управляет работой блока 24 дешифрации.

Последний имеет число выходов, равное числу разделяемых каналов, при этом выходы поочередно активизуются на время Т и разрешают прохождение разряда двоичной последовательности соответствующим получателем cooGщений.

Формула изобретения

Устройство для разделения сигналов в многоканальных системах передачи, содержащее на передающей стороне перемножители, первый и второй фильтры нижних частот, элемент ИЛИ, формирователь синхроимпульсов, последовательно соединенные задающий генератор и регистр сдвига, выходы которого подключены к первым входам перемножителей, а на приемной стороне45 перемножители, выделитель синхроимпульсов, и регистр сдвига, выходы которого подключены к первым входам перемножителей, о т л и ч а ю щ е ес я тем, что, с целью повышения скорости и помехоустойчивости передачи, введены на передающей стороне блок регистров, блок дешифрации, блок элементов И. последовательно соединенные сумматор и цифроаналоговый преобразователь, выход которого под ключен к входу первого Фильтра нижI

6 них частот, выходы блока регистров подключены к вторым входам перемножителей, выходы которых подключены к сигнальным входам сумматора, выходы блока дешифрации подключены к первым входам блока элементов И, вы" ходы которого подключены к входам элемента ИЛИ, выход которого подключен к второму входу регистра сдвига, с второго по пятый выходы задающего генератора подключены соответственно к входу блока дешифрации, к тактовым входам сумматора, к второму входу цифроаналогового преобразователя и к входу формирователя синхроимпульсов, выход которого через второй фильтр нижних частот подключен к выходу первого фильтра нижних частот и является выходом передающей стороны устройства, входами которой являются вторые входы блока элементов И, а на приемной стороне введены блок ре" гистров, сумматор, блок дешифрации, генератор тактовых импульсов, выдели" тель синхроимпульсов, последовательно соединенные аналого-цифровой преобразователь, блок вычитания, и запоминающий блок, последовательно соединенные блок счетчиков, пороговый блок и блок элементов И, вторые вхо" ды которого соединены с выходами блока дешифрации, выходы блока регистров подключены к вторым входам перемножи" телей, выходы которых подключены к сигнальным входам сумматора, выход которого подключен к второму входу блока вычитания, выходы запоминающего блока подключены к счетным входам блока счетчиков, выход порогового блока подключен к сигнальному входу регистра сдвига, выход выделителя синхроимпульсов подключен к входу генератора тактовых импульсов, выходы которого подключены к входу блока дешифрации, к второму входу запоминающего блока, к третьему входу блока вычитания и к тактовым входам регистра сдвига, блока счетчиков и анало" го-цифрового преобразователя, вход которого соединен с входом выделителя синхроимпульсов и является сигналь ным входом приемной стороны устройства, опорным входом и выходами которой являются соответственно второй вход порогового блока и выходы блока элементов И.

1598190

Net

Составитель О.Андрушко

Техред М.Моргентал Корректор И.Шароши

Редактор С.Пекарь ай 1а

Заказ 3072 Тираж 529 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ С СР

113035, Москва, Ж-35, Раушская наб., д. 4/5 с

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101