Устройство для цифрового формирования сигналов с амплитудно- фазовой модуляцией и одной боковой полосой

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - повышение точности формирования сигналов. Устр-во содержит источник 1 данных, кодер 2, блоки 3-6 задержки, мультиплексор 7, блок 8 памяти, буферный регистр 9, сумматор 10, регистр 11, ключ 12, ЦАП 13, фильтр 14, блок 15 управления, блок 16 формирования адресов и переключатель 17 скорости работы. Двоичная последовательность с источника 1 поступает на кодер 2, который в три этапа перекодирует ее в четыре последовательности. Из них далее блоки 3-6 задержки формируют четыре двоичных разрядных слова, которые поступают на мультиплексор 7. Он поочередно коммутирует на выход каждое из слов, которое поступает в блок 8 памяти. На его выходах поочередно появляются многоразрядные числа, которые поступают на сумматор 10 непосредственно и через регистр 9 со сдвигом на один разряд влево. Далее числа записываются в регистр 11 и через ключ 12 поступают на ЦАП 13, преобразующий числа в отсчеты аналогового сигнала. Затем фильтр 14 отфильтровывает в них побочные продукты преобразования. Даны ил. выполнения кодера 2, блока 15 управления и блока 16 формирования. 3 ил.

СОЮЗ СОВЕТСКИХ . СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

1 (19) (11) щ) H 04 I, 27/18

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BT0PCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4430104/24-09 (22) 24,05.88 (46) 07.10.90. Бюл. " 37 (71) Новосибирский электротехнический институт связи им. Н.Д.Псурцева (72) Н.В.Верховский, Г.Х.Гарсков и А.Н.Горидько . (53) 621.394.14(088.8) . (56) Авторское свидетельство СССР

М 1070703. кл. Н 04 I. 27/18, 1981. (54) УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ФОРНИРОВАНИЯ СИГНАЛОВ С АИПЛИТУДНО-ФАЗОВОЙ МОДУЛЯЦИЕЙ И ОДНОЙ FOKOBOA ПОЛОСОЙ (57) Изобретение относится к технике связи ° Цель изобретения - повышение точности формирования сигналов. Устрво содержит источник 1 данных, кодер 2, блоки 3-6 задержки, мультиплексор. 7, блок 8 памяти, буферный регистр 9, сумматор 10, регистр 11, ключ 12, ЦАП 13, фильтр 14, бгок 15

2 управления, блок 16 формирования адресов и переключатель 17 скорости работы. Двоичная последовательность с источника 1 поступает на кодер 2, который в три этапа перекодирует ее в четыре последовательности. Из них далее блоки,3-6 задержки формируют четыое двоичных разрядных слова, которые поступают на мультиплексор 7.

Он поочередно коммутирует на выход каждое из слов, которое поступает в блок 8 памяти. На его выходах поочередно появляются многоразрядные числа, которые поступают на сумматор 10 непосредственно и через резистр 9 со сдвигом на один разряд влево. Далее числа записываются в регистр 11 и через ключ 12 поступают на ЦАП 13, преобразующий числа в отсчеты аналогового сигнала ° Затем фильтр 14 отфильтровывает в них побочные продукты преобразования. Даны ил. выполнения кодера 2, блока 15 управления и блока 16 формирования. 3 ил .

1598?O0

44k 4 4,-8

® а 44-7

k=0 1,2,3...

d4 ki 2 4 с+ +k-6

d Ф + Ь 4k+i fkОперация осуществляется с помощью у элемента задержки на двенадцать тактовых интервалов (регистров 18-20 и четырех сумматоров ?1-?4). Эта

Изобретение относится к техни ке связи и может использоваться в системах передачи данных по первичным широкополосным каналам связи.

Цель изобретения - повышение точности формирования.

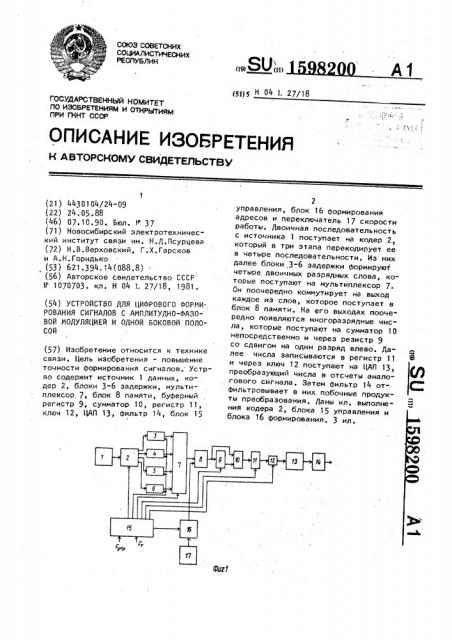

На Фиг. 1 изображена структурная электрическая схема предлагаемого устройства; на Фиг. 2 - ; 1p на Фиг. 3 - схема блока управления и блока формирования адресов.

Устройство содержит источник 1 данных, кодер 2, блоки 3-6, задержки, мультиплексор 7, блок 8 памяти, буферный регистр 9, сумматор 10,, регистр 11, ключ 12, цифроаналоговый преобразователь 13, фильтр 14, блок

15 управления, блок 16 формирования адресов, переключатель 17 скорости работы.

Кодер 2 состоит из регистров 1820 сдвига, сумматоров 21-28 по модулю два, буферного регистра 29.

Блок 15 управления состоит из счетчиков-делителей 30 и 31, дешифра- тора 32, элементов HE 33-35, элемента И-НЕ 36. одновибратора 37.

Блок 16 состоит из счетчиков 38 и

39, элемента 40 и постоянного запоминающего устройства 41.

Устройство работает следующим образом.

Двоичная последовательность а„ с выхода источника 1 поступает со скоростью V „нHа вBхxоoд кKоoд еeр а 22, который перекодирует ее в четыре последовательности Ъ ), Ь ), (CI,j, с, скорость следования V которых в четыре раза ниже скорости следова40 ния исходной последовательности 1а„ )

Процесс перекодирования осуществляется в три этапа. На первом этапе из исходной последовательности 1а„ ) образуется четыре последовательности 45 141 у )d<<„j, (Й fk, ), (d «+, ПО правилу операция необходима для устранения явления размножения ошибок, где знак

9 обозначает суммированию по модулю два. На втором этапе производится инвертирование каждого нечетного элемента подпоследовательностей

)d Id ф З s что необходимо для Формирования сигнала с амплитудно-фазовой модуляцией и одной боковой полосой. В результате образуется четыре подпоследовательности (b„), ь „,), (с„ 1, с„"j, b> =Ь +2Ь

f и

С> С„+ 2С„ (3) гДе b1,, bfI, С1„ С могут принимать значения 1 и значит представляют собой двоичные символы, а Сt, и Ь g

f где Ь = 1„„, (-1)

bg = d@g< (-1)", k=0,1,2,3,...

С = 4k+1 (-1)"

С1, = rk: (-1)" (2)

Инвертирование каждой из последовательностей осуществляется с помощью сумматоров 25-28,на один вход которого подаются символы одной из последовательностей, а на другой вход— управляющий сигнал (-1)" . Если значение управляющего сигнала - логическая единица, то символ подпоследовательности инвертируется, если логический ноль, - передается без изменения. На третьем этапе происходит запись полученных символов подпоследовательностей (Ь ), (Ь1,), (CI,I, (C>) в буферный регистр 29. Четыре символа подпоследовательностей, например, ц I u

Ь1, . Ь1,, С1,, С хранятся в нем до тех пор, пока на его входах не появится следующие четыре значения:

I 0 (li

Ь1,! ° " К. ° С К- с

Для нормальной работы на та ктовые входы кодера от блока 15 подаются частоты F, F тд,, F т/, Следует отметить, что в данном случае формируется многоуровневый сигнал с амплитудно-Фазовой модуляцией и одной боковой полосой путем получения значений синфазной Ь р и квадратурной С1, огибающих. Значения квадратурных огибающих связаны с последовательностями Ь, Ь, и С„, С следующим образом:

1598200 б могут принимать значения +1, +3 и представляют собой четырехуровневые символы.

С выхода кодера 2 символы подпоследовательностей jb ), Ъ1 ), С }, (С „ ) поступают соответственно на входы блоков 3-6. Число отводов в каждом иэ блоков задержки равно 2N. Сам блок задержки представляет собой последовательный регистр сдвига. На выходах блоков задержки, например блока 3, Формируется двоичное 2N разрядное слово, символы которого равны

I (I соответственно Ь,, bt, „, bg,, (°,,, Ь/ b1,«..., b>+ < Информация на выходах линий 4-6 задержки формируется аналогичным образом из подпоследовательностей (b ), (С, (с„ ) .

Четыре двоичных 2N разрядных слова с выходов блоков 3 - 6 поступают одновременно на входы мультиплексора 7. На управляющий вход мультиплексора подается с блока 15 двухбитовое слово, которое может иметь четыре . значения 00, 01, 10, 11. При этом

,в зависимости от значения управляющего слова на выход мультиплексора 7 коммутируется одно из четырех 2N разрядных слов, сформированных на выходах блоков 3 - 6. 1аким образом, на выходе мультиплексора 7 каждое из слов, полученных на выходах блоков

3-6, появляется поочередно через одну четвертую периода средней частоты формируемого спектра (Fgp).

С выхода мультиплексора 7 2N-разрядные слова подаются на младшие разряды адресных входов блока 8. В блоке 8 хранятся заранее рассчитанные отсчеты выходного сигнала Формирующего фильтра нижних частот (ФНЧ), представляющие собой свертку импульс" ной реакции ФНЧ с двоичной информационной последовательностью. Сигнал на выходе ФНЧ с импульсной реакцией

h(n) конечной длительности при подаче íà его вход синхронной последовательности, например Ь1,), описывается известным выражением ! й-<

B(t) = X Ь -h jt — (r + k)T j, (4) М™ где Т - длительность входного единичного импульса.

При этом отсчеты сигнала на выходе ФНЧ в моменты времени t = iÑ, где ь= —, i 0,1,2 3,..., могут э э е в ° ° е быть найдены из (4) как

5, М-

В(К) = Q Ь, „:h(i f.r- =-H (r + k)T) ° (5) Обычно в реальных системах пере" дачи данных значение средней частоты формируемого спектра F и скорость следования V соотносятся как простые числа

V С и — — — — т.е. = — т . (6) и

Т m m

С учетом этого обстоятельства выражение (5) можно записать в виде

<4-1

11

Ь h(i — Т—

g 3cir It1

В (i7) 25 (r + k)T). (7) Выражение i < = i — Т предста вим в

° л ° n

30 виде суммы двух компонент = КТ+-Т л 1

m (8) где К - целая часть от деления числа

1 (1n) m — — ocTRToK от деления числа (in) íà m, 1 =

= 0.1,2,...,m-1.

Тогда выражение (7) преобразуется к виду

s(i) = в(кт + — T) =

Ш

М-

1 — Ь h(KT + — Т— = -и "+"

И4

-rT — Кт) = b h(- т — rT).(9)

4+f m

Из выражения (9) видно, что отсчеты сигнала на выходе ФНЧ, взятые в моменты i i, могут принимать конечное

55 множество значений, которое определяется длиной линии задержки 2N и числом m, зависящим от соотношения скорости следования Ч и средней частоты спектра Рр. Количество возможных

1598200 значений отсчетов сигналов H(i f). составляет М = 2, так как принимает к только одно из двух значений +1 или

-1, а 1 = 0,1, °...m-1. Поэтому можно заранее с высокой точностью рассчитывать все M возможных значений сигнала B(i i) и записать их в блок памяти. Затем при формировании очередного значения В(il) = Г(Ъ1,„,Ъ 1, <"

Ь1,, Ь 1, 1 ) достаточно подать на адресные входы блока памяти двоичное слово 1Ь1 Ь1 1 f ° ° р Ь 1 Ь ..., b «) и двоичное слово 1.

Такйм образом, двухразрядные двоичные слова, появляющиеся íà выходе мультиплексора 7, подаются на младшие разряды адресных входов блока

8 памяти, на старшие разряды адресных входов которого подается двоичное число 1 с выхода блока 16.

В результате на выходах блока 8 поочередно появляются многоразрядные числа В,, Вт, С 1, С, где

"f 1

r=-H 1-1

Г=

И-f у - М

И-1

;> С „h (— — r) °

1= и (10) 35

В = В„+ 2В .

Это число В записывается в регистр

11. Затем с блока 8 на вход буферногс 55 регистра 9 подается число С,, запиcblBaeTcR в него и подается с задерж- кой на второй сумматор 10, где склаЧисла В 1, R С,, С с выхода блока 8 подаются на вход сумматора

10 и вход буферного регистра 9, причем на вход сумматора 10 эти числа

40 подаются со сдвигом на один разряд влево. На тактовый вход буферного регистра 9 с блока 15 подается сигнал записи в моменты появления чисел В„ и С1 пОЭТОму числО В 1 записывает ся в буферный регистр 9 и подается с задержкой на второй вход сумматора 10. В момент поступления на первый вход сумматора 10 числа В, (со сдвигом на один разряд) íà его выходах формируется число В, равное

50 дывается с числом С . В результате на выходах сумматора 10 появляется число С

С=С +2С

Число C также записывается в регистр 11. Регистр 11 необходим для задержки числа В на одну четвертую периода частоты F . Выход регистра

11 соединен с входом ключа 12. Ключ

12 в соответствии с управляющим сигналом с блока 15 подает на цифроаналоговый преобразователь 13 сначала число В, затем через одну четвертую

Э периода частоты F t число С, затем через период частоты F следующее число В;, и т.д. Длительность подачи чисел на цифроаналоговый преобразователь 13 не превышает 200-300 нс, Цифроаналоговый преобразователь 13 преобразует числа В и С в отсчеты аналогового сигнала длительностью

200-300 нс. Выход цифроаналогового преобразователя 13 соединен с входоя

Фильтра 14, который отфильтровывает побочные продукты преобразования, 1

При передаче по первичному широкополосному каналу связи используется ряд стандартных скоростей. Конкретная скорость передачи выбирается переключателем 17, который подает на блок 16 двухразрядное слово: 00, 01, 10, 11, которое определяет, какая из скоростей следования V используется: 24, 32, 38 или 48 кБод. Это же слово подается на синтезатор частот (не показан), с которого на блок

15 подается одна из четырех тактовых частот F : 96, 128, 144 или 192 кГц и частота управления F „р, равная

672 кГц. Блок 16 формирования адре,сов состоит из последовательно соединенных счетчика, на вход которого подается частота F, равная 84 кГц, с блока 15, а на выходах появляются pЭ числа от 0 до m-1 (в данном случае

21), и постоянного запоминающего устройства. На постоянное запоминающее устройство блока 16 также подает.ся двухрахрядное слово с выхода переключателя 17 и сигнал с блока 15, который определяет, какое число выдавать на выходе блока 16. Блок 15, обеспечивает согласованную работу всех блоков устройства.

8200

9 159

Формула изобретения устройство для цифрового формиро. вания сигналов с амплитудно-фазовой модуляцией и одной боковой полосой, содержащее источник данных, первый и второй блоки задержки, блок памяти, сумматор, цифроаналоговый преобразователь, выход которого соединен с входом фильтра, выход которого является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности формирования, введены кодер, третий и четвертый блоки задержки, блок управления, мультиплексор, переключатель скорости работы, блок Формирования адресов, буферный регистр, регистр и ключ, причем выход источника соединен с входом кодера, выходы которого через соответствующие блоки задержки соединены с входами мультиплексора, выход которого соединен с младшими разрядами адресных входов блока памяти, выход которого соединен с входом буферного регистра и первым входом сумматора, выход которого через последовательно соединенные регистр и ключ соединен с входом цифроаналогового преобразователя, выход переключателя скорости работы соединен с входом блока формирования адресов, 10 выход которого соединен со старшими разрядами адресных входов блока памяти, выход буферного регистра сое" динен с вторым входом сумматора, выходы блока управления соединены со15 ответственно с тактовым входом кодера, тактовыми входами блоков задержки, управляющим входом мультиплексора, тактовым входом буферного регист. ра, тактовым входом регистра, управ- ляющим входом ключа, управляющим входом блока формирования адресов, входы блока управления являются управляющим и тактовым входами устрой. ства.

0m

17

Составитель Н.Лазарева

Редактор С.Пекарь Техред М.Моргентал корректор В.Гирняк

Заказ 3072 Тираж 528 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СЧСР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, r Ужгород, ул.. агарина, I t 1!

101