Устройство для сложения и вычитания чисел по модулю

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах и устройствах, функционирующих в системе остаточных классов. Целью изобретения является сокращение аппаратурных затрат. Устройство для сложения и вычитания чисел по модулю содержит первый информационный вход 1 устройства, вход 2 задания сложения устройства, дешифратор 3, кольцевой регистр 4 сдвига, блок 5 элементов И, шифратор 6, вход 7 задания вычитания устройства, выход 8 устройства, второй информационный вход 9 устройства, элемент 10 запрета, вычитатель 11 по модулю, вход 12 задания модуля устройства, блоки 13 и 14 элементов И, блок 15 элементов ИЛИ, приемный регистр 16, схему 17 сравнения, счетчик 18, тактовый вход 19 устройства. 1 ил.

А1

СОКИ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 5 G 06 F 7/72

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И OTHPbA ÈßÌ

ПРИ 1ННТ СССР (21) 4470192/24-24 (22) 02.08.88 (46) 15.10.90. Бюл. Р 38 (72) В.И.Глушков, В.И.Долгов, В.А.Краснобаев, И.В. Кононова и А.И.Сахно (53) 681.325.5(088.8) (56) Авторское свидетельство СССР

У 1388850, кл. G 06 F 7/49, 1986.

Авторское свидетельство СССР

9 1532923, кл. G 06 F 7/72, 24. 05.88. (54) УСТРОЙСТВО ДПЯ СЛОЖЕНИЯ И ВЫЧИТАНИЯ ЧИСЕЛ ПО МОДУЛЮ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах и устройствах, функционирующих в систе2 ме остаточных классов. Целью изобретения является сокращение аппаратурных затрат. Устройство для сложения и вычитания чисел по модулю содержит первый информационный вход 1 устройства, вход 2 задания сложения устройства, дешифратор 3, кольцевой регистр 4 сдвига, блок 5 элементов И, шифратор 6, вход 7 задания вычитания устройства, выход 8 устройства; второй информационный вход 9 устройства, элемент 10 запрета, вычитатель 11 по модулю, вход 12 задания модуля устройства, блоки 13 и 14 элементов И, блок 15 элементов ИЛИ, приемный регистр 16, схему 17 сравнения, счетчик 18, тактовый вход 19 устройства. 1 ил.

1599857

Изобретение относится к автбматике и вычислительной технике и может быть использовано в системах и устройствах, функционирующих в системе остаточных классов (СОК).

Целью изобретения является сокращение аппаратурных затрат.

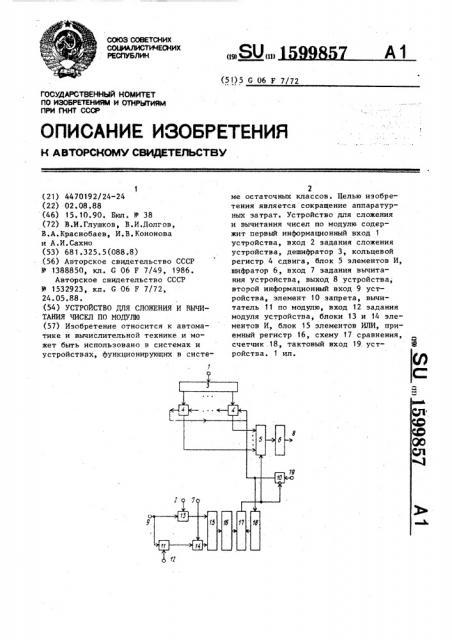

На чертеже представлена схема устройства дпя сложения и вычитания чи- . 10 сел по модулю.

Устройство содержит первый информационный вход 1 устройства, вход

2 задания сложения устройства, дешифратор 3, кольцевой регистр 4 сдвига, первый блок 5 элементов И, :,шифратор 6, вход 7 задания вычитания устройства, выход 8 устройства, второй информационный вход 9 устройства, элемент 10 запрета, вычитатель

11,по модулю, вход 12 задания модуля устройства, второй и третий блоки

13 и 14 элементов И, блок 15 элементов ИЛИ, приемный регистр 16, схему

17 сравнения, счетчик 18, тактовый 25 вход 19 устройства.

Дешифратор 3 служит для преобразования первого операнда А из двоич. ного кода в унитарный, шифратор 6для преобразования унитарного выходного кода регистра 4 в двоичный код результата операции.

Устройство работает следующим образом.

На первый вход 1 подается операнд А, а на второй вход 9 — операнд

В. С выхода дешифратора 3 .операнд

А в унитарном коде поступает на А-й двоичный разряд регистра 4, записывая "единицу" в данном разряде (ис40 ходное состояние разрядов регистра 4 - нулевое), Второй операнд В по" ступает на вход вычитаемого вычитателя 11. В зависимости от типа реали- зуемой операции операнд В (операция 45 сложения) или операнд в3 = m — В (операция вычитания, ш - значение модуля) через блок 15 элементов ИЛИ поступает на вход регистра 16. С началом работы импульсы с входа 19 через открытый элемент 10 запрета поступают на вход счетчика 18 и на вход разрешения сдвига регистра 4, сдвигая исходное содержимое его на В (либо В) двоичных разрядов в положи55 тельном (против часовой стрелки) направлении. При наличии в счетчике

18 значения В (либо В) выходной сигнал схемы 17 сравнения закрывает элемент 10 запрета, прекращая подачу импульсов на счетчик 18 и регистр

4, и открывает блок 5 элементов И.

Далее содержимое регистра 4 (полученный код) через открытые элементы

И блока 5 поступает на вход шифратора 6, с выхода .которого значение. результата операции в двоичном коде поступает на выход 8 устройства.

Рассмотрим пример конкретной реализации модульных операций для m=5.

Исходное состояние регистра 4 следующее:

Пусть А = 3, В = 4, Необходимо определить (А + B)mod 5.

Первый операнд А = 0.11 заносится на вход 1. Второй операнд В = 100 заносится на вход 9 и далее через открытый (присутствует сигнал входа 2) блок 13 элементов И, через блок 15 элементов ИЛИ поступает s регистр 16.

С третьего выхода дешифратора 3 сигнал переводит третий двоичный раз« ряд (разряды регистра 4 нумеруются с нулевого.до (m-1) -ro справа налево) в единичное состояние. Содержимое регистра 4 будет иметь следующий вид

С входа 19 импульсы через открытый элемент 10 запрета поступают на вход счетчика 18 и на вход разрешения сдвига регистра 4, сдвигая в положительном направлении исходное содержимое регистра 4 на четыре двоичных разряда. В этом случае содержимое регистра 4 будет иметь следующий вид:

Когда в счетчике 18 будет находиться величина В = 100, схема 17 сравнения выдает сигнал "Равенство", кото" рый закрывает элемент 10 запрета и открывает блок 5 элементов И, через который код 00100 с выхода разрядов регистра 4 поступает на вход .шифратора 6, с выхода которого значение

010 поступает на выход 8.

Формула изобретения

Устройство для сложения.и вычитания чисел по модулю, содержащее деСоставитель А. Клюев

Техред М..Дидык Корректор Н. Ревская

Редактор А.Маковская

Заказ 3144 Тираж 566 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

5 15998 шифратор, кольцевой регистр сдвига, первый, второй и третий блоки элементов И, шифратор, элемент запрета, вычитатель по модулю, блок элементов

ИЛИ, приемный регистр, схему сравнения и счетчик, причем первый информационный вход устройства соединен с входом дешифратара, выходы мпадших разрядов кольцевого регистра сдвига соединены с входами соответствующих разрядов первого, входа первого блока элементов И, второй вход которого соединен с управляющим входом элемента запрета и с выходом схемы сравнения, первый и второй входы которой соединены соответственно с выходами приемного регистра и счетчика, вход которого соединен с выходом элемента запрета, информационный вход кото- 20 рого соединен с тактовым .входом устройства, второй информационный вход которого соединен с первым входом второго блока элементов И и с входом вычитаемого вычитателя по модулю, вход 25 уменьшаемого и выход которого соеди57 6 иены соответственно с входом задания модуля устройства и с первым входом третьего блока элементов И, . входы задания сложения и вычитания устройства соединены соответственно с вторыми входами второго и третьего блоков элементов И, выходы которых соединены соответственно с первым и вторым входами блока элементов ИЛИ, отличающееся тем, что, с целью сокращения аппаратурных saтрат, выходы дешифратора соединены с входами соответствующих разрядов кольцевого регистра сдвига, выходы старших разрядов которого соединены с входами соответствующих разрядов первого входа первого блока элементов И, выход которого соединен с .входом шифратора,. выход которого является выходом устройства, выход элемента запрета соединен с входом разрешения сдвига кольцевого регистра сдвига, выход блока элементов ИЛИ соединен с входом приемного регистра.