Устройство для обмена данными в вычислительной сети

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в локальных вычислительных сетях в качестве устройства для обмена данными между локальными станциями сети и вычислительными средствами каждой локальной станции. Целью изобретения является расширение области применения и повышение достоверности функционирования сети за счет обеспечения возможности инициализации процедуры обмена и контроля передачи данных. Поставленная цель достигается тем, что в устройство, содержащее процессор 1, системный контроллер 2, блок приоритетного прерывания, блоки постоянной и оперативной памяти, генератор 6 тактовых импульсов, блок 7 синхронизации связи, дешифратор управления, блок анализа состояния, введены блок 22 контроля времени ожидания ответа, блок 23 контроля времени связи, блок контроля времени ожидания обмена, блок шинных формирователей и элемент И. 6 ил.

союз советсних социАлистичесних

РЕСГВБЛИН (51)5 С 06 F 13 12

ОЛИСАНИЕ ИЗОБРЕТЕНИЯ

К A ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОсудАРстВенный нОмитет

AO ИЗОБРЕТЕНИЯМ И OTHPblTHRM пРи п4нт сссР (21) 4621425/24-24 (22) 15.12.88 (46) 15.10.90. Бюл . И 38 (71) Харьковское научно.-производственное объединение по системам автоматизированного управления (72) А.В.Веселов, В.В.Герасименко, Н.И.Сорокин, Г.Н.Тимонькин, С.Н.Ткаченко, В.В.Топорков и В.С.Харченко (53) 681. 325 (088. 8)

{56) Мартин Дж. Вычислительные сети и распределенная обработка данных.

Вып. 2. М.: Финансы и статистика, 1986.

Авторское свидетельство СССР

Р 1432537, кл. G 06 Р 13/!2, 1987.

„„Я0„„1599864 А1

2 (54) УСТРОЙСТВО ДЛЯ ОБМЕНА ДАННЬЙЯ1

В ВИЧИСИИТЕЛЬНОИ СЕТИ (57) Изобретение относится к вычиспительной технике и может быть использовано в локальных вычислительных сетях в качестве устройства для обмена данными между локальными станциями сети и вычислительными средствами каждой локальной станции. Цепью изобретения является расширение области применения и повышение достоверности функционирования сети sa счет обеспечения возможности инициализации процедуры обмена и контроля передачи данных. Поставленная цель достигается тем. что в устройство, 1599864 содержащее процессор 1, системный контроллер 2, блок приоритетного прерывания, блоки постоянной и оперативной памяти, генератор 6 тактовых импульсов, блок 7 синхронизации связи, дешифратор управления, блок аналиИзобретение относится к вычислительной технике и может быть использовано в локальных вычислительных сетях в качестве устройства для обмена данными межцу локальными станциями сети и вычислительными средствами каждой локальной станции.

Целью изобретения является расширение области применения устройства 20 и повышение достоверности функционирования сети за счет обеспечения контроля передачи данных и возможности инициализации процедуры обмена.

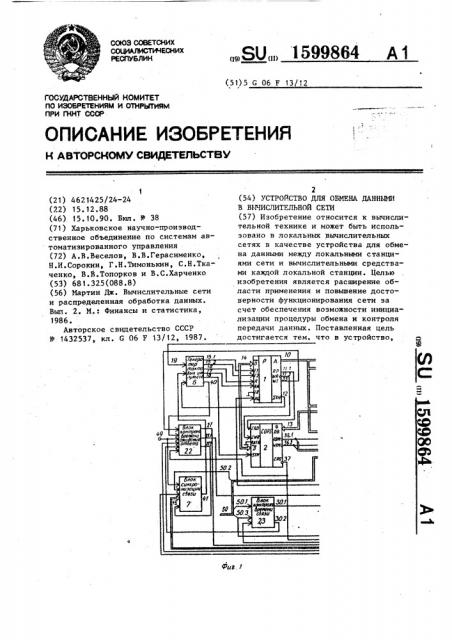

На фиг.1 и 2 приведена структур- 25 ная схема устройства для обмена в вычислительной сети; на фиг.3 — пример реализации блока контроля времени ожидания ответа; на фиг.4 — то же, блока контроля времени связи;на фиг.5-30 то же, блока контроля времени ожидания обмена; на фиг.6 — то же, блока шинных формирователей.

Устройство для обмена данными в вычислительной сети (фиг.1-2) содержит процессор 1, системный контроллер 2, блок Зприоритетного прерывания, блоки постоянной 4 и оперативной 5 памяти, генератор 6 тактовых импульсов, блок 7 синхронизации связи, дешифратор 8 управления, блок 9 анализа состояния канала, группу 10 адресных выходов, в том числе первого 10.1 и второго 10.2 разрядов, двенадцатого 10.3, тринадцатого 10.4, четырнадцатого 10.5.и пятнадцатого

10.6 разрядов, выходы управления 11.1 чтением, 11.2 записью и 12 синхронизации процессора, шину 13 данных устройства, информационную, связь 14, 0 первый-пятый 15. 1, 15.2, 16-18 выходы генератора 6 тактовых импульсов, шину 19 начальной установки, внешнюю интерфейсную магистраль 20, первый разряд 21.1, второй разряд

21.2 группы 21 выходов блока 9 анализа состояния канала, блок 22 контроля времени ожидания ответа, блок 23 контроля времени связи, блок 24 контза состояния, введены блок 22 контроля времени ожидания ответа, блок

23 контроля времени связи, блок контроля времени ожидания обмена, блок шинных формирователей и элемент И.

6 ил. роля времени ожидания обмена, блок

25 шинных формирователей, элемент

И 26, первый-третий 27, 28. 1, 28.2 выходы блока 22 контроля времени ожидания ответа, шину 29 адреса, первый

30.1 и второй 30.2 выходы блока 23 контроля времени связи, выход 31 блока 24 контроля времени ожидания обмена, группы выходов адресных 32, управления 33 и входов-выходов данных 34 блока 25 шинных формирователей, выход 35 подтверждения ожидания процессора 1,выходы чтения 36.1 и записи 36.2 системного контроллера 2, выход 37 подтверждения приема запроса прерывания системного контроллера

2, группу 38 входов-выходов данных блока 3, выход 39 запроса на преры-, вание блока 3, выход 40 установки генератора 6, выход 41 блока 7 синхронизации связи, первый 42, второй

43.1,третий 43.2, четвертый 44 и пятый 45 выходы дешифратора 8,группу

46 управляющих выходов устройства, управляющий выход 47 блока 9, входвыход 48 данных устройства, вход 49 блокировки ответа устройства, первый 50.1, второй 50.2, третий 50.3 разряды группы входов 50 устройства, старшие разряды 51, шину 52 ответа внешней интерфейсной магистрали 20.

Блок 22 контроля времени ожидания ответа (фиг.3) содержит триггер 53, первый 54, второй 55 элементы И, эле" менты И-НЕ 56, 57, диод 58 и конденсатор 59.

Блок 23 контроля времени связи (фиг,4) содержит первый 60 и второй

61 триггеры, таймер 62, элемент HE 63, транзистор 64, конденсатор 65, резисторы 66 и 67.

Блок 24 контроля времени ожидания обмена (фиг.5) содержит таймер 68, элемент HE 69, транзистор 70, конденсатор 71, резисторы.72 и 73.

Блок 25 шинных формирователей (фиг.6) содержит первый 74 и второй зона буфера передачи в канал связи ю эона буфера приема из канала связи; зона дополнительного буфера приема из канала связи.

Генератор 6 тактовых импульсов предназначен для формирования двух непересекающихся во времени последовательностей тактоных импульсов, необходимых для работы процессора 1, синхронизации выдачи на процессор 1 сигналов сброса и готовности, а также

75 блоки магистральных элементов, первый 76 и второй 77 магистральные элементы.

Процессор 1 предназначен для управления обменом данными и управляющей информацией в устройстве в соответствии с заданным сетевым протоколом и обработки сигналов прерывания от блоков контроля.

Системный контроллер 2 предназначен для сохранения информации о работе, выполняемой процессором 1 в течение машинного цикла, а также для управления отдельными элементами системы устройства.

Блок 3 предназначен для обеспечения организации обмена информацией в режиме прерывания от блоков контроля устройства и в процессе приема информации, Блок 3 позволяет осуществлять простой приоритетный режим прерыванИя, йри реализации которого всем входам запросов на прерывание приснаиваются фиксированные приоритеты.

Постоянное запоминающее устройстso 4 предназначено для хранения программ, определяющих работу устройства при обмене данными в вычислительной сети.

Оперативное запоминающее устройство 5 предназначено для хранения текущей передаваемой и принимаемой информации. В ОЗУ 5 подразумевается несколько зон. Распределение информации по зонам может быть следующим: эона конфигурации вычислительной сети, включающая список собственных адресов устройств для .обмена данными, аналогичных заявляемому, которые подключаются к локальной сети; зона байтов состояния канала, передачи, приема, завершения приема; эона рабочих ячеек;

99864 6 формирования стробирующих сигналон состояния и синхронизации.

Блок 7 предназначен для формирова5 ния сигнала готовности.на основе входных управляющих сигналон от элементов устройстна.

Дешифратор 8 предназначен для формирования сигналов управления элемен10 тами устройства.

Блок 9 предназначен для управления работой элементов устройства для обмена данными и связанного с ним приемопередатчика с учетом состояния какала (наличия ипи отсутствия в нем информации).

Блок 22 предназначен для обеспечения контроля работоспособности приемопередатчика по времени ожида20 ния от него ответа процессором 1, а также для формирования сигналов управления приемопередатчиком, блоком

7 синхронизации связи и блоком 3 приоритетного прерывания.

25 Блок 23 предназначен для контроля отказа передатчика по непрерывной генерации данных в линию связи (превышение допустимого времени связи}.

Блок 25 предназначен для управле3О ния выдачей и обменом соответственно адресных, управляющих сигналов и данных с учетом входных сигналов управления.

Устройство работает следующим об35

Обмен информацией н сети между локальными станциями организован в виде циклов, под которыми понимается процедура передачи в канал связи одной посылки информации (сообщения). Несколько взаимосвязанных циклов образуют процесс передачи, который в общем случае организуется по асинхронному принципу. Это оэнача 5 ет, что на посылаемые в канал связи вызовы устройство должно получать ответы.. При обмене данными между локальными станциями в сети реализуется, например, интерфейс ИРМ

5О (ГОСТ 26139-84. Интерфейс для АСУ рассредоточенными объектами). В этом случае передача информации между локальными станциями осущестнялется посредством ограниченного набора байтов, порядок следования которых устанавливается форматом сообщения. Устрой- ство может выполнять несколько сетевых функций, код которых задается в формате сообщений байтом, содержащим.

1599864 информацию о виде сообщения, признаке занятости локальной станции, " типе формата сообщения, признаке по вторения передачи.

Локальной станцией могут выполняться следующие функции, которые оп ределяют ее место на соответствующем уровне передачи управления в сети: прием — ответ централизованное упЭ 1О равление.

При выполнении соответствующей функции локальная станция считается

BKTHBHOH OTHOCHTBJlbHO STOA функции.

В зависимости от функций, выполняемых устройством в данный момент времени, различают три следующих типа состояний локальных станций: управляемая подсистема", инициативная уп" равляющая подсистема; ведущая подсистема.

Переходы между состояниями локальных станций осуществляются в соответствии с принятым алгоритмом обмена данными в сети. В состоянии управ- 25 ляемая подсистема" осуществляется прием адресованных устройству сообщений и формирование ответных сообщений в соответствии с кодом реализуемой сетевой функции. В состоянии

"Инициативная управляющая подсистема" устройства могут принимать управление обменом по каналу связи, формировать и передавать сообщения, принимать и анализировать ответные сообщения, а также возвращать управление по окончании процесса передачи.

В состоянии "Ведущая подсистема" устройство осуществялет координацию работы всех устройств, подключенных к 4 каналу связи. При этом ведущее устройство может передавать управление другому устройству и контролировать работу инициативного управляющего устройства. Координация взаимодейст- 45 вия локальных станций сети осуществляется ведущим устройством сети путем выполнения функций передачи и возврата управления. При передаче управленчя ведущее устройство назначает одно из числа имеющихся в сети активным управляющим устройством для передачи сообщения. Для этого ведущее устройство направляет выбранной локальной станции сообщение

"Передача управления каналом". После приема сообщения выбранная станция может выполнять один цикл обмена в одной процедуре передачи, По окончании процесса передачи инициативная управляющая станция выполняет функцию возврата управления, для чего она направляет ведущему устройству сообщение "Возврат управления каналом". Передача управления может осу-1 ществляться только по инициативе ведущей системы. Процедура передачи данных осуществляется при выполнении сетевой функции "Запись". При этом ведущее устройство или инициативное управляющее устройство формирует посылку в канал связи сообщения с функцией "Запись", которое адресуется конкретной локальной станции.

Адресуемое устройство производит опознавание собственного адреса в сообщении и выдает в канал связи сообщение "Подтверждение приема сообщения". После выдачи сообщения выдавшее его устройство осуществляет программный отсчет контрольного интервала времени в ожидании ответного сообщения. При отсутствии ответа по истечении контрольного интервала передающая станция осуществляет трехкратную повторную передачу того же сообщения. В случае отсутствия ответа после трехкратной пересынки адресуемое устройство считается отказавшим. Во время обмена с адресуемым устройством ведущая станция выполняет функцию пассивного приема сообщений.

Основными режимами работы устройства являются начальный запуск и прием-передача (обмен) данных.

В режим начального запуска система переходит при поступлении с интерфейсной магистрали 20 по шине 19 сигнала установки на вход генератора 6 тактовых импульсов,с выхода .16 которого сигнал поступает на вход начальной установки микропроцессора

1. При этом обнуляются его программный счетчик команд, внутренние триггеры разрешения прерывания и захвата шин. После этого процессор 1 переходит к реализации программы начального запуска. По сигналу с выхода 40 генератора 6 тактовых импульсов элементом И 55 формируется низкоуровневый сигнал "Сброс" приемопередатчика, который с выхода 27 поступает на одноименную линию шины

46 для перевода приемопередатчика в исходное состояние. В процессе выполнения программы начального запу1599864!

О ска в ОЗУ 5 происходит очистка списка адресов локальных станций, байтов состояния, сброс байтов готовности, настройка блока 3 приоритетного прерывания, после чего устройство считается готовым к обмену информацией.

Далее устройство осуществляет реализацию процедур по обмену информацией с модуляьж ввода-вывода, подключенными к нему через магистраль О, и ! о с другими локальными станциям через канал связи. При этом контролируется работоспособность собственных средств передачи информации и других станций в сети (в частности, ведущей), В локальной вычислительной сети только-одно устройство может быть ведущим и осуществлять управление каналом связи. Все остальные устройства, входящие в сеть, являются пассивнымн и активизируются после передачи им управления. Любое устройство, входяmee в сеть, осуществляет анализ информации, циркулирующей в канале свя- 25 зи, с целью обнаружения адресованного ему сообщения. Выполнение этой функции реализуется следующим образом.

В случае наличия информации в канале связи одна из линий группы 51 входов блока 9 анализа состояния канала возбуждается, что приводит к фор" мированию сигнала прерывания на линии 21.1, который поступает на вход

- 35 блока 3, что вызывает на его выходе

39 формирование сигнала прерывания, который подается на одноименный вход процессора 1., Процессор 1 на шине

14 формирует код слова состояния, а на выходе 11.1 — сигнал "Чтение".

Это вызывает формирование на выходе

37 системного контроллера 2 c :òíàëà подтверждения прерывания, поступающего на одноименный вход блока 3. 45

Храме того, сигнал с выхода 37 системного контроллера 2 подается на вход блока 22. Блок 3 по шине 38 на шину 13 данных устройства выдает команду вызова программы обслуживания данного прерывания. По сигналу же подтверждения прерывания с выхода

37 системного контроллера 2 в блоке

22 осуществляется формирование сигнала, который с выхода 28.2 поступает на вход блока 7 и на ега выходе формирует сигнал готовности, пасту" лающий на вход генератора 6. На выходе 17 генератора формируется однаименный сигнал, поступающий на вход готовности процессора 1. После этога процессор 1 считывает команду вы° зава и приступает к выполнению об, служивающей программы. При обращении к приемопередатчику па адресу, выставленному на шине 10 процессором 1, дешифратором 8 управления формируется на выходе 43. 1 сигнал обращения к внутренним элементам системы, после чего блоком 9 анализа состояния канала вырабатывается сигнал чтения регистра состояния приемопередатчика. Сигнал с выхода 43.1 дешифратара 8 управления, кроме того, поступает на блок 22 связи. На выходе элемента И 5 формируется высокий потенциал (так как в режиме обмена сигнал на входе 49 имеет высокий уровень). В случае превышения времени ожидания ответа от приемопередатчика на сигнал обращения к нему процессора 1 происходит заряд конденсатора 59 и на выходе элемента 56 формируется сигнал низкого уровня, устанавливающий триггер 53 в единичное состояние, что вызывает формирование Hà его единичном выходе высокоуровневого сигнала прерывания, который с вьгхода 28.1 блока 22 поступает на блок 3. После этого устройство переходит к обслуживанию поступившего запроса на прерывание. Сигналом подтверждения прерывания с выхода 37 системного контроллера 2 триггер 53 устанавливается в нулевое состояние. Сигнал обращения к внутренним элементам устройства, поступающий с линии группы 43 входов блока

7 синхронизации связи вместе с сигналом готовности приемопередатчика„ поступающим по линии 50,2, вызывают формирование на выходе 4 1 блока 7 синхронизации связи сигнала готовности приемоперецатчика для обмена, который поступает на вход генератора 6 тактовых импульсов. Это, в свою очередь, вызывает формирование генератором на выходе 17 импульсов, поступающих на вход процессора 1.

После этого процессор 1 считывает состояние приемопередатчика и данные от него.

После выбора адресованного сообщения устройство контролирует правильность приема сообщения и када функции. При неправильном приеме информации система переходит к выполнению .

99864 12

20 !

II 15 алгоритма анализа состояния канала связи. Если же информация принята правильно и получено сообщение с кодом функции "Запись", то устройство осуществляет анализ занятости буфера приема из канала связи. Если буфер свободен, то устройство осуществляет передачу в канал ответного сообщения с кодом "Подтверждение" и установленным признаком готовности по приему. Передача информации от заявляемого устройства в канал связи осуществляется аналогично приему. Меняется только направление передачи путем формирования процессором 1 соответствующих адресных разрядов на шине 10 и сигнала "Запись" на выходе 11.2, поступающего на системный контроллер 2, который вырабатывает управляющие сигналы блоком

9 анализа состояния канала. При приеме информации из канала и ее передаче блоком 22 непрерывно осуществляется контроль работоспособности приемопередатчика по заданному времени ответа от него. Если буфер приема из канала связи занят, то устройство передает в канал связи ответное сообщение с признаком занятости буфера и переходит к реализации алгоритма анализа состояния канала связи. Поскольку в каждом устройстве, входящем в сеть, задается собственный код времени ожидания перехода в ре-. жим ведущего устройства, то при отсутствии информации в канале связи по истечении интервала времени ожидания, отслеживаемого программно, осуществляется переход к реализации программы ведущего устройства. При выполнении программы ведущего устройства организуется передача управления каждой локальной станции,входящей в список конфигурации сети, хранящийся в соответствующей зоне

ОЗУ 5, и контролируется информация из канала связи. Если в канале связи информация отсутствует, то есть ни одна из локальных станций сети не отвечает на передачу управления, то ведущее устройство снимает с себя функции ведущего и переходит к реа" лизации программы анализа состояния канала связи аналогично описанному выше. При этом программа анализа состояния канала связи выполняется до тех пор, пока в канале не появится информация либо не истечет интер25

S0

55 вал времени ожидания перехода к функции ведущего. Если в канале связи присутствует информация с кодом функции передачи управления, то устрой-, ство формирует в ответ код функции возврата управления и переходит на выполнение программы инициативной управляющей или управляемой системы.

Организация связи устройства с модулями ввода-вывода, подключенными к нему через магистраль 20,осуществляется следующим образом.

Процессор 1 на шине 10 формирует адрес обращения к соответствующему модулю ввода-вывода. При этом передаются высокие потенциалы соответственно на входы 10.2-10.5, что вызывает формирование на выходе 43.2 дешифратора 8 управления низкоуровневого сигнала обращения к внешним элементам, который управляет блоками

25 шинных формирователей и 7 синхронизации связи. В зависимости от выполняемой процессором 1 операции по приему или выдаче информации в модули ввода-вывода на соответствующих его выходах (11.1 или 11.2) формируются сигналы управления, на основании которых системным контроллером

2 определяется направление передачи информации и вырабатываются на выходах 36.1 или 36.2 одноименные сигналы управления, поступающие на входы блока шинных формирователей, инициируя при этом передачу или прием информации в/из модулей ввода-вывода. После идентификации сигнала обращения устройство ввода-вывода, распознавшее его, формирует сигнал "Ответ", который по линии 52 интерфейсной магистрали 20 поступает на вход блока 7 синхронизации связи. При этом на его выходе формируется сигнал готовности, который поступает на соответствующий вход генератора 6 и инициирует формирование на его выходе 17 сигнала готовности, который поступает на одноименный вход процессора 1, оповещая его о возможности считывания (выдачи) данных с/на шину 13 данных.

При передаче данных в канал связи устройство осуществляет контроль работоспособности передатчика путем отслеживания продолжительности кванта передачи. Информация о начале работы передатчика поступает в систему по линии 50.3 группы входов 50 приемопередатчика. Если воемя работы передат 3 159 чика превысит допустимое время цикла передачи информации, то конденсатор

65 успеет зарядиться до высокого уровня сигнала, превышающего уровень срабатывания таймера 62 по пороговому входу. На выходе таймера сформируется импульс низкого уровня, длительность которого определяется временем разряда конденсатора 65. Сформированный низкоуровневый сигнал с выхода 30.2 блока 23 контроля времени связи поступает на вход блока 22 и вызывает формирование сигнала "Сброс" приемопередатчика. Кроме того, импульс с выхода таймера 62 инвертируется элементом HE 63 и поступает на синхровход триггера 61, устанавливая его в нулевое состояние и формируя тем самым на выходе 30.1 блока 23 сигнал прерывания процессора 1 по превышению передатчиком допустимого време- ни передачи в канал связи. Работа системы по обслуживанию прерывания происходит аналогично описанному выше. После восприятия сигнала прерывания процессор 1 переходит к выполнению программы обслуживания данного типа прерываний.

Если же время работы передатчика не превысило допустимое, то никакие сигналы блоком 23 не формируются и устройство функционирует в соответствии. с программами, хранимыми в блоке 4 ПЗУ, и информацией, записанной в соответствующих зонах ОЗУ 5.

Кроме описанного вида контроля в устройстве реализован контроль времени ожидания очередного цикла обмена по каналу связи. По окончании работы передатчика на линии 56.3 устанавливается сигнал низкого уровня, инвертируемый элементом НЕ 69 блока

24. Сигнал высокого уровня с выхода элемента НЕ 69 поступает на вход пуска таймера 68 и базу транзистора 70.

Конденсатор 7 1 начинает заряжаться.

Время его заряда рассчитано на время начала очередного цикла обмена информацией по каналу связи заявляемой системы с другими станциями. Если очередной цикл обмена будет инициирован несвоевременно, например возник тупик при организации взаимодействия между локальными станциями сети, то конденсатор 71 успеет зарядиться до порогового уровня и на выходе таймера 68 будет сформирован ниэкоуровне9864

15

55 вый сигнал прерывания, поступающий с выхода 31 блока 24 контроля времени ожидания обмена на вход блока 3 приоритетного прерывания. Обслужива-, ние данного запроса на прерывание осуществляется так же, как было описано выше. В том случае, когда очередной цикл обмена начинается своевременно, с включением передатчика изменяется уровень сигнала на линии

50.3 и блок 24 не формирует сигнал прерывания.

Формула изобретения

Устройство для обмена данными в вычислительной сети, содержащее процессор, системный контроллер, блок приоритетного прерывания, блоки постоянной и оперативной памяти, генератор тактовых импульсов, блок синхронизации связи, дешифратор управления, блок анализа состояния канала, причем группа адресных выходов процессора соединена с одноименными входами группы блоков постоянной и оперативной памяти, выход первого разряда группы адресных выходов процессора соединен с одноименным входом блока приоритетного прерывания, выходы первого и второго разрядов группы адресных выходов процессора соединены с одноименными входами бло- ка анализа состояния канала, выходы двенадцатого и тринадцатого разрядов группы адресных выходов процессора соединены с первым и вторым соответственно входами дешифратора, выходы управления чтением, записью и синхронизации процессора соединены соответственно с входами чтения, записи системного контроллера и с входом синхронизации генератора тактовых импульсов, первый вход-выход данных си . стемного контроллера через одноименную шину соединен с входами-выходами данных блоков постоянной памяти, оперативной памяти, приоритетного прерывания и входом-выходом данных устройства, второй вход-выход данных системного контроллера соединен с входом-выходом данных процессора, выходы с первого по пятый генератора соединены соответственно с первым и вторым синхровходамн, входами сброса и готовности процессора и входом синхронизации системного контроллера, выход второго разряда кода прерывания

15 159986 группы выходов блока анализа состояния соединен с входом третьего разряда запроса прерывания блока приори4 тетного прерывания, вход начальной установки генератора тактовых импульсов соединен с одноименной шиной внешней интерфейсной магистралью и является входом устройства, о т л ич а ю щ е е с я тем, что, с целью расширения области применения и повышения достоверности функционирования сети путем обеспечения возмож" ности инициализации процедуры обмена и контроля передачи данных, в него введены блоки контроля времени ожидания ответа, контроля времени связи, контроля времени ожидания обмена, шинных формирователей и элемент И, причем выходы с первого по 3) третий блока контроля времени ожидания ответа соединены соответственно с выходом сброса устройства, с входом первого разряда запроса прерывания блока приоритетного прерывания и с 25 первым информационньм входом блока сихронизации связи,.первый и второй выходы блока контроля времени связи соединены соответственно с входом четвертого разряда запроса прерывания, gg блока приоритетного прерывания и первым информационным входом блока контроля времени ожидания ответа, выход блока контроля времени ожидания обмена соединен с входом пятого разряда запроса прерывания блока приоритетного прерывания, выходы адреса, входы-выходы данных и выходы управления блока шинных формирователей являются входами-выходами устройства, выход подтверждения ожидания процес- сора соединен с вторым информационным входом блока контроля времени ожидания ответа, выход чтения системного контроллера соединен с первым входом режима блока шинных формирователей, входом чтения блока постоянной памяти, входом чтения блока анализа состояния и входом чтения приоритетного прерывания, выход записи сис- 5О темного контроллера соединен с вторым входом режима блока шинных формирователей и входами записи блоков оперативной памяти, анализа состояния канала и приоритетного прерывания, выход подтверждения прерывания системного контроллера соединен с третьим информационным входом блока контроля времени ожидания ответа и.вход

4 16 дом подтверждения прерывания блока приоритетного прерывания, выход запроса прерывания которого соединен с одноименным входом процессора, выход установки генератора тактовых импульсоВ соединен с четвертым информационным входом блока контроля времени ожидания ответа, первый выход дешиф- ратора соединен с управляющим входом блока приоритетного прерывания, второй выход дешифратора соединен с пятым информационным входом блока контроля времени ожидания ответа, управляющим входом блока анализа состояния и вторым информационным входом блока синхронизации, третий выход дешифратора соединен с входом выбора блока шинных формирователей и третьим информационным входом блока синхронизации, четвертый и пятый выходы дешифратора соединены соответственно с входом выбора постоянной памяти и входом синхронизации оперативной памяти, выход первого разряда группы информационных выходов блока анализа состояния соединен с входом второго разряда запроса прерывания блока приоритетного прерывания, выход адреса блока анализа является одноименным выходом устройства, управляющий выход блока анализа состояния соединен с первым входом блока контроля времени связи, входы первого, второго, третьего разрядов и старших разрядов управляющей информации группы входов устройства соединены соответственно с вторым информационным входом блока контроля времени связи, четвертым информационным входом блока синхронизации, информационным входом блока контроля времени ожидания обмена и входом управления блока анализа состояния канала, третий информационный вход блока контроля времени связи соединен с информационным входом блока контроля времени ожида- ния обмена, вход блокировки ответа устройства соединен с шестым информационным входом блока контроля времени ожидания ответа и пятым информационным входом блока синхронизации связи, вход ответа устройства соединен с шестым информационным входом блока синхронизации, выход которого соединен с входом готовности генератора тактовых импульсов, выходы четырнадцатого и пятнадцатого разрядов ад17 15 реса группы адресных выходов процес= сора соединены соответственно с первым и вторым входами элемента И, выход Которого соединен с третьим и четвертым входами дешифратора, груп= па адресных выходов микропроцессо99864 18 ра соединена с информационными входами группы блока шинньж формирователей, группа входов-выходов которого соединена с входом-выходом данных устройства.

1599864

1599864

И1

Составитель Б.Резван

Техред М.Дидык

Корректор Н. Ревская

Редактор .А.Маковская

Заказ 3144 Тираж 571 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ CgCP

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101