Устройство для сохранения информации в полупроводниковой памяти при аварийном отключении питания

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в качестве оперативного запоминающего устройства в системах числового программного управления. Целью изобретения является повышение надежности устройства и уменьшение мощности потребления. Это достигается за счет введения третьего ограничительного элемента на третьем резисторе, делителя напряжения на четвертом и пятом резисторах, источника опорного напряжения на шестом резисторе и стабилитроне, второго накопительного элемента на втором конденсаторе и ключей на третьем и четвертом диодах. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4494477/24-24 (22) 14. 10.88 (46) 15.10.90. Бюл. № 38 (72) В. А. Лисицын и Е. Я. Марголин (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР № 1205193, кл. G 11 С 29/00, 1986.

Авторское свидетельство СССР № !285537, кл. G 11 С 29/00,, 1987.

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам, и может быть использовано в качестве оперативного запоминающего устройства в системах числового программного управления.

Цель изобретения — повышение надежности устройства и уменьшение мощности потребления от резервного источника питания.

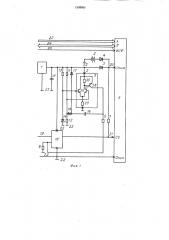

На фиг. 1 приведена функциональная схема предложенного устройства, на фиг. 2 — временные диаграммы.

Устройство содержит основной и резервный источники 1 и 2 питания, разделительные элементы на диодах 3 и 4, полупроводниковую память 5, ограничительные элементы на резисторах 6, 7 и 8, компаратор 9, формирователь 10 импульсов, делитель напряSU,,» 599901 А 1 (51)5 G 11 С 29/00

2 (54) УСТРОЙСТВО ДЛЯ СОХРАНЕНИЯ

ИНФОРМАЦИИ В ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ ПРИ АВАРИЙНОМ ОТКЛЮЧЕНИИ ПИТАНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в качестве оперативного запоминающего устройства в системах числового программного управления. Целью изобретения является повышение надежности устройства и уменьшение мощности потребления. Это достигается за счет введения третьего ограничительного элемента на третьем резисторе, делителя напряжения на четвертом и пятом резисторах, источника опорного напряжения на шестом резисторе и стабилитроне, второго накопительного элемента на втором конденсаторе и ключей на третьем и четвертом диодах. 1 з.п. ф-лы, 2 ил. жения на резисторах 11 и 12, источник опорного напряжения на резисторе 13 и стабилитроне 14, накопительные элементы на конденсаторах 15 и 16, ключи на диодах

17 и 18, информационый вход 19 устройства, выходы 20 и 21 устройства, шину 22 нулевого потенциала устройства, адресную шину 23, шину 24 данных, вход 25 режима работы.

Компаратор 9 содержит транзисторы 26—

28, резисторы 29 и 30. На фиг. 2 обозначены диаграммы напряжений 31 — 37.

Устройство работает следующим образом.

При номинальном уровне напряжения основного источника 1 питания напряжение на инвертирующем входе компаратора 9 равно напряжению стабилизации стабилитрона

14 источника опорного напряжения. При этом напряжение на неинвертирующем вхо1599901 компаратора 9, поступающее с дели теля напряжения, на резисторах 11 и 12, превышает напряжение стабилитрона 14.

На выходе компаратора 9 имеется высокий уровень напряжения, который через ограничительный элемент 6 поступает на вход запрета формирователя 10, разрешая прохождение сигналов выборки памяти со входа

19 на выход 21 устройства, а с него на соответствующий вход запоминающих матриц .памяти 5. Сигналы выборки, проходящие через формирователь 10, осуществляют в зависимости от уровня сигнала на входе 25 режима работы запись информации с шины 24 данных по адресу на адресной шине 23 в память 5 или чтение по адресу на адресной шине 23 в шину 24 данных.

Диоды 17 и !8 ключей находятся в закрытом состоянии. Напряжение на накопительном элементе 16 отсутствует. Так как изменения напряжения на выводах конденсатора 16 не происходит, ток через него не протекает, цепь обратной связи компаратора

9 разорвана. Питание на память 5 подается от основного источника 1 питания через открытый разделительный элемент на диоде 3.

Разделительный элемент на диоде 4 закрыт.

Ток от резервного источника 2 питания не потребляется.

При аварийном отключении источника 1 питания напряжение питания устройства начинает медленно (благодаря конденсатору

15) снижаться (диаграмма 31, Тl фиг. 2).

Напряжение на стабилитроне 14 источника опорного напряжения остается неизменным до тех пор, пока напряжение питания устройства не упадет до напряжения стабилитрона 14 (диаграмма 32). Напряжение на выходе делителя напряжения на резисторах

11 и 12 начинает снижаться одновременно с напряжением питания.

Как только напряжение на резисторах

11 и 12 упадет до напряжения стабилитрона 14, что выполняется при напряжении питания, равном минимально допустимому рабочему напряжению памяти 5, компаратор 9 переключится, и напряжение на его выходе скачкообразно снизится (диаграмма 34, Т2 фиг. 2) .

Так как напряжение на конденсаторе 16 не может измениться мгновенно, напряжение в точке соединения диодов 17 и 18 ключей также скачкообразно снизится.

Диод 17 откроется и это изменение напряжения поступит на неинвертирующий вход компаратора 9, замыкая цепь положительной обратной связи и ускоряя процесс переключения компаратора 9.

Низкий уровень напряжения с выхода компаратора 9 через ограничительный элемент на резисторе 6 поступает на вход запрета формирователя 10 и блокирует прохождение сигналов выборки на вход 21 устрйства. Обращение к памяти 5 исключается.

5

Конденсатор 16 начинает заряжаться спадающим питающим напряжением через резисторы 6, 8 и 11, а затем, после снижения питающего напряжения ниже напряжения на конденсаторе 16, разряжается до нуля через открывшийся ключ на диоде 17 и резисторы

12, 11, 6 и 8 (диаграмма 36, ТЗ, Т4 фиг. 2).

При снижении основного питающего напряжения ниже уровня переключения устройства вплоть до нуля напряжение на инвертирующем входе компаратора 9 будет превышать напряжение на его неинвертирующем входе. Транзистор 26 будет открыт, а транзистор 27 и, следовательно, транзистор

28 будут закрыты. Так как запрещающий вход формирователя 10 соединен через ограничительный элемент на резисторе 8 с шиной 22 нулевого потенциала, запрещающий уровень на этом входе будет сохраняться и при снижении напряжения основного источника питания от минимально допустимого значения до нуля.

Благодаря ограничительному элементу на резисторе 7 высокий уровень напряжения будет сохраняться на выходе 21 устройства все время, когда напряжение основного источника 1 питания ниже номинального.

Память 3 будет при этом находиться в режиме хранения.

При снижении напряжения основного источника 1 питания ниже напряжения резервного источника 2 питания, разделительный элемент на диоде 3 закрывается, а разделительный элемент на диоде 4 открывается, обеспечивая непрерывность подачи питания на память 5 и поддержание высокого (запрещающего) уровня на выходе устройства 21.

При включении питания (Т5 фиг. 2) напряжение питания нарастает от нуля до номинального значения. Напряжение на стабилитроне 14 нарастает от нуля до напряжения стабилизации стабилитрона 14 (Тб фиг. 2). Напряжение основного источника

1 питания через резистор 11, диод 18 и ограничительные элементы на резисторах 6 и 8 заряжается конденсатор 16.

Напряжение на средней точке делителя напряжения из резисторов 11 и 12 начинает расти с задержкой, определяемой постоянной времени этой цепи (диаграмма 33, Тб, Т7 фиг. 2). При достижении напряжением на средней точке делителя уровня напряжения стабилитрона 14, происходит переключение компаратора 9. Напряжение на его выходе скачкообразно возрастает. Так как напряжение на конденсаторе 16 не может измениться мгновенно, возрастает напряжение и в точке соединения резисторов 11 и

12. Диод 18 закрывается. Поскольку при этом отключается цепь заряда конденсатора

16, на делителе напряжения появляется небольшой скачок напряжения (диаграмма

33, Т8 фиг. 2), поступающий на неинвер\

1599901 тирующий вход компаратора 9. Замыкается цепь положительной обратной связи, ускоряя процесс переключения компаратора 9.

Время, необходимое для заряда конденсатора 16 до напряжения стабилитрона 14, определяет задержку переключения компаратора 9 и тем самым задержку подачи разрешающего потенциала на вход формирователя 10 по отношению к моменту подачи питающего напряжения.

В тот момент, когда напряжение в точке соединения диодов 17 и 18 достигает значения основного источника 1 питания, открывается диод 17. Конденсатор 16 быстро разряжается через малое сопротивление диода

17 и открытого транзистора 28, после чего устройство оказывается в исходном состоянии (Т9 фиг. 2).

Малое время восстановления устройства при включении питания при наличии запаса по времени задержки включения позволяет отслеживать даже кратковременные провалы напряжения основного источника питания ниже минимально допустимого значения (Т10 фиг. 2). Такие провалы напряжения питания могут привести к записи ложной информации в память 5, если приходятся на момент выборки памяти. Отработка защитного интервала времени, в течение которого блокируется выборка, на каждую такую помеху по питанию исключает запись в память 5 .ложной информации.

Формула изобретения

1. Устройство для сохранения информации в полупроводниковой памяти при аварийном отключении питания, содержащее основной и резервный источники литания, разделительные элементы на первом и втором диодах, катоды которых объединены и являются первым выходом устройства, первый накопительный элемент на первом конденсаторе, одна обкладка которого соедине\ на с выходом основного источника литания и с анодом первого диода, другая обкладка первого конденсатора соединена с шиной нулевого потенциала устройства, компаратор, первый вход питания которого соединен с входами питания. основного . и резервного источников питания и с шиной нулевого потенциала устройства, формирователь импульсов, входы питания которого соединены соответственно с выходом основного источника питания и с шиной нулевого потенциала устройства, первый и второй ограничительные элементы на первом и втором резисторах, выводы первого из которых

1О

20 соединены соответственно с выходом компаратора и с входом запрета формирователя импульсов, информационный вход которого является информационным входом устройства, анод второго диода соединен с выходом резервного источника питания, выводы второго резистора соединены соответственно с катодом первого диода и с в ых одом формирователя импульсов, второй вход питания компаратора соединен с выходом основного источника питания, выход формирователя импульсов является вторым выходом устройства, отличающееся тем, что, с целью повышения надежности устроиства и уменьшения мощности потребления, в устройство введены третий ограничительный элемент на третьем резисторе, делитель напряжения на четвертом и пятом резисторах, источник опорного напряжения на шестом резисторе и стабилитроне, второй накопительный элемент на втором конденсаторе и ключи на третьем и четвертом диодах, катод третьего диода соединен с выходом основного источника питания и с первыми выводами четвертого и шестого резисторов, анод третьего диода соединен с катодом четвертого диода и с первой обкладкой второго конденсатора, вторая обкладка которого соединена с выходом компаратора, анод четвертого диода соединен с первым информационным входом компаратора, с вторым выводом четвертого резистора и с первым выводом пятого резистора, второй вывод которого соединен с анодом стабилитрона и с шиной нулевого потенциала устройства, второй вывод шестого резистора соединен с вторым информационным входом компаратора и с катодом стабилитрона, первый вывод третьего резистора соединен с входом запрета формирователя импульсов, второй вывод третьего резистора соединен с шиной нулевого потенциала устройства.

2. Устройство по и. 1, отличающееся тем, что компаратор содержит первый, вто40 рой и третий транзисторы, седьмой и восьмой резисторы, причем первый вывод седьмого резистора соединен с эмиттерами первого и второго транзисторов, базы которых являются соответственно информационными входами компаратора, второй вывод седьмого транзистора является первым входом . питания компаратора, коллектор первого транзистора является вторым входом питания компаратора и соединен с первым выводом восьмого резистора и с эмиттером третьего транзистора, база которого соединена с вторым выводом восьмого резистора и с коллектором второго транзистора, коллектор третьего транзистора является выходом компаратора.

1599901

Фиг. 1

1599901

74 75 ТБТ7 ТВ Т9 T1L7

4 Г 2

Составитель А. Воронин

Редактор И. Сегляник Техред А. Кравчук Корректор Т. Малец

Заказ 3146 Тираж 485 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-издательский комбинат «Патент», г. Ужгород, ул. Гагарина, 101