Двоичный счетчик

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в качестве базового счетного элемента в устройствах с повышенной эксплуатационной отказоустойчивостью. Цель изобретения - повышение эксплуатационной отказоустойчивости устройства путем введения в его структуру резервного разряда и средств автоматической реконфигурации работоспособной структуры. Двоичный счетчик содержит разряды 1-4, элементы И 5, 10, элементы НЕ 6,7, элементы ИЛИ-НЕ 8 и 9, элементы И-НЕ 11.1-11.4, элементы 3И-ИЛИ 12.1-12.4. За счет введения резервного разряда, содержащего триггер 16.5, элемент И-НЕ 14.5 и элемент 2И-ИЛИ 17.5, а в первый разряд элемента И-НЕ 14.1, И/И-НЕ 13,1, во второй, третий и четвертый разряды элементов И/И-НЕ 13.2-13.4, 2И-ИЛИ-НЕ 15.2-15.4 и элементов 2И-ИЛИ 17.2-17.4 с соответствующими конструктивными связями, достигается возможность при отказе одного из основных разрядов перейти автоматически на резервную работоспособную структуру, проводя замену интегральной микросхемы в устройстве. При этом, в случае отказа одного из основных разрядов, на соответствующий управляющий вход запрета работы двоичного счетчика подается сигнал логического нуля. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (И1 (5I)g H 03 IC 23/58

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4469031/24-21 (22) 01.08.88 (46) 15.10.90. Бюл. Р 38 (72) А.Н. Пархоменко, В.В. Голубцов, В,С. Харламов и А.Е. Корняков (53) 621.374.322(088.8) (56) Авторское свидетельство СССР

Р 6 16712, кл . Н 03 К 23/24, 1978.

Авторское свидетельство СССР

Р 1529447, кл. Н 03 К 23/58, 1988.

Применение интегральных микросхем в электронной вычислительной технике.

Справочник./Под ред. Б.Н. Файзулаева, Б.В. Тарабрина. — М.: Радио и связь, 1987, с. 41, рис. 3.34.

2 (54) ДВОИЧНЬЙ СЧЕТЧИК (57) Изобретение относится к импульсной технике и может быть использовано в качестве базового счетного элемента в устройствах с повышенной эксплуатационной отказоустойчивостью. Цель изобретения — повышение эксплуатационной отказоустойчивости устройства путем введения в его структуру резерв.;ого разряда и средств автоматической реконфигурации работоспособной структуры. Двоичный счетчик содержит разряды 1-4, элементы И 5, 10, элементы

НЕ 6, 7, элемен и ИЛИ-НЕ 8 и 9, элементы И-НЕ 11.1 — 11.4, элементы 3 И1599988

ИЛИ 12.1-12.4. За счет введения резервного разряда, содержащего триггер

16.5, элемент И-НЕ 14.5 и элемент

2И-ИЛИ 17.5, в первый разряд элемента И-НЕ 14.1, И/И-НЕ 13.1, во второй, третий и четвертый разряды элементов

И/И-НЕ 13.2- t3.4, 2И-ИЛИ-НЕ 15.215.4 и элементов 2И-ИЛИ 17.2-17.4 с соответствующими конструктивными связями, достигается возможность !

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной технике в качестве базового компонента с повышенной эксплу- 20 атационной отказоустойчивостью.

Цель изобретения — повьш ение эксплуатационной отказоустойчивости устройства путем введения в его структуру резервного разряда и средств 25 автоматической реконфигурации работоспособной структуры.

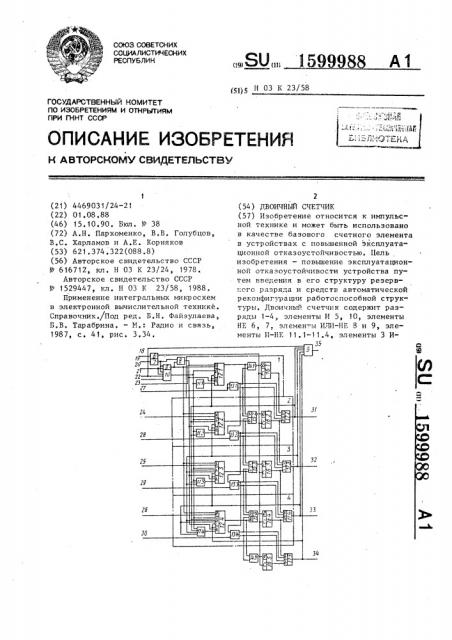

На чертеже приведена функциональная схема предлагаемого двоичного счетчика. 30

Устройство содержит разряды 1-4, первый элемент И 5, первый 6 и второй 7. элементы НЕ, первый 8 и второй

9 элементы ИЛИ-НЕ, второй элемент

И 10, первые элементы И-НЕ 11,1

11.4 разрядов, элементы ЗИ-ИЛИ 12,112.4 разрядов, элементы И/И-НЕ 13.113.4 разрядов, вторые элементы И-НЕ

14.1 и 14.5 первого и резервного разрядов, элементы 2И-ИЛИ-НЕ 15,2- 40

15.4 разрядов, триггеры 16.1-16.5 разрядов и элементы 2И-ИЛИ 17.217 ° 5 разрядов.

Синхровход 18 устройства соединен с входом элемента НЕ 6, выход ко- 45 торого соединен с синхровходами триггеров 16.1-16.5. Вход 19 установки в "0" устройства соединен с входом элемента НЕ 7, выход которого соединен с входами элементов ИЛИ-HE 8 и 9 и инверсным входом элемента И 10.

Первый вход 20 управления режимом работы устройства соединен с входами . элементов ИЛИ-НЕ 9,и И 10. Вход 21 разрешения переноса устройства соединен с входом элемента И 5 и входом элемента И 10 ° Второй вход 23 управления режимом работы устройства соединен с входом элемента И 10, выход при отказе одного из основных разрядов перейти автоматически на резервную работоспособную структуру,.проводят замену интегральной микросхемы в устройстве. При этом в случае отказа одного из основных разрядов на соответствующий управляющий вход запрета работы двоичного счетчика подается сигнал логического нуля.

1 которого соединен с первыми входами элементов И-НЕ 11.1-11.4 и первыми входами вторых групп входов элементов

ЗИ-ИЛИ 12.1-12.4 разрядов. Выход элемента ИЛИ-НЕ 9 соединен с вторым входом элемента ИЛИ-НЕ 8 и первыми входами первых групп входов элементов ЗИ-ИЛИ 12.1-12.4 разрядов. Входы

23-26 предварительной установки устройства соединены соответственно с вторыми входами первых групп входов элементов ЗИ-ИЛИ 12.1-12.4 соответствующих разрядов, Входы 27-30 запрета работы разрядов соединены соответственно с первыми входами элементов И/И-НЕ 13.1-13.4 одноименных разрядов. Выход элемента ИЛИ-НЕ 8 соединен с вторыми входами третьих групп входов элементов ЗИ-ИЛИ 12.112 ° 4.

Выход элемента,И-НЕ 11.1 первого разряда соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ

12.1, выход которого соединен с первым входом элемента И-НЕ 14„,1 и первым входом первой группы входов элемента 2И-ИЛИ-НЕ 15. 2. Прямой выход элемента И/И-НЕ 13.1 соединен с вторым входом элемента И/И-HE 13.2, входом первой группы входов элемента

2И-ИЛИ 17.2 и вторым входом элемента И-НЕ 14.1, выход которого соединен с инверсным D-входом триггера 16.1,, прямой выход которого соединен с входом первой группы входов элемента 2И-ИЛИ 17.2. Инверсный выход элемента И/И-НЕ 13.1 соединен с входом первой группы входов элемента 2И-ИЛИ-HE 15.2 и входом второй группы входов элемента 2И-ИЛИ 17.2.

Выход элемента И-НЕ 11,2 соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ 12,2 выход которого соединен с входом второй группы

5 159 входов элемента 2И-ИЛИ-НЕ 15.3. Прямой выход элемента И/И-НЕ 13,2 соединен с вторым входом элемента И/И-НЕ

13.3, входом первой группы входов элемента 2И-ИЛИ 17.3 и входом второй группы входов. элемента 2И-ЩП1-HF 15.2 выход которого соединен с инверсным входом D-триггера 16.2, прямой выход которого соединен с входом второй группы входов элемента 2И-ИЛИ 17.2 и входом первой группы входов элемента 2И-ИЛИ 17.3. Инверсный выход элемента И/И-HP. 13.2 соединен с входом первой группы входов элемента

2И-ИЛИ-НЕ 15,3 и входом второй группы входов элемента 2И-ИЛИ 17.3, Выход элемента И-НЕ 11.3 соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ 12.3, выход которого соединен с входом второй группы входов элемента 2И-ИЛИ-НЕ

15.3 и входом первой группы входов элемента 2И-ИЛИ-НЕ 15.4. Прямой выход элемента И/И-НЕ 13.3 соединен с третьим входом элемента И/И-НЕ

13.4, входом первой группы входов элемента 2И-ИЛИ 17.4 и входом второй группы входов элемента 2И-ИЛИ-НЕ

15.3, выход которого соединен с инверсным входом D-триггера 16.3, пря.— мой выход которого соединен с входом второй группы входов элемента 2И-ИЛИ

17.3 и входом первой группы входов элемента 2И-ИЛИ 17.4. Инверсный выход элемента И/И-НЕ 13.3 соединен с входом первой группы входов элемента 2И-ИЛИ-НЕ 15.4 и входом второй группы входов элемента 2И-ИЛИ 17.4.

Выход элемента И-НЕ 11.4 соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ 12,4, выход которого соединен с входом второй группы входов элемента 2И-ИЛИ-НЕ 15.4, и первым входом элемента И-НЕ 14.5.

Прямой выход элемента И/И-НЕ 13.4 соединен с входом первой группы входов элемента 2И-ИЛИ 17 ° 5 и входом второй группы входов элемента 2И-ИЛИНЕ 15.4, выход которого соединен с инверсным входом D-триггера 16.4, прямой выход которого соединен с входом второй группы входов элемента

2И-ИЛИ 17.4 и входом первой группы входов элемента 2И-ИЛИ 17.5. Инверсный выход элемента И/И-HE 13.4 соединен с входом второй группы входов элемента 2И-ИЛИ 17.5 и входом элемента И-НЕ 14.5, выход которого соеди-, нен с инверсным входом D-триггера

9988 6

ЗО

16.5, прямой выход которого соединен с входом. второй группы входов элемента 2И-ИЛИ 17.5..

Выход элемента 2И-ИЛИ 17.2 является первым разрядным выходом 31 устройства и соединен с входом элемента

И 5, инверсным входом второй и первым входом третьей групп входов элемента

ЗИ-ИЛИ 12.1, вторыми входами вторых групп входов элементов ЗИ-ИЛИ 12.212.4 и вторыми входами элементов И-НЕ

11.2-11.4.

Выход элемента 2И-ИЛИ 17.3 является вторым разрядным выходом 32 устройства и соединен с третьим входом элемента И 5, инверсным входом второй и первым входом третьей групп входов элемента ЗИ-ИЛИ 12.2, третьими входами вторых групп входов элементов ЗИ-ИЛИ

12.3 и 12,4 и третьими входами элементов И-HE 11.3 и 11.4. !

Выход элемента 2И-ИЛИ 17.4 явля-, ется третьим разрядным выходом устройства 33 и соединен с инверсным входом второй и первым входом третьей групп входов элемента ЗИ-ИЛИ 12.3, четвертым входом второй группы входов элемента ЗИ-ИЛИ 12.4 и четвертым входом элемента И-НЕ 1 1.. .

Выход элемента 2И-: Jf 17.5 является четвертым разрядным выходом устройства 34 и соединен с инверсным входом второй и первым входом третьей групп входов элемента ЗИ-ИЛИ 12,4, Выходы элементов 2И-ИЛИ 17,217.5 подключены дополнительно к соответствующим входам элемента И 5, выход 35 которого является выходом переноса устройства.

Элемент И 5 формирует на своем выходе единицу переноса при наличии единичного потенциала на входе 21 разрешения переноса . и единичном состоянии триггеров всех четырех разрядов.

Элементы НЕ 6 и 7, ИЛИ-НЕ 8 и 9, И 10 образуют схему управления режимами работы двоичного счетчика: установка в "0", установка в состояние, соответствующее значениям сигналов на входах 23-26, счетный режим.

Элементы И-НЕ 11.1-11.4 формируют на своих выходах сигналы управления открытием или закрытием третьих групп входов соответствующих элементов ЗИ-ИЛИ 12.! 12.4 в счетном режиме при передаче предыдущего состояния триггера в последующий разряд двоичного счетчика.

1599988

Элементы ЗИ-ИЛИ 12. 1-12.4 предназначены для подачи на информационные входы D-триггеров (через элементы

И-EIE 14,1 и 14.5 и элементы 2И-ИЛИ-НЕ

15.2-15.4) сигналов с входов 23-26

5 через свою первую группу входов в режиме занесения параллельного кода, сигналов переноса с предыдущего разряда в счетном режиме через свои

10 вторую и третью группы входов.

Элементы И/И-НЕ 13.1-13.4 последовательно обобщают сигнал работоспособного состояния всех предыдущих разрядов и формируют на своих инверс- 5 ном и прямом выходах соответствующие сигналы настроечной функции, управ" ляющей работоспособной конфигурацией двоичного счетчика.

Элемент И-НЕ 14.1 пропускает информационные сигналы с выхода элемента ЗИ-ИЛИ 12.1 на.соответствующий вход триггера 16.1 в случае исправного. состояния первого разряда. Элемент И-НЕ 14.5 пропускает информаци- 25 онные сигналы с выхода элемента ЗИИЛИ 12.4 в случае неисправного состояния одного из четырех основных разрядов.

Элементы 2И-ИЛИ-НЕ 15.2-15.4 про- 30 |пускают на информационные входы соответствующих триггеров 16.2-16.4 с выходов элементов ЗИ-ИЛИ 12.212.4 либо с выхода одноименного элемента, либо с выхода элемента ЗИ-ИЛИ

i2 предыдущего разряда, в зависимости

35 от степени исправности предыдущих основных разрядов.

Элементы 2И-ИЛИ 17.2-17.5 пропускают на разрядные выходы 31-34 уст40 ройства сигналы либо с выхода триггера предыдущего разряда, либо с выхода триггера одноименного разряда в зависимости от исправного или неисправного состояния всех предыдущих 45 разрядов.

Двоичный счетчик работает следующим образом.

Для установки двоичного счетчика в исходное нулевое состояние на вход

19 установки в "0" устройства подается сигнал нулевого логического уровня„ а на синхровход 18 — импульс.

При этом на выходе элемента ИЛИ-НЕ 8 вырабатывается сигнал нулевого логического уровня, которыи закрывает

55 третьи группы входов элементов ЗИИЛИ 12.1-12.4, первые и вторые группы входов которых также закрыты следующими сигналами: первые группы входов — нулевым сигналом с выхода эле мента ИЛИ-НЕ 9(на первом управляю,щем — сигнал единичного логического уровня) и вторые группы входов — нулевым сигналом с выхода элемента

И 10 (на его инверсном входе — сигнал логической единицы с выхода элемента НЕ 7) . Таким образом, на выходах элементов ЗИ-ИЛИ 12.1-12.4 формируются сигналы логического нуля, что приводит к формированию на выходах элементов И-НЕ 14.1 и 14.5, 2И-ИЛИ-НЕ 15.2-15,4 сигналов единичного логического уровня. В результате этого с приходом синхроимпульса с синхровхода 8 устройства через элемент НЕ 6 на синхровходы триггеров 16.1-16.5 последние принимают состояние логического нуля.

При исправном состоянии всех основных триггеров 16.1-16.4 на входы запрета работы 27-30 подаются сигналы логической единицы. В этом случае единичными разрешающими сигналами открыты следующие логические элементы устройства: элемент И-HE 14.1; вторые группы входов элементов 2И-ИЛИНЕ 15.2-15.4, первые группы входов элементов 2И-ИЛИ 17.2-17.5. Одновременно с этим закрываются следующие логические элементы устройства: первые группы входов элементов 2И-ИЛИНЕ 15.2-15.4; элемент И-НЕ 14.5 и вторые группы входов элементов 2И-ИЛИ

17.2-17.5.

Установка двоичного счетчика в состояние, равное информации на входах 23-26 производится следующим образом.

На первый вход 20 управления устройства подается сигнал логического нуля, на синхровход 18 устройства— синхроимпульс, на вход 19 установки в "0" — единичный сигнал, на входы

21 разрешения переноса Р и второй вход 22 управленим — сигналы логического нуля и на входы 23-26 предварительной установки - информация предварительной установки двоичного счетчика.

В этом случае открываются первые группы входов элементов ЗИ-ИЛИ 12.112.4 и на их вьжодах формируются сигналы, идентичные сигналам на соответствующих входах 23-26 устройства.

Эти сигналы через элементы И-НЕ

14.1, 2И-ИЛИ-HE 15.2-15.4 поступают

1599988

10 на инверсные П-входы триггеров 16.116.4. С приходом синхроимпульса эти триггеры принимают значения, равные значениям сигналов на соответствую5 щих им входах, и через первые группы входов элементов 2И-ИЛИ 17.2-17.5 поступают на разрядные выходы 31-34 устройства. Выход триггера 16.5 отключен закрытой второй группой входов элемента 2И-ИЛИ 17 ° 5.

Подсчет импульсов, поступающих на синхровход С устройства, производится по следующей логической ветви предлагаемого двоичного счетчика.

На входах 19-22 при этом присутствуют сигналы логической единицы, а на синхровход 18 устройства — поступают синхроимпульсы.

Импульсы поступают через элемент

НЕ 6 на синхровходы триггеров 16.116.4, которые с приходом каждого синхроимпульса изменяют свое состояние в зависимости от предыдущего своего состояния и состояний тригге- 25 ров предыдущих разрядов.

Рассмотрим пример подсчета синхроимпульсов с предварительной установкой счетчика в состояние "1001",т.е. когда вначале режима счета в двоичный счетчик были занесены единичные состояния в триггеры 16.1 и 16.4.

В этом случае единичные состояния с выходов элементов 2И-ИЛИ 17.2 и 17.5 открывают следующие логические эле35 менты структуры двоичного счетчика: третью группу входов элементов ЗИИЛИ 12.1 и 12.4 (вторые группы входов этих же элементов этими же сигналами закрываются по их инверсным 40 входам); вторые группы входов элемен тов 12.2 и 12.3 по их вторым входам.

С приходом синхроимпульса триггер

16.1 устанавливается в состояние

"0" триггер 16-2 — в состояние лоУ 45 гической единицы, триггеры 16.3 и

16.4 остаются в своих прежних нулевом и единичном соответственно состояниях. Это происходит следующим образом. Так как все три группы входов элемента ЗИ-ИЛИ 12.1 закрыты (первая

50 группа входов закрыта нулевым сигналом с выхода элемента ИЛИ-EIE 9, вторая — единичным сигналом на своем инверсном входе с выхода элемента

2И-ИЛИ 17.2 и третья группа входов нулевым сигналом с выхода элемента

И-НЕ 11.1), то на его выходе формируется сигнал логического нуля, который через элемент И-НЕ 14.1 поступает на инверсный D-вход триггера

16.1. Следовательно, с приходом синхроимпульса триггер 16.1 установит- ся в нулевое состояние.

В элементе ЗИ-KIN 12.2 в этом случае открыта вторая группа входов единичным разрешающим сигналом с выхода элемента И 17, с выхода элемента 2И-ИЛИ 17.2 и выхода элемента

2И-ИЛИ 17.3 (нулевой уровень сигнала на инверсный вход) . Следовательно, единичный уровень сигнала через вторую группу входов элемента 2ИИЛИ-НЕ 16.2 поступает на инверсный вход D-триггера 16.2, что приводит к установке его в состояние "1".

Все три группы входов элемента

ЗИ-ИЛИ 12.3 в этом случае закрыты: первая группа входов — нулевым сигналом с выхода элемента ИЛИ-НЕ 9; вторая — нулевым сигналом с выхода элемента 2И-ИЛИ 17.3 и третья группа входов — нулевым сигналом с выхода элемента 2И-ИЛИ 17.4. Следовательно, на выходе элемента ЗИ-ИЛИ 12.3 формируется сигнал логического нуля, который через вторую группу входов элемента 2И-ИЛИ-НЕ 15.3 подтверждает прежнее нулевое состояние триггера

16.3.

В элементе ЗИ-ИЛИ 12.4 открыта третья группа входов с выхода элементов 2И-ИЛИ 17.5, выхода элемента

ИЛИ-НЕ 8 и выхода элемента И-НЕ

11.4, поэтому триггер 16.4 с приходом синхроимпульса остается в единичном состоянии.

Таким образом, с приходом первого синхроимпульса двоичный счетчик после состояния "1001" устанавливается в состояние "1001", т.е. изменяет свое состояние на "+1".

С приходом второго синхроимпульса предлагаемый двоичный счетчик принимает состояние "1011" по следующему алгоритму.

Триггер 16.1 устанавливается в состояние единицы, а триггеры 16.216.4 остаются в своих прежних состояниях, Триггер 16.1 устанавливается в единичное состояние, так как открыта вторая группа входов элемента ЗИ-ИЛИ

12. 1 с выхода элемента И 10 и выхода элемента 2И-ИЛИ 17.2.

Триггер 16.2 остается в единичном состоянии, так как в этом случае от1599988 крыта третья группа входов элемента

ЗИ-ИЛИ 12.2 с выходов элементов

2И-ИЛИ 17.3, ИЛИ-НЕ 8 и И-НЕ 11.2 соответственно.

Триггер 16.3 остается в нулевом состоянии, так как все три группы входов элемента ЗИ-ИЛИ 12.3 закрыты сигналами с выходов элементов ИЛИ-НЕ

9, 2И-ИЛИ 17.2, и 17.4 соответствен- 10 но.

Триггер 16.4 остается в единичном состоянии, так как остается открытой третья группа входов элемента ЗИИЛИ 12.4. 15

Подсчет третьего, четвертого и т.д. импульсов производится аналогичным образом. При достижении двоичным счетчиком состояния, равного "1111", на его выходе переноса 35 формирует- 20 ся единица переноса, что позволяет образовать из нескольких предлагаемых двоичных счетчиков двоичный счетчик большей разрядности.

При отказе какого-либо одного из 25 основных разрядов двоичного счетчика на соответствующий управляющий вход запрета работы разряда подается сигнал логического нуля. Рассмотрим пример, когда отказал триггер второго 30 разряда 16 .2, В этом случае на вход запрета работы 28 подается сигнал нулевого логического уровня, который приводит к противоположной смене сигналов на прямом и инверсном выходах элементов И/И-НЕ 13.2-13.4.

Вследствие этого открываются следующие логические элементы структуры предлагаемого двоичного счетчика: первые группы входов элементов 4Р

2И-ИЛИ-HE 15.3 и 15.4; элемент И-НЕ

14 ° 5 и вторые группы входов элементов 2И-ИЛИ 17.3-17.5. Одновременно с этим закрываются следующие логические элементы структуры двоичного 45 счетчика: вторые группы входов элементов 2И-ИЛИ-НЕ 15.2-15,4; первые группы входов элементов 2И-ИЛИ 17.317 ° 5 и сами элементы И/И-НЕ 13.213.4.

В режиме занесения параллельного кода информации с входов устройства двоичный счетчик в этом случае функционирует следующим образом.

Сигнал с входа 23 устройства через открытую лервую группу входов элемента ЗИ-ИЛИ t2.1, элемент И-HE 14.1 поступает на инверсный 9-вход триггера 16.1. Сигнал с входа 24 устрой12 ства через открытую первую группу входов элемента ЗИ-ИЛИ 12.2, первую группу входов элемента 2И-ИЛИ-НЕ

15.3 поступает на инверсный D-вход триггера 16.3. Сигнал с входа 25 устройства через открытые первые группы входов элементов ЗИ-ИЛИ 12.3 и 2И-ИЛИ-НЕ 15.4 поступает на вход

D-триггера 16.4. Сигнал с входа предварительной установки 26 устройства через открытую первую группу входов элемента ЗИ-ИЛИ 12.4 и элемент И-НЕ 14.5 поступает на инверсный D-вход триггера 16.5. С приходом синхроимпуЛьса триггеры 16. 1, 16.3-16.5 устанавливаются в состояния, соответствующие состояниям на входах 23-26 устройства. Сигнал с прямого выхода триггера t6.1 через открытую первую группу входов элемента 2И-ИЛИ 17.2 поступает на разрядный выход 31 устройства. Сигнал с прямого выхода триггера 16.3 через открытую вторую группу входов элемента 2И-ИЛИ 17.3 поступает на разрядный выход 32 устройства. Сигнал с прямого выхода триггеров 16.4 и 16.5 поступает через открытые вторые группы входов элементов 2И-ИЛИ t7.4 и 17,5 на разрядные выходы 33 и 34 устройства соответственно. Таким образом, в результате подачи нулевого логического уровня сигнала на вход запрета работы 28 триггер 16.2 вытесняется из работоспособной структуры предлагаемого двоичного счетчика.

Подсчет импульсов в этом случае производится по следующему алгоритму.

При нулевом состоянии триггера каждого разряда и единичном состоянии триггеров предшествующих разрядов этот триггер при помощи открытого состояния второй группы входов соответствующего элемента ЗИ-ИЛИ 12 устанавливается в единичное состояние с приходом очередного импульса. При предыдущем единичном состоянии триггера соответствующего разряда и при единичном состоянии триггеров предыдущих разрядов данный триггер устанавливается с приходом очередного синхроимпульса в нулевое состояние.

В остальных случаях триггеры соответствующих разрядов сохраняют свое прежнее состояние, Обход отказавшего триггера 16.2 также осуществляется закрытым состоянием элемента 2И-ИЛИНЕ 15.2 по обеим группам входов и

1599988

1О

20 закрытым состоянием первой группы входов элемента 2И-ИЛИ 17.3, а также закрытым состоянием второй группы входов элемента 2И-ИЛИ 17.2.

Переход на работоспособную структуру при отказе первого, третьего или четвертого разрядов производится аналогичным образом.

Таким образом, в двоичном счетчике осуществляется автоматическая реконфигурация работоспособной структуры при отказе одного из основных разрядов, что создает возможность обеспечения работоспособности логических блоков устройств автоматики и вычислительной техники без замены данной интегральной микросхемы и, следовательно, повышает эксплуатационную отказоустойчивость двоичного счетчика.

Формула изобретения

Двоичный счетчик, содержащий два элемента И, два элемента EIE, .два. элемента ИЛИ-НЕ и разряды, каждый. из которых содержит триггер, элемент

ЗИ-ИЛИ и первый элемент И-НЕ, синхровход счетчика соединен с входом первого элемента HF., выход которого. соединен с синхровходом триггера каждого разряда, вход установки в

"0" счетчика соединен с входом второго элемента НЕ, выход которого соединен с первым входом первого элемента ИЛИ-НЕ, первым входом второго элемента ИЛИ-НЕ и инверсным входом второго элемента И, первый вход управления режимом работы счетчика соединен с вторыми входами вторых элементов ИЛИ-НЕ и И, вход разрешения переноса счетчика соединен с первым входом первого и третьим входом второго элементов И счетчика, второй вход управления режимом работы счетчика соединен с четвертым входом второго элемента И, выход которого соединен с первыми входами первых элементов И-НЕ и первыми входами вторых групп входов элементов ЗИ-ИЛИ каждого разряда, входы предварительной установки счетчика соединены соответственно с вторыми входами первых групп входов элементов ЗИ-ИЛИ одноименного разряда, выход первого злемента ИЛИ-НЕ счетчика соединен с вторым входом третьей группы входов элемента ЗИ-ИЛИ

55 каждого разряда, выход второго элемента ИЛИ-НЕ, счетчика соединен с вторым входом первого элемента И-НЕ и с первым входом первой группы входов элемента ЗИ-ИЛИ каждого разряда, выход элемента И-НЕ,каждого разряда соединен с третьим входом третьей группы входов элемента ЗИ-ИЛИ одноименного разряда, о т л и ч а ю— шийся тем, что, с целью повышения эксплуатационной отказоустойчивости двоичного счетчика, в него введены резервный разряд, содержащий триггер, второй элемент И-НЕ и элемент 2И-ИЛИ, а каждый основной разряд дополнительно. содержит элемент

И/И-НЕ, каждый основной, кроме первого, разряд дополнительно содержит элементы 2И-ИЛИ-НЕ и 2И-ИЛИ, первый разряд дополнительно содержит второй элемент И-НЕ, входы запрета работы соответствующего разряда счетчика соединены соответственно с первыми входами элемента И/И-HE одноименного разряда, прямой выход элемента И/И-НЕ первого разряда соединен с вторым входом второго элементаИ-НЕ одноименного, с вторым входом элемента И/И-НЕ и с вторым входом первой группы входов элемента 2И-ИЛИ;. второго разряда„ инверсный выход

И/И-HE первого, второго и третьего разрядов соединены соответственно с вторыми входами первых групп входов элементов 2И-ИЛИ-HE и первыми входами вторых групп входов элементов 2И-ИЛИ последующих разрядов, инверсный выход элемента И/И-НЕ четвертого разряда соединен с вторым входом второго элемента И-НЕ и первым входом второй группы входов элемента

2И-ИЛИ резервного разряда, прямой выход элемента И/И-HE второго и третьего разрядов соединен с первым входом второй группы входов элемента 2И-ИЛИНЕ одноименного, вторым входом элемента И/И-НЕ и с вторым входом первой группы входов элемента 2И-ИЛИ последующего разрядов, прямой выход элемента И/И-НЕ четвертого разряда соединен с первым входом второй группы входов элемента 2И-ИЛИ-HF. одноименного и вторым входом первой группы входов элемента 2И-ИЛИ резервного разрядов, выход элемента ЗИ-ИЛИ первого разряда соединен с первым входом второго элемента И-НЕ одноименного и первым входом первой группы входов

Составитель О. Скворцов

Редактор Л. Пчолинская Техред М.Дидык Корректор Д, Бескид

Заказ 3150 Тираж 659 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГЕНТ СССР

113035, Москва, Ж-35, Раушская каб., д. 4 /5

Производственно-издательский комбинат "Патент", r.Óæãîðîä, ул. Гагарина, 10 1

l5 15999 элемента 2И-ИЛИ-HE второго разрядов, выходы элементов ЗИ-ИЛИ второго и третьего разрядов соединены с вторым входом второй группы входов элемента

2И-ИЛИ-НЕ одноименного и первым входом первой группы входов элемента 2ИИЛИ-НЕ последующего разряда, выход элемента ЗИ-ИЛИ четвертого разряда соединен с вторым входом второй груп-10 пы входов элемента 2И-ИЛИ-НЕ одно.именного и первым входом второго элемента И-НЕ резервного разрядов, выход второго элемента И-HE первого разряда соединен с инверсным D-вхо15 дом триггера одноименного разряда, прямой выход которого соединен с первым входом первой группы входов элемента 2И-ИЛИ второго разряда, выход элемента 2И-ИЛИ-HF. второго раз20 ряда соединен с инверсным D-входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов элемента 2И-ИЛИ одноименного и с первым входом первой группы входов элемента

2И-ИЛИ третьего разрядов, выход элемента 2И-ИЛИ-НГ третьего разряда соединен с инверсным входом D-триггера одноименного разряда, прямой выход которого соединен с вторым входом . второй группы входов элемента 2И-ИЛИ одноименного и с первым входом первой группы входов элемента 2И-ИЛИ четвертого разрядов, выход элемента

2И-ИЛИ-НЕ четвертого разряда соединен

/, с инверсным D-входом триггера одноименного разряда, прямой выход которого соединен с вторым входом второй группы входов элемента 2И-ИЛИ одноименного и первым входом первой группы входов элемента 2И-ИЛИ резервного разрядов, выход второго элемента И-НЕ резервного разряда соединен с инверсным D-входом триггера одноименного разряда, прямой выход которого соеди45 нен с вторым входом второй группы холов элемента 2И-ИЛИ резервного разряда, синхровход триггера резервного разряда соединен с выходом первого элемента HE счетчика, выход элемента 2И-ИЛИ второго разряда является первым разрядным выходом счетчика и соединен с вторым входом первого элемента И счетчика, инверсным входом второй, первым входом третьей групп входов элемента ЗИ-ИЛИ первого, вторым входом второй группы входов элемента ЗИ-ИЛИ, вторым входом первого элемента И-НЕ второго, вторым входом второй группы входов элемента ЗИ-ИЛИ, вторым входом первого элемента И-НЕ третьего, вторым входом второй группы входов элемента ЗИ-ИЛИ и вторым входом первого элемента И-HF. четвертого разрядов, выход элемента 2И-ИЛИ третьего разряда является вторым разрядным выходом счетчика и соединен с третьим входом первого элемента И счетчика инверсным входом второй и первым ° входом третьей групп входов элемента ЗИ-ИЛИ второго, третьим входом второй группы входов эле- мента ЗИ-KBI, третьим входом первого элемента И-HE третьего, третьим входом второй группы входов элемента

ЗИ-ИЛИ и третьим входом первого элемента И-НЕ четвертого разрядов, выход элемента 2И-ИЛИ четвертого разряда соединен с четвертым входом первого элемента И счетчика, инверсным входом второй и первым входом третьей групп входов элемента ЗИ-ИЛИ третьего, четвертым входом второй группы входов элемента ЗИ-ИЛИ и четвертым входом первого элемента И-НЕ четвертого разрядов и является третьим разрядным выходом счетчика, выход элемента 2И-ИЛИ резервного разряда соединен с пятым входом первого элемента И счетчика, инверсным входом второй и первым входом третьей групп входов элемента ЗИ-ИЛИ четвертого разряда и является четвертым разрядным выходом счетчика. !