Преобразователь четырехпозиционного временного кода в двоичный код

Иллюстрации

Показать всеРеферат

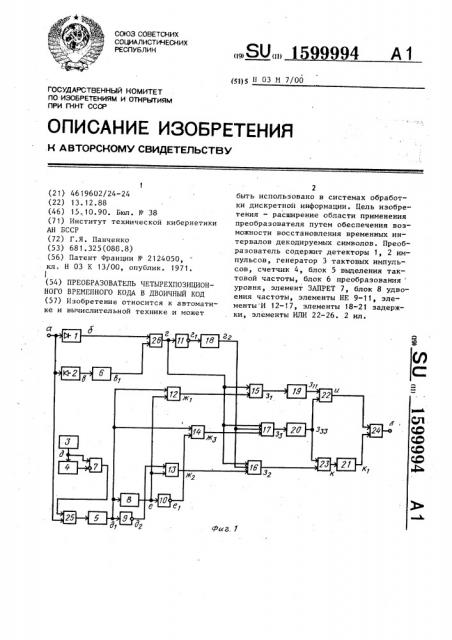

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обработки дискретной информации. Цель изобретения - расширение области применения преобразователя путем обеспечения возможности восстановления временных интервалов декодируемых символов. Преобразователь содержит детекторы 1,2 импульсов, генератор 3 тактовых импульсов, счетчик 4, блок 5 выделения тактовой частоты, блок 6 преобразования уровня, элемент ЗАПРЕТ 7, блок 8 удвоения частоты, элементы НЕ 9-11, элементы И 12-17, элементы 18-21 задержки, элементы ИЛИ 22-26. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (1)5 Н 03 М 7/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 46 19602/24-24 (22) 13. 12. 88 (46) 15. 10. 90. Бюл. № 38 (71) Институт технической кибернетики

АН БССР (72) Г.Я. Панченко (53) 681.325(088.8) (56) Патент Франции ¹ 2124050, кл. Н 03 К 13/00, опублик. 197 I ! (54) ПРЕОБРАЗОВАТЕЛЬ ЧЕТЫРЕХПОЗИЦИОННОГО ВРЕМЕННОГО КОДА В ДВОИЧНЫЙ КОД (57) Изобретение относится к автоматике и вычислительной технике и может

ÄÄSUÄÄ 15 9994 А1

2 быть использовано в системах обработки дискретной информации. Цель изобретения — расширение области применения преобразователя путем обеспечения возможности восстановления временных интервалов декодируемых символов. Преобразователь содержит детекторы 1, 2 импульсов, генератор 3 тактовых импульсов, счетчик 4, блок 5 выделения тактовой частоты, блок 6 преобразования уровня, элемент ЗАПРЕТ 7, блок 8 удвоения частоты, элементы НЕ 9-11, элементы И 12-17, элементы 18-21 задержки, элементы ИЛИ 22-26. 2 ил.

1599994

Изобретение относится к автоматике ивычислительной технике и может быть использовано в системах обработки дискретной информации, Цель изобретения — расширение об5 ласти применения преобразователя за счет обеспечения воэможности восстановления временных интервалов декодируемых символов. 10

kla фиг, 1 представлена функциональная схема преобразователя; на фиг,,2 временные диаграммы,.поясняющие его работу,, Преобразователь 4-позиционного временного кода в двоичный код,фиг.1, содержит детекторы 1, 2 импульсов, генератор 3 тактовых импульсов, счетчик 4, блок 5 выделения. тактовой час-. тоты, блок 6 преобразования уровня, элемент ЗЛПРЕТ 7, блок 8 умножения частоты, элементы НЕ 9-11, элементы

И 12-17, элементы 18-21 задержки, элементы ИЛИ 22-26.

Преобразователь 4-позиционного временного кода в двоичный код работает следующим образом.

После включения электропитания преобразователя сигнал начального сброса, выработанный внешним устройством, устанавливает двоичный счетчик 4 в исходное состояние. При этом с выхода генератора 3 через последовательно соединенные открытый элемент 7 запрета и элемент ИЛИ 25 на вход блока 5 выделения тактовой частоты поСтупает последовательность тактовых импульсов с длительностью

T /2, следующих с номинальной тактовой частотой Г- = 1/T. (фиг. 2ф), ко40 торая обеспечивает запуск и сипхронизацию блока 5.

С выхода генератора 3 последовательность тактогых импульсов поступает одновременно на вход двоичного счетчика 4, который после окончания установленного счета импульсов переполняется и положительным потенциалом со своего выхода закрывает элемент 7, что предотвращает прохождение через него импульсов с выхода генератора и

50 обеспечивает работу блока 5 в автономном режиме.

Перед началом приема информационного массива на вход преобразователя поступает синхросигнал тактовой часто 5 ты с длительностью импульсов Т /2 (меандр), передние фронты импульсов в котором совпадают с началом тактоного интервала Т, что обеспечивает работу блока 5 в режиме синхронизации входной последовательностью импульсов, поступающей на вход устройства.

При этом разнополярный 4-позиционный сигнал с длительностью импульсов

Т /2 в тактовом интервале Т, следующих с номинальной тактовой частотой

Г, сформированный по заданному алгоритму (2В -+1T) и передние фронты импульсов в котором совпадают с началом и с серединой тактового интервала Ти сдвинуты по отношению к его началу на величину T>/4 (фиг. 2ц), поступает на входы детекторов 1 и 2, с помощью которых разделяется соответственно на последовательности положительных (фиг.28) и отрицательных (фиг.2e) импульсов, а также поступает через элемент 25 на вход блока 5 выделения тактовой частоты и обеспечивает его работу в режиме синхронизации.

Затем последовательность положительных импульсов с выхода детектора

1 непосредственно (фиг.26), а после— довательность отрицательных импульсов с выхода детектора 2 — через блок 6 преобразования уровня, обеспечивающий преобразование отрицательных импульсов (фиг.2 g) в положительные (фиг.2b), поступает к входам элемента

26, сформированный однополярный сигнаг.. с выхода которого (фиг. 2 ) на одни входы элементов И 15, 16 и 17 поступает Йепосредственно, а на другие входы элементов 16 и 17 — через последовательно соединенные элемент 11 (фиг.2г) л и элемент 18 задержки на величину Т /4 (фиг. 2 ) ..

С выхода блока 5 последовательность тактовых импульсов (фиг.2),) поступает к входам элементов 12 и. 1 4, другие входы которых непосредственно и через элемент НЕ 10 (фиг. 2a,) подключены к выходу блока 8 умножения частоты на "2" (фиг.22), соединенному также с соответствующим входом элемента 13, другой вход которого через элемент 9 (фиг.2 2) подключен к выходу блока 5 (фиг.2,), в результате чего на выходах элементов И 12, 13 и. 14 формируются соответственно последовательности тактовых импульсов с длительностью Т/4 (фиг,2+i Ж,i+ ), которые, поступают к .соответствующим входам элементов И15, 16 и 17 и передние фронты которых совпадают соответ9994 6

Ф о р м у л а .и s о б р е т е н и я

5 159 ственно с передними фронтами входных импульсов, поступающих с выхода элемента 26 (фиг.2Z) на первые входы элементов И 15, 16 и 17 и совпадающих соответственно с началом (фиг.2,) и с серединой (фиг.24 ) тактового интервала Т и сдвинутых по отношению к

его началу на величину Т /4 (фиг.2йз)

В результате суммирования входных сигналов, поступающих на входы элементов И 15, 16 и 17 совместно с последовательностями тактовых импульсов с длительностью Т /4 (фиг.2Ас, ж,Ас ) обеспечивается соответственно разделе ние входного 4-х позиционного сигнала (фиг.2q) по временному положению импульсов в тактовом интервале Т в соZ ответствии с заданным алгоритмом обратного преобразования (1Т вЂ” 2В) и формирование на выходах элементов

И 15, 16 и 17 (фиг.2з,,э„ь ) импульсов с длительностью Т /4, отображающих соответственно комбинации из двух двоичных символов 10, 01 и 11 из которых был сформирован по заданному алгоритму прямого преобразования (2 — 1Т) входной 4-позиционный сигнал (фиг.2 ol).

При этом с выхода элементов 15 и

16.сигналы через элемент 19 задержки на величину Tz/2 (фиг.23„) и непосредственно поступают к входам элементов ИЛИ 22 и 23, другие входы которых через элемент 20 за,!ержки на величину

Т /4 = T< /2 (фиг. 2 3+ подключены к выходу элемента 17 (фиг.2З ), в pезультате чего на выходах элементов 22 (фиг. 20) и 23 (фиг. 2 К) формируются соответствующие параллельные комбинации из двух двоичных символов с длительностью импульсов Т (/2, которые с их выходов (фиг.20,r)непосредственно и через элемент 21 задержки на величину Т (фиг.2 К,) поступают к входам элемента 24, на выходе которого формируется восстановленная исходная двоичная последовательность длительностью импульсов T /2, следующих с но-. минальной тактовой частотои F = 1/T4 =

1у Т>/2 = 2F g (фиг.2Л) .

Преобразователь четырехпозиционного временного кода в двоичный код, содержащий блок преобразования уровня, первый — шестой элементы И, первый, второй и третий элементы ИЛИ, первый и второй элементы НЕ, первый и второй детекторы импульсов, вход первого детектора импульсов является информационным входом преобразователя, выход первого элемента ИЛИ является выходом преобразователя, о т л и ч а юшийся тем, что, с целью расширения области применения преобразователя путем обеспечения возможности восстановления временных интервалов декодирующих символов, в него введены элемент ЗАПРЕТ, счетчик, четвертый, пятый элементы ИЛИ, третий элемент

НЕ, блок .умножения частоты, блок выделения тактовой частоты, первый— четвертый элементы задержки и генератор тактовых импульсов, выход которого соединен с первым входом счетчика и прямым входом элемента ЗАПРЕТ, выход которого соединен с первым входом второго элемента ИЛИ, выход которого через блок выделения тактовой частоты соединен с первыми входами первого и второго элементов И, входами первого элемента НЕ и блока удвоения частоты, выход которого соединен с вторым входом первого элемента И, первым входом третьего элемента И и через второй элемент НЕ " с вторым входом второго элемента И, выход которого соединен с первым входом четвертого элемента И, выход которого через первый элемент задержки соединен с первыми входами . третьего и четвертого элементов ИЛИ, выход первого элемента НЕ соединен с вторым входом третьего элемента И, выход которого соединен с первым входом пятого элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого через второй элемент задержки соединен е первым входом первого элемента ИЛИ, 1 второй вход второго элемента ИЛИ и вход второго детектора импульсов сое-

Таким образом, предложенное устройство для преобразования 4-позиционного временного кода в двоичный код обеспечивает восстановление временных интервалов декодируемых символов путем преобразования 4-позиционного сигнала в двоичный. динен с информационным входом преобразователя, выход первого детектора импульсов соединен с первым входом пятого элемента KIH; выход которого, соединен с вторыми входами четвертого и пятого элементов И, с первым входом шестого элемента И и через последовательно соединенные третий

159999ч

Фиг. 2

Составитель С. Берестевич

Техред М.Дидык Корректор С. Ыекмар

Редактор М. Товтин

Заказ 3151 Тираж 658 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, . осква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина,101 элемент НЕ и третий элемент задержки — с третьими входами четвертого и пятого элементов И, выход первого элемента И соединен с вторым входом шестого элемента И, выход которого через четвертый элемейт задержки соединен с вторым входом третьего элемента ИЛИ,,выход которого соединен с вторым входом первого элемента

ИЛИ, выход второго детектора импульсов через блок преобразования уровня соединен с вторым входом пятого элемента ИЛИ, второй вход счетчика является входом сброса преобразователя, выход счетчика соединен с инверсным входом элемента ЗАПРЕТ,