Патент ссср 160039

Иллюстрации

Показать всеРеферат

Подписная группа № 145

Г. Ф. Кучеров и В. И. Максимова

СПОСОБ РЕАЛИЗАЦИИ ТЕРНАРНОГО КОДИРОВАНИЯ

ПРИРАЩЕНИИ В БИНАРНЫХ ЦИФРОВЫХ

ДИФФЕРЕНЦИАЛЬНЫХ АНАЛИЗАТОРАХ

ПОСЛЕДОВАТЕЛЬНОГО ТИПА

Известны способы реализации тернарного кодирования прнраше ий в бпнаоных цифровых дифференциальных анализаторах (ЦДА) последовательного типа.

Предложенный способ отличается от известных тем, что для устранения фазовых (флуктуационных) ошибок, на входы накапливающих регистров У и Я подают приращения (положительные или отрицательные) в случае, когда в последовательности переполнений интегратора имеются два соседних переполнения с одинаковыми знаками.

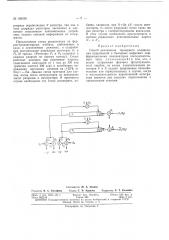

На чертеже представлена функциональная схема устройства, с помощью которого реализуется тернарный способ кодирования в бинарных ЦДА.

Схема состоит из двух одинаковых сдвигающих регистров Р> и Р2 с прецессией и восьми вентилей Bj — B>, из которых вентили Вз и В4 являются вентилями несовпадения, а все остальные — вентилями совпадения.

Переполнение AS,. интегратора (интегратор на чертеже не показан) и его инверсия ЛЯ; в последовательности переполнений Р„ также подаются на вход регистров Р и Р2 через вентили В, и В„на которые в этом же такте в зависимости от знака приращения, полученного на выходе данного интегратора в i — 1 шаге интегрирования, поступает или приращение AS, — 1 или его инверсия Л5,.— 1. Если

AS,— 1=1 и AS 1, то запись приращения производится в регистре Рь а если AS,— 1=1 и ЛЯ; =1, то в регистре P . При всех остальных комбинациях запись приращений в регистры не производится. Записанное приращение в каждом малом цикле работы интегратора сдвигается в регистрах с прецессией.

Для осуществления прецессии выходные импульсы из регистра Pl(P2) подаются в течение итерации через вентиль В (В4) на вход предпоследнего разряда регистра P, (P>) . B следующей итерации ранее записанное при- ращение заменяется новым, для чего в регистре Р; также на выход вентиля Вз(В4) поступает управляющий импульс, который запрещает перезапись ранее записанного приращения.

Выходной импульс, как и в обычном бинарном ЦДА, из регистра P>(P>) поступает на соответствующие устройства ЦДА через вентили В;, Вв(„ ), на которые подаются управляющие импульсы А, и А», представляющие собой адреса приращений Л,„A, Если приращение данного интегратора йоложительное, то оно в зависимости от адреса А или

А у снимается из вентиля В,- или В . Если приращение отрицательное, то оно снимается из вентиля В7 или В8. Приращение AS; — -1 с целью экономии оборудования можно хранить в младшем разряде R регистра или же в б

Ме 160039

/1 5((Рп) Составитель Ж. А, Зимина

Редактор Н. С. Кутафина Техред T. П. Курилко Корректор P. Т. Келембет

Подп. к печ. 18/II — 64 г. Формат бум. 60Х90 /в Объем 0,23 изд. л.

Заказ 3623/16 Тираж 650 Цена 5 коп

ЦНИИПИ Государственного комитета по делам изобретений и открытий СССР

Москва, Центр пр. Серова, д. 4

Типография, пр. Сапунова, 2 разряде переполнения У регистра, так как в этих разрядах регистров, засланных в магнитное оперативное запоминающее устройство, обычно никакой информации не содержится.

Предлагаемая схема реализована на феррит-транзисторных ячейках, работающих в одно- и двухтактном режимах, и содержит при восемнадцати разрядных регистрах Р, и

Р2 52 триода. (Регистры Р, и Р2 содержат в каждом разряде по одному триоду). Схема работает надежно при изменении частоты сдвигающих импульсов от 1 кгпв до 300 кгпв (рабочая частота 200 кгпв) и колебаниях напряжения источника питания на +25 /о от

Екн= — 15в. Данная схема пригодна для случая, когда число интеграторов не превышает числа разрядов в интеграторе. В противном случае необходимо эту схему расширить, добавив, например, при N=2n (N — число интеграторов, n — число разрядов) точно такие же два регистра с соответствующими вентилями.

В этом случае необходимо предусмотреть в системе управления дополнительные адреса

А и А

Предмет изобретения

Способ реализации теонарного кодирования приращений в бинарных цифровых дифференциальных анализаторах последовательного типа, отличающийся тем, что, с целью устранения фазовых (флуктуационных) ошибок, на входы накапливающих регистров У и R подают приращения (положительные или отрицательные) в случае, когда в последовательности переполнений интегратора имеются два соседних переполнения с одинаковыми знаками.