Цифровой частотный детектор

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике. Цель изобретения - уменьшение искажений производной гармонической модулирующей ф-ции на выходе детектора и расширение диапазона частот модулирующей ф-ции. Детектор содержит формирователь 1, D-триггер 2, каналы 3-6 обработки сигнала, эл-т ИЛИ 7, фильтры 8 и 9 нижних частот, дифференциальный усилитель 10 и блоки переменной задержки /БПЗ/ 11 и 12 импульсов, состоящие каждый из JK-триггеров 13 и 20, N-разрядного двоичного реверсивного счетчика 14, эл-тов И 15 и 16, двоичного N-разрядного счетчика 17, цифрового компаратора 18 и эл-та задержки 19. На эл-т ИЛИ 7 поступают импульсы из каналов 5 и 6, а также из каналов 3 и 4, но задержанные с помощью БПЗ 11 и 12. На выходе эл-та ИЛИ 7 возникает непрерывная последовательность импульсов, в которой каждый импульс имеет одну и ту же временную синхронизацию. Информация заключена в изменении скважности этих импульсов под действием модулирующего сигнала. Достижение одной и той же временной синхронизации информационных импульсов обеспечивает устранение искажений производной гармонической модулирующей ф-ции и дает возможность повысить частоту среза фильтра 8, что расширяет диапазон частот гармонической ф-ции. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (Ф1)5 Н 03 0 3/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

0 (61) 1376226 (21) 4626418/24-09 (22) 27.12.88 (46) 23.10.90. Бюл, № 39 (72) В.И.Закиров и И,В.Закиров (53) 621.376.3 (088.8) (56) Авторское свидетельство СССР

¹ 11337766222266, кл. Н 03 D 3/00, 03.01.85. (54) ЦИФРОВОЙ ЧАСТОТНЫЙ ДЕТЕКТОР (57) Изобретение относится к радиотехнике.

Цель изобретения — уменьшение искажений производной гармонической модулирующей ф-ции на выходе детектора и расширение диапазона частот модулирующей ф-ции.

Детектор содержит формирователь 1, Dтриггер 2, каналы 3-6 обработки сигнала, эл-т ИЛИ 7, фильтры 8 и 9 нижних частот, дифференциальный усилитель 10 и блоки переменной задержки(БПЗ) 11 и 12 импульсов, состоящие каждый из IK-триггеров 13 и

„„59„„1601740 А2

20, и-разрядного двоичного реверсивного счетчика 14, эл-тов И 15 и 16, двоичного и-разрядного счетчика 17, цифрового компаратора 18 и эл-та задержки 19. На эл-т

ИЛИ 7 поступают импульсы из каналов 5 и

6, а также из каналов 3 и 4, но задержанные с помощью БПЗ 11 и 12. На выходе эл-та

ИЛИ 7 возникает непрерывная последовательность импульсов, в которой каждый импульс имеет одну и ту же временную синхронизацию. Инфсрмация заключена в изменении скважности этих импульсов под действием модулирующего сигнала. Достижение одной и той.же временной синхронизации информационных импульсов обеспечивает устранение искажений производной гармонической .модулирующей ф-ции и дает возможность повысить частоту среза фильтра 8, что расширяет диапазон частот гармонической ф-ции. 3 ил.

1607 740

Изобретение относится к радиотехнике, может быть использовано в радиоприемных устройствах для частотного детектирования в широком диапазоне частот и является усовершенствованием цифрового частотного детектора по авт, св.

hL 1376226.

Целью изобретения является уменьшение искажений производной гармонической модулирующей функции на выходе детектора и расширение диапазона частот модулирующей функции.

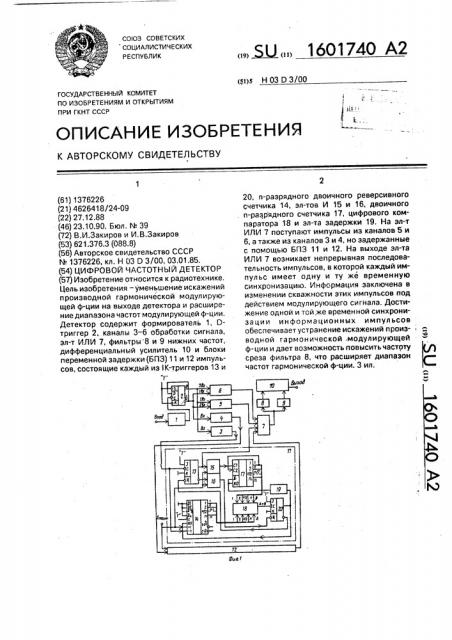

На фиг.1 представлена структурная электрическая схема цифрового частотного детектора; на фиг.2 — диаграмма работы цифрового частотного детектора; на фиг.3— диаграмма работы блока переменной задержки импул ьса.

Цифровой частотный детектор содержит входной формирователь 1, D-триггер 2, первый 3 и второй 4 каналы обработки сигнала, первый 5 и второй 6 дополнительные каналы обработки сигнала, элемент ИЛИ 7, первый 8 и второй 9 фильтры нижних частот, дифференциальный усилитель 10, первый

11 и второй 12 блоки переменной задержки импульсов.

Каждый из блоков переменйой задержки импульсов содержит первый IK-триггер

13, и-разрядный двоичный реверсивный счетчик 14, первый 15 и второй 16 элементы

И, двоичный п-разрядный счетчик 17, цифровой компаратор 18, элемент 19 задержки и второй IK-триггер 20.

Детектор работает следующим образом.

Допустим, что на вход детектора поступает частотно-модулированный сигнал. Под действием модулирующего сигнала (фиг.2а) происходит изменение мгновенного значения несущей частоты (фиг.2б). На интервалах времени t< — tz и тз — t4 несущая частота возрастает, на интервале времени t2 — ta несущая частота убывает. При возрастании несущей частоты работают первый 5 и второй

6 дополнительные каналы. При этом на выходе элемента ИЛИ 7 возникают пачки импульсов, Каждый импульс этих пачек возникает при изменении напряжения несущей частоты от максимального значения до минимального. Передний фронт этих импульсов совпадает с моментом прохождения через нулевое состояние напряжения несущей частоты (фиг.3в),при уменьшении несушей частоты работают первый 3 и второй 4 каналы, Импульсы на выходах этих каналов сдвинуты во времени на величину собственной длительности в сторону опережения (фиг.2г). Задний фронт этих импульсов совпадает с моментом перехода через

55 нулевое состояние напряжения несущей частоты, изменяющегося от плюса к минусу.

Затем указанные импульсы с помощью блоков переменной задержки импульсов подвергаются операции задержки во времени на величину собственной длительности (фиг.2д). Блок 11 переменной задержки импульсов задерживает импульсы, поступающие с выхода первого 3 канала, а блок 12 переменной задержки — импульсы, поступающие с выхода второго канала 4 обработки сигнала, На выходе элемента ИЛИ 7 возникает непрерывная последовательность импульсов, в которой каждый импульс имеет одну и ту же временную синхронизацию.

Информация заключена в изменении скважности этих импульсов под действием модулирующего сигнала. Достижение одной и той же временной синхронизации информационных импульсов обеспечивает устранение искажений производной гармонической модулирующей функции и дает возможность повысить частоту среза первого фильтра 8 нижних частот, так как критерием ее выбора становится обеспечение подавления сигналов нижних боковых частот несущей частоты, а не гармоник модулирующей функции как в известном детекторе, Новый критерий выбора частоты среза обеспечивает расширение диапазона частот гармонической функции.

В предлагаемом детекторе непрерывную последовательность импульсов на выходе элемента ИЛИ 7 в первом приближении можно представить как модулированную по частоте повторения гармоническим модулирующим сигналом последовательность положительных прямоугольных импульсов.

Спектр такой последовательности определяется выражением (1) В пт 2 kBmCm 1 Qt Х

Т Т 2 х cos Q(t — )+ g x

x ), — imp(kneCm) х

p — — — C6 "

X SII1 -"-: .." — -" Х

x cos ((и а — р 9)t+ 2 ), где Bm — амплитуда импульсов; - длительность импульсов;

Cm — амплитуда сигнала модулирующей частоты, вызывающего модуляцию импульCGB; к — коэффициент пропорциональности, определяющий глубину модуляции; в- среднее значение несущей частоты;

1601740

0 = 2 л F. = 2 к T- круговая частота модулирующего сигнала.

Из выражения (1) следует, что в спектре сигнала на выходе элемента ИЛИ 7 содерВ„х жится постоянная составляющая ., сигнал производной гармонической х модулирующей функции cos Q (t — — ), сигнал несущей частоты и ее гармоник

cos n а, сигналы боковых частот несущей частоты и ее гармоник cos(n в+ р И) .

С помощью дифференциального усилителя 10 устраняется постоянная составляющая, а с помощью фильтров 8 и 9 — сигналы несущей частоты и ее гармоник, а.также сигналы боковых частот. В итоге выделяется неискаженный сигнал производной гармонической модулирующей функции, так как в спектре отсутствуют B отличие от известного детектора гармоники модулирующей частоты.

В известном же устройстве сигнал выделенной модулирующей функции имеет деформированный вид, Положительная полуволна короче отрицательной полуволны P1 < Т2, T1 + T2 = Т, где Т вЂ” период исходной модулирующей функции (фиг.2е и ж — сплошные линии)).Эта деформация вызвана тем, что полуволна модулирующей функции, соответствующая интервалам времени уменьшения несущей частоты, выделяется с опережением во времени на интервал Лt или в угловом масштабе — на

Л<р.

В блоках 11 и 12 переменной задержки импульсов во время поступления импульса с выхода соответствующего канала на вход разрешения счета на сложение двоичного реверсивного счетчика 14 последний осуществляет счет импульсов тактовой частоты, поступающих на его счетный вход(интервал времени tq — т2 на фиг.3а). К моменту окончания счета в памяти двоичного реверсивного счетчика 14 записывается некоторое число

А, которое равно отношению периода импульсов, поступающих с выхода соответствующего канала к периоду тактовой частоты (фиг.36), В это время число импульсов, сосчитанных двоичным счетчиком 17, равно нулю, т.е.число В= О. Поэтому на выходе А> В цифрового компаратора 18 возникает потенциал логической единицы (фиг.Зг). В момент времени тз первый IK-триггер 13 переходит в состояние логической единицы по прямому выходу (фиг.Зж). При этом импульсы тактовой частоты через первый элемент И 15 поступают на первый счетный вход двоичного счетчика 17, который осуще5

10 кции на выходе частотного детектора и

55 расширения диапазона частот модулирующей функции, между выходом первого каналаобработки информации и первым входом элемента ИЛИ введен первый блок переменной задержки импульсов, а между выходом второго канала обработки информации

50 ствляет счет импульсов в течение интервала времени ts-t4. В момент времени т4 число импульсов, сосчитанных двоичным счетчиком 17, равно числу импульсов, сосчитанных двоичным реверсивным счетчиком 14, т.е. число А станет равным числу В (фиг.За). Поэтому на выходе цифрового компаратора 18 произойдет перепад напряжения от уровня логической единицы до уровня логического нуля, под действием которого второй 1Ктриггер 20 перейдет в состояние логической единицы па прямому выходу (фиг.Зд) и в состояние логическага нуля па инверсному выходу (фиг.Зе). При этом произойдет установка в нулевое состояние сначала перваго tK-триггера 13, а затем с некоторой задержкой — двоичного счетчика 17. Установка в нуль произойдет также в двоичном реверсивном счетчике 14. С появлением потенциала логической единицы на инверсном выходе первого lK-триггера 13 обеспечивается поступление импульсов тактовой частоты через второй элемент И 16 на вход установки в нуль второго tK-триггера 20. С приходом первого импульса тактовой частоты на указанный вход второй

iK-триггер 20 вновь возвращается в состояние логического нуля по прямому выходу.

Импульс, возникающий на прямом выходе первого IK-триггера 13, равен по длительности с точностью до периода тактовой частоты импульсу, поступающему на вход блока переменной задержки (фиг.Зж), Однако во времени этот импульс смещен на интервал времени t1 — t2 который с указанной точностью равен интервалу времени тз-т4.

Таким образом, блок переменной задержки импульсов осуществляет задержку поступающих на его вход информационных импульсов на время, равное длительности этих импульсов. Длительность импульсов определяется отношением девиации несущей частоты к ее среднему значению, т.е. она переменна. Этим определяется название блоков переменной задержки импульсов. Точность задержки определяется параметрами блоков переменной задержки импульсов.

Формула изобретения

Цифровой частотный детектор по авт. св. ¹ 1376226, отличающийся тем, что, с целью уменьшения искажений производной гармонической модулирующей фун1601740 и вторым входом элемента задержки введен второй блок переменной задержки импульсов, при этом каждый блок переменной задержки импульсов содержит первый

IK-триггер, С-вход которого является входом блока переменной задержки импульсов, выходом которого является прямой выход IK-триггера, который подключен к первому входу первого элемента И, инверсный выход первого IK-триггера подключен к первому входу второго элемента И, последовательно соединенные и-разрядный двоичный реверсивный счетчик, прямой и инверсный входы которого подключены соответственно к вторым входам первого и второго элементов И и к С-входу первого

IK-триггера, компаратор, второй (К-триггер, R-вход и инверсный выход которого подключены соответственно к выходу второго элемента И и к R-входу первого (К-триггера, элемент задержки и и-разрядный двоичный счетчик, первый из и выходов и и выходов

5 которого подключены соответственно к второму счетному входу и-разрядного двоичного счетчика и и информационным входам компаратора, при этом прямой и инверсный выходы второго (К-триггера подключены со10 ответстценно к входам установки в "0" иразрядного двоичного реверсивного счетчика и первого (К-триггера, (-вход которого и I-вход второго триггера являются вхо. дом логической единицы цифрового

15 частотного детектора, а К-входы первого и второго IK-триггеров и информационные входы и-разрядного двоичного реверсивного счетчика подключены к общей шине.

1601740

Составитель Л.Тимошина

Техред М.Моргентал Корректор М. Самборская

Редактор Н.Рогулич

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101

Заказ 3277 Тираж 656 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва; Ж 35, Раушская наб., 4/5