Устройство тактовой синхронизации

Иллюстрации

Показать всеРеферат

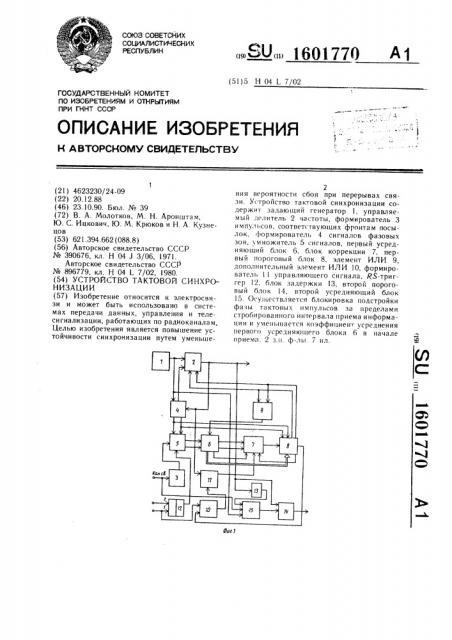

Изобретение относится к электросвязи может быть использовано в системах передачи данных, управления и телесигнализации, работающих по радиоканалам. Целью изобретения является повышение устойчивости синхронизации путем уменьшения вероятности сбоя при перерывах связи. Устройство тактовой синхронизации содержит задающий генератор 1, управляемый делитель 2 частоты, формирователь 3 импульсов, соответствующих фронтам посылок, формирователь 4 сигналов фазовых зон, умножитель 5 сигналов, первый усредняющий блок 6, блок коррекции 7, первый пороговый блок 8, элемент ИЛИ 9, дополнительный элемент ИЛИ 10,формирователь 11 управляющего сигнала, RS-триггер 12, блок задержки 13, второй пороговый блок 14, второй усредняющий блок 15. Осуществляется блокировка подстройки фазы тактовых импульсов за пределами стробированного интервала приема информации и уменьшается коэффициент усреднения первого усредняющего блока 6 в начале приема. 2 з.п. ф-лы, 7 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1601770 (51)5 Н 04 1 7/02

ОПИСАНИЕ ИЗОБРЕТЕНИР

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flQ ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4623230/24-09 (22) 20.12.88 (46) 23.10.90. Бюл. № 39 (72) В. А. Молотков, М. Н. Ароншта м, Ю. С. Ицкович, Ю. М. Крюков и H. А Кузнецов (53) 621.394.662 (088.8) (56) Авторское свидетельство СССР № 390676, кл. Н 04 J 3/06, 1971

Авторское свидетельство СССР № 896779, кл. Н 04 L 7/02, 1980. (54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к электросвязи и может быть использовано в системах передачи данных, управления и телесигнализации, работающих по радиоканалам.

Целью изобретения является повышение устойчивости синхронизации путем уменьше2 ния вероятности сбоя при перерывах связи. Устройство тактовой синхронизации содержит задающий генератор I, управляемый делитель 2 частоты, формирователь 3 импульсов, соответсгвующих фронтам посылок, формирователь 4 сигналс в фазовых зон, )множитель 5 сигналов, первый усредняющий блок 6. блок коррекции 7, первый пороговый блок 8, элемент ИЛИ 9, дополнительный элемент ИЛИ 10, формирователь 1! управляющего сигнала, PS-триггер 12, блок задержки 13, второй пороговый блок 14, второй усредняющий блок

15. Осуществляется блокировка подстройки фазы Td KTQBbl x импульсов за пределами стробированного интервала приема информации и уменьшается коэффициент усреднения первого усредняющего блока 6 в начале

llðHåìë. 2 з.ll. ф- Ib!. 7 ил.!

601770

Изобретение относится к области электросвязи и может быть использовано в системах передачи данных, управления и телесигнализации, работающих по радиоканалам.

Целью изобретения является повышение устойчивости синхронизации путем уменьшения вероятности сбоя при перерывах связи.

На фиг. 1 представлена структурная электрическая схема устройства тактовой синхронизации; на фиг. 2 — 6 — структурные

:электрические схемы умножителя сигналов, первого усредняющего блока, блока коррек:.ции, первого порогового блока и формирователя управляющего сигнала, соответ:.ственно; на фиг. 7 — временные диаг;раммы сигналов, поясняющие работу устройства.

Устройство тактовой синхронизации содержит задающий генератор 1, управляе-! мый дели"-ль 2 частоты, формирователь 3

:импульсов, соответствующих фронтам посы:.ок, формирователь 4 сигналов фазовых зо;, умножитель 5 сигналов, первый усредняюц ий блок 6, блок 7 коррекции, первый пороговый блок 8, элемент ИЛИ 9, дополнитель. ый элемент ИЛИ 10, формирователь I упр,.вляющего сигнала, RS-триггер

12, блок 13 задержки, второй пороговый блок 14, второй усредняющий блок 15.

Умножитель 5 сигналов содержит элементы И---HE 16 и !7. Первый усредняющий блок 6 содержят р версивный счетчик

18 и D-триггер 19. Блок 7 коррекции содержит реверсивный счетчик 20, дешифратор 21 и элемент ИЛИ вЂ” НЕ 22.

Первый пороговый блок 8 содержит дешифратор 23, элемент И 24 и элементы И—

НЕ 25 и 26. Формирователь 11 управляющего сигнала содержит счетчик 27 импульсов, дешифратор 28 и RS-триггер 29.

Частота импульсов задающего генератора (фиг. 1) делится с помощью управляемого делителя 2, на выходе которого формируются тактовые импульсы (фиг. 7в).

На информационнь!й вход устройства тактовой синхронизации из канала связи поступает входной сигнал (фиг. 76), представляющий собой смесь кодовой посылки (фиг. 7а) и помеХи.

Из информационных посылок, поступающих из канала связи, на выходе формирователя 3 формируются короткие импульсы, совпадающие по фронту с моментом перехоьа через нуль информационных посылок фиг. 7е).

Умножитель 5 (фиг. 2) контролирует попадание этих сигналов в одну из трех зон такта, равного интервалу между соседними тактовыми импульсами: зоны отставания (фиг. 7г), зоны опережения (фиг. 7д) и зоны синхронного приема в начальной и конечной частях такта.

Зона синхронного приема расположенасимметрично относительно тактового импульса. Коррекция фазы тактовых импульсов производится, если фронты принимаемых сигна5 лов попадают в зону опережения или отста ва ни я.

Для обеспечения достаточной помехоустойчивости синхронизации фазовое рассогласование интегрируется реверсивными счетчиками 18 и 20 соответственно первого усредняющего блока 6 (фиг. 3) и блока 7 коррекции. Коррекция фазы производится, если первым пороговым блоком 8 зафиксировано определенное число импульсов рассогласования. Если фронты сигнала в канале

15 связи отстают от тактовых импульсов, то они оказываются в зоне отставания. Если фронты сигнала в канале связи опережают тактовые импульсы, то они попадают во вторую половину тактового интервала— зону опережения.

Сигналы с формирователя 4 управляют элементами И вЂ” HE 16 и 17 умножителя 5 (фиг. 2), разрешая прохождение импульсов с выхода формирователя 3 (фиг. 7е) на первый усредняющий блок 6. В зависимос25 ти от фазового положения фронтов входного сигнала относительно зоны отставания и зоны опережения реверсивные счетчики

18 и 20 работают на сложение или на вычитание.

Предварительно в реверсивные счетчики

30 18 и 20 записывак>тся числа, равные соответственно половине их емкости.

На выходах дешифраторов 23 и 21 соответственно первого порогового блока 8 и блока 7 коррекции сигналы появляются при нулевом состоянии реверсивных счетчиков 18

35 и 20, т. е. когда разность числа отстающих и опережающих импульсов равна произведению чисел, введен ных в реверсивные счетчики 18 и 20 при их предварительной установке.

Если сигнал на выходе элемента И 24 первого порогового блока 8 соответствует зоне оставания, то под действием выходного сигнала элемента И†HE 25 первого пороговбго блока 8 осуществляется увеличение коэффициента деления управляемого

45 делителя 2. Это приводит к смещению фазы тактовых импульсов в сторону отставания, т. е. уменьшает их опережение.

Если сигнал на выходе элемента И 24 первого порогового блока 8 соответствует зоне опережения, то под действием выход50 ного сигнала элемента И вЂ” HE 26 первого порогового блока 8 производится уменьшение коэффициента деления управляемого делителя 2, что приводит к противоположному смещению фазы тактовых импульсов.

Сигнал на установочный вход управля55 емого делителя 2 поступает на каждом тактовом интервале с дополнительного выхода форм-.рователя 4. Любой из выходных

7 ) сигналов первого пороговог( элемент ИЛИ 9 с помощью I

> первого усредняющего блоки импульс, осуществляющий и;< новку первого усредняющего 6:

> > ка 7 коррекции. Длительность (., .„.;нного интервала приема в квжд<>м,)икл связи определяется сигналами, ))<>ступающими на ъ1х-вход и S-вход RS-трипер:i !2.

Для ускорения вхождения Fl фазу после перерыва связи в каждом цикле связи входным управляющим сигналом через элемент ИЛИ 10 сбрасывается RS-триггер 29 формирователя 11 (фиг. 6), выходным сигналом которого с помощью элемента ИЛИ—

НЕ 22 блокируется выходной сигнал дешифратора 21, при этом коэффициент усред;)Bния определяется только реверсивным C;B" чиком 18 первого усред))яющего блока 6.

Одновременно выходной сигнал дополнительного элемента ИЛИ !<> вводит в счетчик 27 формирователя 11 число, которое 20 превьцпает в 2 раза (при равенстве количества разрядов реверсивного счетчика 8 и счетчика 27) <)исг)0, ввочимое В реверсивный счетчик 18.

Сигнал на выходе дешифратора 28 появляется при нулевом состоянии счетчика 27.

При работе устройства TBKTOBokl сННхронизации В режиме вхождения B фазу происходит периодическое формирование импульсов на выходе дешифратор» 21 первоп) порогового блока 8, поддержипающих RSтриггер 29 формирователя 1 и ))улевом состоянии. При этом содержимое счетчика 27 не успевает уменьшиться до и, )я, поэтому импульсы на выходе дешифр»тор» 28 не формируются.

При переходе устройства такговой CH«fxpoнизации В режим поддержания синфа3«tOCти интервал появления импульсов и» выходе дешифрагора 23 первого tu>p<>r<»)OIO блока 8 возрастает, в результате чего и рез интервалы времени, определяемые Koэффициентом деления счетчика 27 формироватсг!я l 1, 4О появляются импульсы на выхо Ее дешифратора 28, осуществляющи(установку В единицу RS-триггера 29 формирОВ»теля 11, благодаря чему возрасгает к зффициент ócреднения, так как при этом на Выходе элсмента И 24 первого порогОВОГО блока 8 сигнал появляется только п)>и од)и>врем )Iном появлении сигналов на вь)ходах д(!))ифратора 23 первого порогового блока 8 и я<.— шифратора 21, поскольку снимаетсЯ 6. loK)1ровка с элемента ИЛИ вЂ” НЕ 22. 110 окончании интервала приема информации Входным управляющим сигналом сбрасывается

RS-триггср !2, и его выходным нулевым сигналом блокирун)тся элементы И - HL 16 и !7 умножителя 5. нрскрашая ИО)стройку фазы тактовыx импул! Ов. 55

В уст)ойстве тактовой син . Ни ))<ин Осу)цествляегся поэлемснтный и! <" ин.«» рмац))онных с.) . Налов с помощью р<» усредп)вый блок !4, «)а Выходе которого В

Ko)! ltc каждого такта Вырабатыва Tcÿ curt! < i, I, P B B k l bl H «0», с c;1 H в ы х Од н О и с и г н а.з

l3T0p()Io интегратора не Ilp(Bûí);tcò порогоВыи уровень, и равный «! >:, если превь)шает. !

)!)Ок !8 зад pAKKH обеспечивает задерж ку обнуления второго усредняющего блока !

5 по отношени)о к моменту записи информации Во второй пороговый блок !4.

ФОр.з< )/. !Q )<3() Ор(> тРн )!ч ! YcTPoHcTt3(> тактовой сН HxPQHH3)f t«H kf, c0дсржа щее последовательно соединенные задак))ций генератор, управляемый делитель

<))Зл<>Thl, формирОВатель <ч!гназОВ фазовых зон и умножитель с)з! И)згloB. последовательно соединен ны(элемент ИЛИ. и(рвы и ус редня)о щи и блок и первый И О рого Вь) и блок, первый и второй Bi>txo;thi которого подсоединены с<)ответственно к )!(рвому и

ВТОРОМУ В Х 0 Д;1 М С И Г Н а .1 О В М ! Р «! ) 3 ТЕ Н И Я K O Э ффИllHC ttTO. >t !(10>ИИЯ » ПР;)В 111(МОГ() Д()))T<> IЯ частоты и h первому и )зто!>Ом) Входам элемента ИЛ И, последоиатслыц> с<>(диi!(>Нные второй усредн«)к))ций блок и ито! Ой порогОВый блок, )3))ход зад;))otk«cГО I < Исp B TOp;);10;I,СО(,I!! l! <> к г:1 кто ВоМ > ВХОД» (POP МИ РОВа kC:t Ff СИ ГН<.. !O!3 ф<З:ЗОВЬ) Х

:>0tl, причем информационный вход второго

) cp< дняк)щ() <> бл<>к» и B txn; управляемого

<С )ИТ(.IH ЧИСТОТI,I ЯВ1ЯК)ТСЯ (.00!ВСТСТЕЗС tlt)0 и 1) <1) О !) м l ц и О н н >I; 1 Г. О . I, ) м и В ы х ОдО м ><(T P 0 и—

СТ)З;i 0 Л«! Ч(2К>)l! « ". Я < М, IТ(), (ll(1 ЬЮ l10<зы)и(ния устойчивос.-и синхронизации путем уменьшения вероятности боя при переРЫИ;)Х СВЯЗИ, ВВЕДЕНЫ НОС:!C;tOBBTCЛЬ«!O СОЕди)ц ииыс дополнительный элемент ИЛИ, форми!)<)В<1 ) ель упр<)В Iяк)НЕ(ГО сиГн > )

h0ррекции, Выxoд которого пол:осдинеH к

))ервому дополнит(льному Bxnду .Icpttoro порогового блока,;i та кже блок задержки, К8-трипер и формирователь им::ульсов, соОТ)301 СТВ>>«01!«HХ (t)РОНТВ М iIOСI I, )OK.,ЕЗXОД И ВЬ!x0д которого подклю и иы «.)<>TB(тственно к

lit! l 0p 1B циОИ)!Омх В ХО;!3! ВтÎ j)0) (> (. p(дня к)-!

Ii(I !) 6;1oK;! и н(р)зомх:!Ot)0.)HHò(льномм Вхо3 < IOЖ И . С.! и С kl I Н IЛО B, i! PИ ЭТ<. М )ЗТОРОЙ И тр»1 )й: Оиолнитс.,ы)ые ВxO,:tt>t и первый и втор<>й 10))(>лни)< )hill>1(Выхо «ht первого пор<>ГОВОго блок;)»Олключсиы соответственно к il<. рвому и иг< ному !3!>!хОЯ»м формировате. >< сиг))алОВ ф;)зопых 30)l, tt(j))3oì>, входх д>0)><)лнительноп> э )(vc)tT;) .1 IИ и Второму упр,В IHK)ill("му )!ходу бл,. » коррекции, c)> . )и!» к) 1!) и и )3 x, 1<)>I < HT)i)< BX<)Д К< )O О ПОДКЛЮ> ц . с< ответ TB())10 к ii<. p Ому и Второму в)с ла м и< p«!i<)<:«) )<).)х. ус ановочного!

601770

0т рармиробателя 3 иггерд1Р сигнала первого усредняющего блока, прямой выход RS-триггера подсоединен к второму дополнительному входу умножителя сигналов, первый и второй выходы которого подсоединены соответственно к суммирующему входу и вычитающему входу первого усредняющего блока, дополнительный выход формирователя сигналов фазовых зон подсоединен к установочному входу управляемого делителя частоты, выход которого подсоединен непосредственно к обьединенным тактовым входам формирователя управляющих сигналов и второго порогового блока и через блок задержки подсоединен к установочному входу второго усредняющего блока, тактовый вход которого подключен к выходу задающего генератора, второй вход дополнительного элемента ИЛИ подключен к S-входу Rs-триггера, причем Rвход и S-вход RS-триггера, входы начальной установки первого усредняющего блока, блока коррекции и формирователя управляющего сигнала, тактовые входы первого усредняющего блока, первого порогового блока и формирователя управляющего сигнала и выход второго порогового блока являютс я соот ветст ве н но пе р вы м и вторы м уп ра вляющими входами, входами начальной установки, тактовым входом и дополнительным выходом устройства.

2. Устройство по и. 1, отличающееся тем, что формирователь управляющего сигнала содержит последовательно соединенные счетчик импуЛьсов, дешифратор и RS-триггер, R-вход которого подключен к входу сигнала разрешения записи счетчика импульсов, причем вычитащий вход и входы начальной установки счетчика импульсов и R-вход и пря10 мой выход RS-триггера являются соответственно тактовым входом, входами начальной установки и выходом формирователя управляющего сигнала.

3. Устройство по п. 1, отличающееся тем, что блок коррекции содержит последовательно соединенные реверсивный счетчик, дешифратор, и элемент ИЛИ вЂ” НЕ, причем вторые входы элемента ИЛИ вЂ” HE и дешифратора, суммирующий вход, вь1читающий вход, вход

20 сигнала разрешения записи, входы начальной установки реверсивного счетчика и выход элемента ИЛИ вЂ” HE являются соответственно первым, вторым и третьим управляющими входами, суммирующим входом, вычитающим входом и входами начальной установки и выходом блока коррекции.! 60! 770 о- Ол пармиоойл ля 3

/Г бпрмыддалел п 7

Фиг,5

&му дла гу Р

1 20

Йл пер/ого усреоЬгющего

Клима

Ол ерйго пороеоЕаео блока Ю

Фиг.4

От p о0мирооателя

Ълрормираба пеля 7

От формира5атела 4

ФуГ 5

0щ 5ополнительного

ЛЛЕ ЕЮ77а ФЛИ 70

D ъ

С

1601770

Составитель В. Орлов

Редактор H. Бобкова Техред А. Кравчук Корректор О. Ципле

Заказ 3279 Тираж 529 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям прп ГК11Т ((.СР

) I 3035 Москва., Ж вЂ” 35, Раугпская наб., д. 4/5

Производственно-издательский комбинат «Патент«. г. Ужгоро.i, ул. Гигарп и, 1 0 I