Устройство для измерения отношения размаха сигнала к эффективному значению флюктуационной помехи

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике. Цель изобретения - повышение быстродействия путем уменьшения длительности такта измерения. Устройство содержит блок измерения 1 помехи, коммутатор 2, блок фиксации 3, стробируемый компаратор 4, ЦАП 5, источник 6 опорного напряжения, регистр 7 последовательных приближений, блок индикации 8, генератор 9 строба, блоки деления 10 и 11 частоты, реверсивный счетчик 12, блоки сравнения 13-15, блок формирования 16 последовательного кода поразрядного уравновешивания. В процессе работы устройства в каждом такте анализируется число превышений видеоимпульсом напряжения уравновешивания. Если к концу такта уравновешивания число этих превышений не достигает /превышает/ 1/2 числа кадров, составляющих такт уравновешивания, то напряжение уравновешивания с выхода ЦАП 5 убывает /возрастает/ по законам дихотомии. В процессе уравновешивания имеется возможность принимать решения об увеличении или уменьшении напряжения уравновешивания, а следовательно, формировать цифровой код результата измерения, не дожидаясь набора полного объема статистики. 3 з.п. ф-лы, 6 ил.

СОЮЗ СО8ЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51)5 Н 04 N 17 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 4456762/24-09 (22) 08.07.88 (46) 23.10.90. Бюл. № 39

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (71) Опытно-конструкторское бюро специальных радиотехнических систем Новгородского политехнического института (72) В. П. Орловский, О. О. Попов и В. А. Филиппов (53) 621.397 (088.8) (56) Авторское свидетельство СССР № 1113900, кл. Н 04 N 17/00, 1982.

„„SU„„1601781 А 1

2 (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ

ОТНОШЕНИЯ РАЗМАХА СИГНАЛА К

ЭФФЕКТИВНОМУ ЗНАЧЕНИЮ ФЛЮКТУАЦИОННОЙ ПОМЕХИ (57) Изобретение относится к измерительной технике. Цель изобретения — повышение быстродействия путем уменьшения длительности такта измерения. Устройство содержит блок измерения 1 помехи, коммутатор 2, блок фиксации 3, стробируемый компаратор 4, ЦАП 5, источник 6 опорного

1601781

3 ! напряжения, регистр 7 последовательных приближений, блок индикации 8, генератор

9 строба, блоки деления 10 и 11 частоты, реверсивный счетчик 12, блоки сравнения

13 — 15, блок формирования 16 последовательного кода поразрядного уравновешивания. В процессе работы устройства в каждом такте анализируется число превышений видеоимпульсом напряжения уравновешивания. Если к концу такта уравновешивания число этих превышений не достиИзобретение относится к измерительной технике и может быть использовано в телевизионных системах для измерения отношения размаха видеосигнала к эффективному значению флюктуационной помехи.

Целью изобретения является повышение быстродействия путем уменьшения длительности такта измерения.

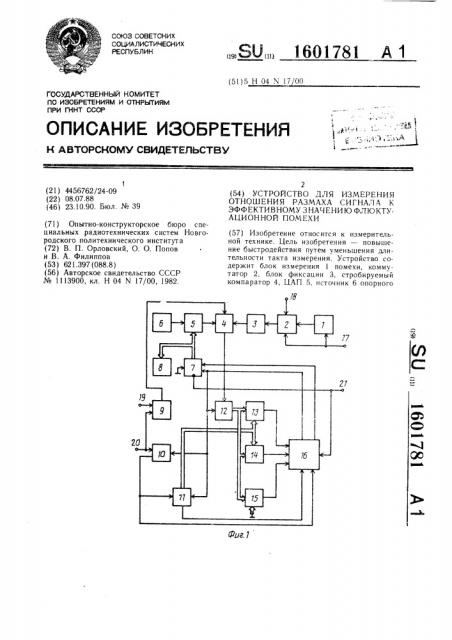

На фиг. 1 представлена блок-схема устройства для измерения отношения размаха сигнала к эффективному значению флюктуационной помехи; на фиг. 2 — структурная схема блока деления частоты; на фиг. 3 — структурная схема блока сравнения; на фиг. 4 — структурная схема блока формирования последовательного кода поразрядного уравновешивания; на фиг. 5 и

6 — временные диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 измерения помехи, коммутатор 2, блок 3 фиксации, стробируемый компаратор 4, цифроаналоговый преобразователь (ЦАП) 5, источник 6 опорного напряжения, регистр 7 последовательных приближений, блок 8 индикации, генератор 9 строба, первый 10 и второй

11 блоки деления частоты, реверсивный счетчик 12, первый 13, второй 14 и третий 15 блоки сравнения, блок 16 формирования последовательного кода поразрядного уравновешивания (ФПКПУ), вход 17 видеосигнала, вход 18 сигнала управления режимом, вход 19 строчных синхроимпульсов, вход 20 кадровых синхроимпульсов, вход 21 запуска устройства.

Блок 10(11) деления частоты содержит блок 22 постоянной памяти, реверсивный счетчик 23, одновибратор 24 и элемент HE

25.

Блок 13 (14 и 15) сравнения содержит блок 26 постоянной памяти и цифровой компаратор 27.

Блок 16 ФПКПУ содержит элемент И-HE

28, первый 29 и второй 30 элементы И, коммутатор 31, элемент 32 задержки и элемент ИЛИ 33.

4О

55 гает (превьппает) 1/2 1исла кадров, составляющих такт уравновешивания, то напряжение уравновешивания с выхода ЦАП 5 убывает (возрастает) по законам дихотомии, В процессе уравновешивания имеется возможность принимать решения об увеличении или уменьшении напряжения уравно. вешивания, а следовательно, формировать цифровой код результата измерения, не дожидаясь набора полного объема статистики, 3 з.п. ф-лы, 6 ил.

Устройство для измерения отношения размаха сигнала к эффективному значению флюктуационной помехи работает следующим образом.

Устройство обеспечивает два режима измерения: измерение отношения сигнал/шум и измерение размаха видеоимпульсов от точечных объектов.

В первом режиме измерения на вход

18 устройства подается сигнал логической

«1». При этом на вход блока 3 фиксации видеосигнал поступает через коммутатор 2 с выхода блока 1 измерения помехи, коэффициент усиления которого регулируется таким образом, чтобы поддерживать постоянным эффективное значение флюктуационного шума в видеосигнале на его выходе, при этом размах видеосигнала на выходе блока 1 пропорционален отношению сигнал/шум. При подаче на вход 18 устройства уровня логического «О» видеосигнал на вход блока 3 фиксации поступает через коммутатор 2 непосредственно с входа 17 устройства, при этом выполняется измерение не относительных, а абсолютных значений размаха видеосигнала.

Измерение представляет собой процесс уравновешивания размаха видеоимпульса от точечного объекта, находящегося внутри строба, наведенного оператором, постоянным напряжением, формируемым ЦАП 5 в соответствии с кодами, вырабатываемыми-регистром 7 последовательных приближений. Последний работает таким образом, что в каждом такте преобразования он вырабатывает цифровой код, начиная с кода 011...1 (половина максимального), который преобразуется далее в постоянное напряжение и сравнивается затем с преобразуемым аналоговым сигналом. Если сигнал, соответствующий коду 011...1 меньше преобразуе ° мого аналогового сигнала, то на информационный вход регистра с устройством сравнения (например, компаратора) поступает сигнал логической «1» и в начале следующе!

60!7Ь! го такта (по приходу тактового импульса на вход С регистра) в старший разряд регистра записывается значение «О».

В случае обратного соотношения преобразуемого и опорного (соответствующего коду 011...1) напряжений в начале следующего такта на выходе регистра присутствует двоичный код 001...1. Таким образом по сравнению с первым тактом преобразования двоичный код на выходе регистра 7 увеличивается или уменьшается на

1/4, т. е. происходит изменение ло законам дихотомии. Полное преобразование в параллельный двоичный код происходит за

2" — 1 тактов, где к — число разрядов.

В процессе работы предлагаемого усгройства в каждом такте анализируется число превышений видеоимпульсом напряжения уравновешивания. Если к концу такта уравновешивания число этих превышений не достигает 1/2 числа кадров, составляющих такт уравновешивания, регистр 7 последовательных приближений вырабатывает такой код, подаваемый на ЦАП 5, что напряжение уравновешивания убывает по законам дихотомии. Если число превышений видеоимпульсом напряжения уравновешивания ста новится большим

1/2 числа кадров, составляющих такт уравновешивания, напряжение с выхода

ЦАП 5 соответственно возрастает.

Число тактов уравновешивания в цикле измерения равно разрядности выходного двоичного кода. Каждый такт полного уравновешивания (ПТУ), длительность которого определяется выбранным объемом статистики и составляет N кадров, разбит на

m элементарных тактов уравновешивания (ЭТУ) длительностью п кадров (m= —,, ) .

Если М вЂ” число разрядов выходного двоичного кода результата измерения, которое равно числу тактов уравновешивания, то М N — число кадров, составляющих полный цикл измерения.

В процессе уравновешивания имеется возможность принимать решения об увеличении или уменьшении напряжения уравновешивания (а следовательно, формировать цифровой код результата измерений) „не дожидаясь набора полного объема статистики.

Действительно, поскольку результирующая точность измерений при данной разрядности выходного кода и отношения сигнал/ шум определяется объемом выборки, производимой на последних шагах процесса уравновешивания, то объем выборки на предыдущих шагах не оказывает влияния на результирующую точность, а носит оценочный характер и может быть сокращен без снижения результирующей точности измерений.

Пусть длительность элементарного такта уравновешивания составляет п=16. Если

К (+ } оказывае-:ся равным или меньшим 4, -го нулевая гипотеза отвергается и делается шаг на "мен "|.iåíèе

Если же К (+) оказывается равным или большим 12, выполняется шаг на увеличение 1}ца. В случае, если 5(K,„(+) 11, объсм выборки увеличивается до 32, а пороги становятся 1 ==11, 4=21, лри этом повторяется предыдущая процедура поиска и так до достижения максимальной длительности такта уравновешивания, равного

М, по окончании которого принятые решения осуществляются, как и в известном, на основе анализа числа превышений вндеоимпульсом напряжения уравновешивания.

Блок 10 деления частоты (фиг. 2) формирует сигналы синхронизации ЭТУ. Число и кадров, составляющих ЭТУ, задается блоком

22. По сигналу «Пуск» (фиг. ба), поступающему на вход обнуления (вычитающего) счетчика 23, на выходе его устанавливается нулевой код, при этом на выходе одновибратора 24, подключенном к выходу переполнения счетчика 23, появляется сигнал, по длительности равный

КСИ (фиг. бб). По заднему фронту этого импульса срабатывает однов«братор 24 (фиг. бв), выходным сигналом которого в счетчик 23 с выхода блока 22 записывается число и. Очередные КСИ, подаваемые на вычитающий вход счетчика 23, уменьшают его состояние. При достижении

«О» на выходе переполнения (фиг. 6 г) и соответственно на выходе блока деления {фиг. бд) формируется импульс по длительности, равный КСИ.

Аналогично работает блок !! деления частоты, который формирует сигналы синхронизации ПТУ. Отличие заключается лишь в том, что в блок 22 записывается число и, а выходной код счетчика, соответствующий текущему номеру ЭТУ в ПТУ, используется в качестве адреса для блоков 13 и 14 сравнения.

Блоки 13---15 сравнения гроизводят сравнение выходного : ода с порогами и, записанными пс соответств,ющ.м адресам блока 26. При этом блок 3 вырабатывает логическую «!» в случае если

К,(+) =: );, 01ок 14 вырабатывает логическую «1» в случае, если К„{+})d, а блок

15 — если, К { - - } ) d ь причеi: значения

di и д соответсгвует табличным данным, а 1; == - - г

Блок 16 формирования, анализируя состояние выходов блоков 13 †-15 сравнения по импульсам синхронизации ЭТУ и ПТУ, вырабатывает последовательный код данных для записи в регистр 7 и импульс записи.

Сигнал «Пуск», приходящий по входу

2! запуска (фиг. 5а), Hpoxoëèò через элемент ИЛИ 33 и осуществляет сброс блоков 10 и 11 деления и счетчик", 12.

1601781 или

Кроме того, сигнал «Пуск» задает начало цикла работы регистра 7 последовательных приближений, на выходе которого устанавливается двоичный код, преобразуемый

ЦАП 5 в напряжение, равное половине эталонного.

В течение п кадров первого такта размах видеоимпульса от точечного объекта, подаваемый с выхода блока 3 фиксации на первый вход компаратора 4, сравнивается с постоянным направлением с выхода ЦАП 5. Импульсы с выхода компаратора 4, соответствующие превышению напряжения U, логически умножаются с сигналом строба, сформированного генератором 9 строба, и поступают на счетный вход счетчика 12, увеличивая состояние (фиг. 5б).

Пусть в первом такте уравновешивания имеет место условие U,

)dg. При этом логическая «1» с выхода блока 14 сравнения проходит через .коммутатор 31, формируя информационный бит для регистра 7. Логический «О» с выхода блока 13 сравнения (К» (+))д,) вызывает появление логической «1» на выходе элемента И-НЕ 28, которая открывает элемент И 29 для прохождения импульса синхронизации ЭТУ через коммутатор 31 и элемент ИЛИ 33 на вход записи регистра 7 (фиг. 5г). Этот же импульс обнуляет блоки 10 и 11 деления и счетчик 12, таким образом, в старший разряд выходного двоичного кода блока 7 формирования алгоритма уравновешивания записывается логическая «1» и напряжение уравновешивания повышается (фиг. 5д) и осуществляется переход к второму такту уравновешивания.

Пусть во втором такте уравновешивания имеет место U+ )U„. Тогда на выходе блока 13 сравнения присутствует «1», а на выходе блока 14 сравнения устанавливается «О», который проходя через коммутатор 31, определяет информационный бит очередного разряда регистра 7, а проходя через элемент И-НЕ 28, устанавливает его на выходе «!», разрешающую как и в рассмотренном случае, запись этого бита в регистр 7 и сброс блоков 10 — 12.

Пусть в третьем такте уравновешивания число видеоимпульсов, превысивших

U Ä, соответствует условию !1(Ки (+) Cd2 °

Г1ри этом к моменту окончания первого элементарного такта (фиг. 5б) в третьем такте уравновешивания на выходе обоих блоков 10 и 11 сравнения присутствуют «1», а на выходе элемента И-НЕ

28 устанавливается «О», запрещающии формирование импульса записи.

Если к приходу очередного ЭТУ (до окончания ПТУ) выполняется одно из условий

К»; (+))с1„;

K„,. (-1-) „в каждом ЭТУ в пределах ПТУ считываются по i-му адресу, формируемому блоком 11 деления из блока 26.

В случае, если к приходу синхроимпульса ПТУ такт уравновешивания не завершился, определение информационного бита для формирования кода поразрядного уравновешивания производится путем анализа логического состояния блока 5 сравнения, выход которого через коммутатор

31 и элемент 32 задержки подключается к информационному входу регистра 7 при единичном сигнале на адресном входе коммутатора 31. Такой сигнал формируется при условии совпадения синхроимпульсов ЭТУ и ПТУ и отсутствии импульса запуска устройства (фиг. 5е). Запись информационного бита производится синхроимпульсом ПТУ, пропускаемого через второй вход коммутатора 31.

В блоке 26 блока 15 сравнения записано число вЂ, которое выбрано исходя

z из следующих соображений.

Такт измерений разбит на m элементарных (длительностью и кадров) тактов. В каждом кадре имеется один видеоимпульс от измеряемого точечного объекта, амплитуда которого флюктуирует. Полагают, что закон распределения этой случайной величины нормальный. Тогда, если пороговое напряжение, уравновешивающее видеоимпульс, в . точности равно среднему значению размаха видеоимпульса U — — U<, то при достаточно большом числе кадров измерения

m и количество в идеои м пульсов К (+ ), превышающих U, практически равно количеству видеоимпульсов Кц (-) не достигших

U или К„(+)

При условиях U )U< или U <(3„, соответственно

K„(+)< " K„(+))

М Й

Таким образом, если за N кадров, составляющих полный такт измерения, сравнивать число K< (+ ) превышений порога с величинои —, можно в конце такта измеИ рения принимать решение об увеличении или об уменьшении напряжения Uö . Это решение, как и в известном устройстве, принимается в зависимости от того, больше или меньше половины общего числа видеоимпульсов (числа кадров набора статистики) превысила пороговый уровень.

1601781

Формула изобретения

20

1. Устройство для измерения отношения размаха сигнала к эффективному значению флюктуационной помехи, содержащее последовательно соединенные блок измерения помехи, коммутатор, второй вход которого соединен с первым входом блока измерения помехи и является входом видеосигнала, а третий вход — входом сигнала управления режимом, блок фиксации и стробируемый компаратор, второй вход которого соединен с выходом источника опорного напряжения через цифроаналоговый преобразователь (LIAH), третий вход соединен с выходом генератора строба, а выход стробируемого компаратора соединен с сигнальным входом реверсивного счетчика, а также блок формирования последовательного кода поразрядного уравновешивания {ФПКПУ) и блок индикации, при этом первый и второй входы генератора строба являются входами соответственно строчных синхроимпульсов и кадровых синхроим пульсов, отличающееся тем, что, с целью повышения быстродействия путем уменьшения длительности такта измерения, введены регистр последовательных приближений, первый, второй, третий и четвертый входы которого соединены соответственно с общей шиной, с первым и вторым выходами блока ФПКПУ и входом запуска устройства, а выходы соединены с входами блока индикации и вторыми входами ЦАП, три блока сравнения, выходы которых соединены соответственно с первым, вторым и третьим входами блока

ФП КПУ, четвертый вход которого соединен с входом запуска устройства, а также два блока деления частоты, к первым входам которых подключены вторые входы реверсивного счетчика и блока ФП КПУ, к пятому и шсстому входам которого подключены соответственно выходы первого и второго блоков деления частоты, к второму входу которого подключен выход первого блока деления частоты, к второму входу которого подключен второй вход генератора строба, при этом вторые выходы второго блока деления частоты соединены с объединенными первыми входами первого и второго блоков сравнения, к вторым входам которых подключены первые входы третьего блока сравнения и выходы реверсивного счетчика, а вторые входы третьего блока сравнения соединены с общей шиной.

2. YcTpoHcTBQ Ilo ll. 1, 0Ti1llчающееся тем, что второй блок деления частоты содержит последовательно соединенные блок постоянной памяти, реверсивный счетчик, информационные выходы которого являются вторыми выходами второго блока деления частоты, элемент НЕ, выход которого является первым выходом второго блока деления частоты, и одновибратор, включенный между входом элемента НЕ и входом записи реверсивного счетчика, счетный вход которого является вторым входом второго блока деления частоты, первый вход которого соединен с входом установки реверсивного счетчика.

3. Устройство по и. 1, отличающееся тем, что каждый блок сравнения содержит последовательно соединенные блок постоянной памяти, входы которого являются первыми входами блока сравнения, и цифровой компаратор, вторые входы которого являются вторыми входами блока сравнения, выход которого соединен с выходом цифрового компаратора.

4. Устройство по п. 1, отличающееся тем, что блок формирования последовательного кода поразрядного уравновешивания (ФПКПУ) содержит последовательно соединенные элемент И-НЕ, первый вход которого является первым входом блока

ФПКПУ, и первый элемент И, второй элемент И, канальный коммутатор, первый и второй входы первого канала которого являются соответственно третьим и вторым входами блока ФПКПУ, четвертый, пятый и шестой входы которого являются соответственно первым, вторым и третьим входами второго элемента И, выход которого соединен с управляющим входом канального коммутатора, первый и второй входы второго канала которого подключены соответственно к выходу первого элемента И и третьему входу второго элемента И, а также элемент задержки подключенный к выходу первого канала канального коммутатора и являющийся первым выходом блока ФПКПУ, и элемент ИЛИ, первый и второй входы которого соединены соответственно с выходом второго канала коммутатора и с первым входом второго элемента И, а выход является вторым выходом блока ФПКПУ, при этом второй вход первого элемента И соединен с вторым входом второго элемента И.

C блЛ

ЕЙНАЯ

С дл1

1601781

11

Составитель И. Грацианская

Редактор Н. Бобкова Техред А. Кравчук Корректор О. Кравцова

Заказ 3279 Тираж 533 Подписное

ВНИИПИ Государственного комитета по изобрегениям и пткрьпиям при < КНТ СССР

113035, Москва, Ж вЂ” 35, Раушская наб., д 4 5

Производственно-издательский комбинат «11атент», г. Ужгород, ул Гагарина, l01