Устройство для приема многочастотных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи и предназначено для приема многочастотных сигналов, передаваемых кодом "2 из N", и их преобразования в сигналы управления коммутационным оборудованием АТС. Целью изобретения является повышение быстродействия. Устройство содержит усилитель 1, первый 3 и второй 9 блоки задержки, первый счетчик 5, сумматор 8, элемент 10 ИЛИ, дешифратор 14, блок 15 памяти. Цель достигается введением в устройство распределителя 11 импульсов, N ячеек 12 памяти, генератора 17, синтезатора 16 частот, мультиплексора 13, второго счетчика 7, частотного компаратора 2, одновибратора 4 и элемента 6 И. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)5 Н 04 0 !/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

1 (21) 4641145/24-09 (22) 23.01.89 (46) 23.10.90. Бюл. № 39 (72) А. С. Патлах, С. В. Егоров, А. И. Корнилов и Н. И. Голубничий (53) 621.395.632 (088.8) (56) Авторское свидетельство СССР № 1322540, кл. Н 04 g 1/46, 1986. (54) УСТРОЙСТВО ДЛЯ ПРИЕМА МНОГОЧАСТОТНЫХ СИГНАЛОВ (57) Изобретение относится к технике связи и предназначено для приема многочастотных сигналов, передаваемых кодом

ÄÄSUÄÄ 1601782 А 1

«2 из и», и их преобразования в сигналы управления коммутационным оборудованием АТС. Целью изобретения является повышение быстродействия. Устройство содержит усилитель 1, первый 3 и второй 9 блоки задержки, первый счетчик 5, сумматор 8, элемент ИЛИ 10, дешифратор 14, блок 15 памяти. Цель достигается введением в устройство распределителя 11 импульсов, и ячеек 12 памяти, генератора 17, синтезатора 16 частот, мультиплексора 13, второго счетчика 7, частотного компаратора 2, одновибратора 4 и элемента И 6. 1 ил.

1601782

Изобретение относится к технике связи

1 и предназначено для приема многочастот,ных сигналов, передаваемых токами тональ ных частот кодом «2 из и», и их преобразования в сигналы управления коммута;ционным оборудованием ATC.

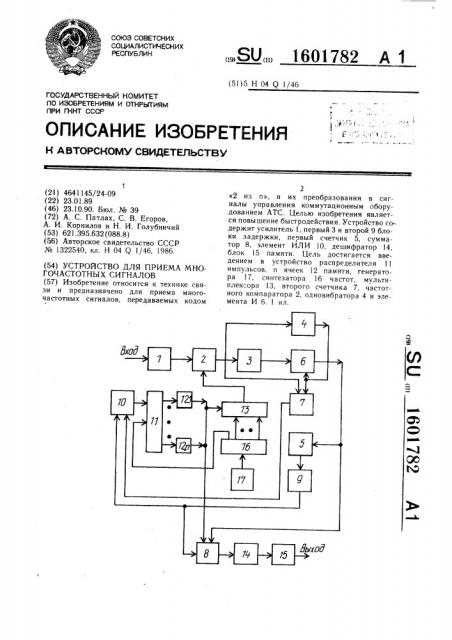

Целью изобретения является повышение . быстродействия, На чертеже приведена структурная электрическая схема устройства для прие;ма многочастотных сигналов.

Устройство содержит усилитель 1, частот;ный компаратор 2, первый блок 3 задерж- ки, одновибратор 4, первый счетчик 5, : элемент И 6, второй счетчик 7, сумма тор 8, второй блок 9 задержки, эле, мент ИЛИ 10, распределитель 11 импуль: сов, п ячеек 12.1...12м памяти, мульти1 плексор 13, дешифратор 14, блок 15 па, мяти, синтезатор 16 частот, генератор I7

Устройство для приема многочастотных, сигналов работает следующим образом.

1

Для получения кода входной частоты

: входные частоты поочередно сравниваются в частотном компараторе 2 с рядом эталонных частот. При совпадении входной частоты с одной из эталонных частот в сумматор 8 записывается код, соответствующий данной эталонной частоте, а значит соответствующий и входной частоте.

: Таким образом, в сумматор 8 поступает код, соответствующий второй частоте, оп, ределяющей, совместно с первой частотой, передаваемую цифру. В сумматоре 8 происходит суммирование кодов, и суммарный код поступает в дешифратор 14, где преобразуется в цифру, которая хранится в блоке 15 памяти до получения .полного передаваемого номера. Входные сигналы принимаются усилителем 1, где усиливаются и нормируются по амплитуде. С выхода генератора 17 сигнал поступает на вход синтезатора 16 частот, на выходах которого образуется ряд частот, равных по значению входным частотам, поступающим на вход устройства. Этот ряд частот с и дополнительных выходов синтезатора 16 частот поступает на п входов мультиплексора 13.

Кроме этого, с выхода синтезатора 16 частот на информационный вход распреде-. лителя 11 импульсов поступает сигнал длительностью, равной 1, 5 периода нижней входной частоты из ряда частот, принимаемых устройством. Под действием этих сигналов на выходах расределителя 11 импульсов поочередно появляются сигналы на время, равное 1,5 периода нижней частоты, принимаемой устройством. Сигналы на выходах распределителя 11 импульсов появляются в возрастающем порядке, т. е. при поступлении первого импульса на информационный вход распределителя 11 импульсов, сигнал появляется на первом выходе, при поступлении второго импульса

55 на втором входе и -,. д. Сигналы с выходов распределителя 11 имп,льсов поочередно поступают на входы разрешения считывания ячеек 12.1...12.п памяти, благодаря чему на выходах этих ячеек поочередно появляются кодовые сигналы, соответствующие дискретному ряду частот, принимаемых устройством. При отсутствии сигнала разрешения считывания на входах ячеек 12.1...12.п памяти выходы этих ячеек находятся в третьем (высокоомном) состоянии. При поступлении сигнала на установочный вход распределителя 11 импульсов последний устанавливается в исходное положение, т. е. при поступлении очередного входного импульса сигнал появляется ня первом выходе распределителя 11 импульсов. Кодовые сигналы,на выходах ячеек 12.1...12.п памяти дискретно появляются в возрастающем порядке, т. е. от значения кодового сигнала, соответствующего нижней частоте, к значению кодового сигнала, соответствующего верхней частоте, принимаемой устройством. Кодовые сигналы с ячеек 12.1...12 и памяти дискретно поступают на управляющий вход мультиплексора 13. Под действием этих сигналов выход мультиплексора 13 поочередно подключается к каждому из входов. Таким образом, на первый вход частотного компаратора 2 с выхода мультиплексора поочередно (в возрастающем порядке) подаются частоты, равные по значению входным частотам, поступающим на вход устройства.

При совпадении частот, поступающих соответственно на первый и второй входы частотного компаратора 2, на его выходе появляется сигнал, который присутствует в течение — 1,5 периода нижней частоты, принимаемой устройством. Этот сигнал поступает через блок 3 задержки на вход элемента И 6, на информационный вход счетчика 7, а также запускает одновибратор 4.

Время задержки блока 3 задержки равно времени срабатывания одновибратора 4.

Последний формирует инверсный (по отношению к выходному сигналу частотного компаратора 2) импульс, длительность которого равна 0,5 периода нижней частоты, одновибратор 4 блокирует прохождение сигнала через элемент И 6. Одновибратор 4 и счетчик 7 служат для защиты устройства от действия импульсных помех.

Предполагают, что импульсная помеха приводит к появлению угнала на выходе частотного компаратора 2, после чего происходит запуск одновибратора 4. Импульс с выхода одновибратора 4 поступает на вход элемента И 6 и на время, равное 0 5 периода нижней частоты, принимаемой устройством, блокирует прохождение сигнала через элемент И 6. После окончания действия импульса с выхода одновибратора

4 на выходе частотного компаратора 2 сигнала, вызванного одиночным импульсом, с0! l 82

10

Фор»<ул< изобретения

Соста вител ь Г. Корса ко в

Редактор Н. Бобкова Техред А. Кравчук Корректор !1. Коро.!ь

Заказ 3279 Тираж 524 Подписи<к

ЬН11!1Г1!1 Государственного ком носта но изобретения I и о! Врьи I!H .Ври ГК11 ССС! !

13035, Москва, Ж вЂ” 35, Рау.нская ннб, l Ii н, л« ств iHH!!-Издате.! ьскн!1 ho. !áèi!.- т «!1

Если на вход устройства поступает рабочая частота, то после окончания действия импульса с выхода одновибратора 4 на выходе частотного компаратора 2 еще присутствует сигнал, который через блок 3 задержки и элемент И 6 поступает на вход разрешения записи сумматора 8. В последнем из соответствующей ячейки 12 памяти записывается кодовый сигнал, соответствующий входной частоте. Передним (переход от «О» к «!») фронтом импульса с выхода одновибратора 4 производится установка счетчика 7 в исходное положение для того, чтобы он не сработал при приеме второй рабочей частоты, так как при приеме первой рабочей частоты на информационный вход счетчика 7 уже поступил один импульс с выхода частотного компаратора 2.

После фиксирования второй частоты, аналогично описанному кодовый сигнал, соответствующий второй входной частоте, поступает в сумматор 8 из соответствующей ячейки 12 памяти и складывается с кодовым сигналом, соответствующим первой входной частоте.

Счетчик 5 считает число разрешающих суммирование импульсов с вь!хода элемента И 6 и по приходу второго импульса с выхода элемента И 6 выдает сигнал, который через блок 9 задержки поступает на вход разрешения считывания сумматора 8, разрешая считывaíèå суммарного кодового сигнала в дешифратор 14. На выходе дешифратора 14 появляется сигнал, определяющий цифру передаваемого номера, соответствующего паре

ЭЗ

45 принят; частст. Полученная цифра номера поступает в блок 1:5 памяти и хранится а М ДО;!O„7i-ЧЕ!;.:с ПО,:!ГОГО ПЕРЕДЯВЯЕМО-!

О комеря, В это - е время сигнал выхода счетч! ОЯ 5 через бло;; ь задержэлемек7 ".!.!! И 1О 17ocT !, РВеТ Н3 тановочкый вход распределителя ! импульсов, благодаря чему последний, а .значит, и мультиплексор !3 устанавливаются в начальное положение, и процесс повторяется до определения следующей цифры передаваемого номера.

Устройство д.-"я приема многочастотных сигналов, содержащее усилитель, вход которого является входом устройств . для приема мкогочастоткы.< сигналов, выходом которого является выход блока памяти, первый блок задержки и первый счетчик, вH.ход которого через второй блок задержки подклfoHeH l< пеpHohlу Bходч элем HTH ИЛИ к Входу рязрец:еь1:<я считывания сумматора, вы.=:од которого через дешифратор подключеH к входу блока памяти, Отличпюи ееея тем, что, с целью повышения бь:стродействия, введены распределитель импульсов, и ячеек памяти, генератор. сиктезатор частот, мульти плексор, второй счетчик и и Оследователько соединенные час-..откый компарятор, одковибратор и элемент И, выход которого подключен к информационном. входу первого счетчика к входу рязрец ения записи су мматоря, !! к форма циоккы и Вхо i которого подключен к выходам r; ячеек памяти к управляющему входу мультиплексора, выход которого подключек к первому входу частотного ком пярято1зя...-.торой вход которого подключен к выходу усилителя. а выход — чер ". первый блок задержки к второму входу элемента И, первый вход которого подкл:!;.-::-:.* к установочному входу второго счет-.ккя, ккформациоккый вход и выход !<оторо;.О подключены соответственно к входу Одкозкбратора и второму вхо. .", э. .с !ектЯ !, i И, вы«ход !<Оторого подключен K устяковоч-lo÷ó входу пяспределителя импульсов. и выходов которого подключены соответственно к входам и ячеек памяти, а информационный вход — к перво !у выходу синтезатора чяСтот. п дополнительных выходов которого подключены соответственно к п входам мультиплексора, а вход — к выходу генератора.