Демодулятор дискретных сигналов

Иллюстрации

Показать всеРеферат

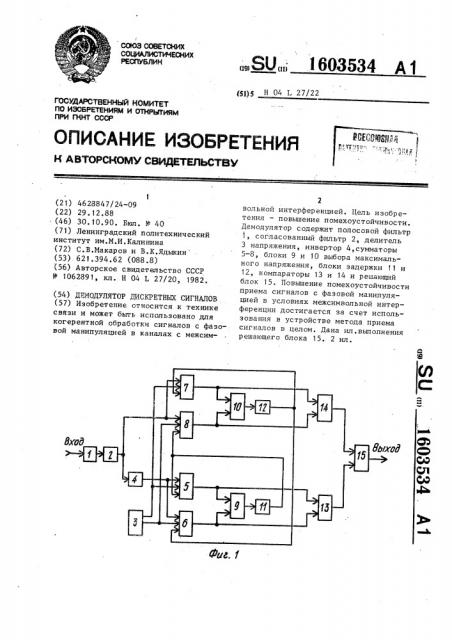

Изобретение относится к технике связи и может быть использовано для когерентной обработки сигналов с фазовой манипуляцией в каналах с межсимвольной интерференцией. Цель изобретения - повышение помехоустойчивости. Демодулятор содержит полосовой фильтр 1, согласованный фильтр 2, делитель 3 напряжения, инвертор 4, сумматоры 5-8, блоки 9 и 10 выбора максимального напряжения, блоки задержки 11 и 12, компараторы 13 и 14 и решающий блок 15. Повышение помехоустойчивости приема сигналов с фазовой манипуляцией в условиях межсимвольной интерференции достигается за счет использования в устройстве метода приема сигналов в целом. Дана ил.выполнения решающего блока 15. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК щ)5 Н 04 L 27/22

Фиг. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

IlPH ГКНТ СССР

1 (21) 4628847/24-09 (22) 29. 12.88 (46) 30.10.90. Бюп. N - 40 (71) Ленинградский политехнический институт им.M.È. Калинина (72) С.В.Макаров и В.К.Ядыкин (53) 621. 394. б 2 (088. 8) (56) Авторское свидетельство СССР

У 1062891, кл. Н 04 L 27/20, 1982. (54) ДЕМОДУЛЯТОР ДИСКРЕТНЫХ СИГНАЛОВ (57) Изобретение относится к технике связи и может быть использовано для когерентной обработки сигналов с фазовой манипуляцией в каналах с межсим„,ЯОы 1603534 Д1

2 вольной интерференцией. Цель изобретения — повышение помехоустойчивости, Демодулятор содержит полосовой фильтр

i согласованный фильтр 2, делитель

3 напряжения, инвертор 4, сумматоры

5-8, блоки 9 и 10 выбора максимального напряжения, блоки задержки 11 и

12„ компараторы 13 и 14 и решающий блок 15. Повышение помехоустойчивости приема сигналов с фазовой манипуляцией в условиях межсимвольной интерференции достигается за счет использования в устройстве метода приема сигналов в целом. Дана ил.выполнения решающего блока 15. 2 ил.

1603534

® Г "" " (q, 41 ц. =max(2 (2а; =1):;. -С:Ч

РР (o,.- )

-2(2с «.) С, (2а, 1 1 (ф где ct ° -- знач.=- .4ие информационного

1 символа на интервале времени ((Ч 1) .- 4 Ч." 4 4 Равное нулю при i--1 и равное единиц и ри i.= 2, ".(— значение свертки в моменты времени qT;;

С, и С вЂ” постоянные ко"-ффициенты.

i)i „= !,2, Изобретение относится к технике связи и может быть использовано для когерентной обработки сигналов с фа зовой манипуляцией в каналах с меж5 символе ной интерфер4 нцией, Цель изобретения — повышение IIO мехоустойчивости.

На фиг.1 изображена структурная электрическая схема предложенного демодулятора; на фиг.2 — схема решающего блока.

Демодулятор содержит полосовой 1, согласованный 2 фильтры, делитель 3 напряжения, инвертор 4, третий 5, четвертый 6, первый 7 и второй 8 сумматоры„ второй 9 и первый 10 блоки выбора максимального напряжения, второй 11 и первый 1.2 блоки задержки„ второй 13 и первый l4 компараторы„ решающий блок 15, состоящий из первого 16 и второ-о 17 сумматоров по модулю два, элемента HJIH 18, первого

19 и второго 20 регистров, первого

21 и второго 22 коммутаторов и блока

23 задержки.

Демодулятор работает следующим образом.

Непрерывный сигнал с двоичной фазовой манипуляцией поступает через полосовой фильтр 1 HB согласованный фильтр 2. Импульсный отклик этого фильтра согласован с формой одиночного сигнала длительностью 2Т. На выходе согласованного фильтра 2 форми35 руется последовательность импульсов с амплитудами, пропорщлональными выборочным значениям свертки входного сигнала и импульсног отклика этого фильтра.

Пля реализации: метода приема в цепом последовательност;л сигналов необходимо прежде ce:.-о произвести обработку выборочных значенил свертки в момент. .. зремени ЧТ .ч=1,2...) по алгоритму. максимизируюшему величину

Для реализации этого правила к выходу согласованного фильтра 2 подключены две пары сумматоров,первыйвторой и третий — четвертый. В моменты времени qT на первые входы сумматоров 5 и 6 поступает инвертирован( ное значение свертки Х . В тот же момент времени на первые входы второй пары сумма т ор ов с выхода с оглас ованного фильтра 2 поступает неинвертированное значение Х . Делитель 3 напряжения, выполненный, например, в виде цепочки последовательно включенных резисторов с отводами, предназначен для формирования двух величин постоянного напряжения, пропорциональных значениям: вЂ,2С, -С „ и

+ 2С4 -СО. На второй вход сумматора

5 с выхода делителя 3 напряжения посту. пает напряжение, пропорциональное величине -2С4 -Ср, а на второй вход второго сумматора 6 — пропорциональное величине +2C4 «Cg .

Формир ование з начений М< (1=1, 2) при i=1 происходит с помощью сумматоров 5 и 6, блока 9 выбора максимального напряжения и блока 11. Значение W < (1=1,2) при i=2 фор(4, !) мируется в тот же момент времени ЧТ с помощью блоков 7 и 8, 10,12. В фор® мировании значений M и W(, (М (а — ъ) участвуют величины W > Ы (» полученные в предыдущий момент времени на выходах блока 9 (W ) и блока

10 (Ч(" 1 ).

Рассмотрим формирование значений

W И- )

С выхода блока 11 на третий вход сумматора 5 в момент времени gT пос-. тупает значение W(" ) . На третий вход I сумматора 6 с выхода блока 12 в этот же момент времени поступает значение (4(,-4)

Ыд . Таким образом в момент времени qT на выходе сумлатора 5 формируется напряжение, пропорциональное вели,,И) . (%) И чине W =-2Х -2С(-Co+W а на выходе сумматора 6 -W(,1 =-2 1 + (М (1 (((-! l

2С,«С +14 . Значения напряжения с выходов пары сумматоров 5 и 6 поступают на входы блока 9, который и выбирает максимальное значение напряжеяля из двух поступивших на вход, Это значение напряжения через блок 11, задержанное на время Т» поступает на третьи входы сумматоров 5 и 8 в момент времени (q+1)T. Значение напряжения с

1603534 выходов сумматоров 5 и 6 поступают, кроме того, на входы компаратора 13, на выходе которого формируется напряжение, соответствующее либо "0", либо

"1". При этом "0" соответствует ситу5 ации, когда значение напряжения на выходе сумматора 5 больше значения напряжения на выходе сумматора 6.

Аналогично формируется значение

W® . На второй вход сумматора 8 с

2 выхода делителя 3 поступает напряжение, пропорциональное величине +2С »

-С, а на второй вход сумматора 7— напряжение пропорциональное величине

-2С» -С . Таким образом, на выходе сумматора 8 в момент времени qT формируется напряжение, пропорциональ— ное величине И((=2Х(»" +2С»-С +

Ъ-»)

+ М,,а на выходе сумматора 7 н этот же момент времени — напряжение, пропорциональное величине W =2Х

Ю (%»1

-2С,-С„+W . С выходов сумматоров

8 и 7 на входы блока 10 поступают 25 напряжения, пропорциональные значениям W(. Максимальное из двух поса.)

2 тупивших на вход блока 10 значений напряжения через блок 12 поступает на третьи входы сумматоров 6 и 7.

Значения напряжений с выходов этих сумматоров поступают на входы компаратора 14, на выходе которого формируется напряжение, соответствующее либо "0", либо "I", причем "0" соответствует ситуации, когда значение напряжения на выходе сумматора 8 больше значения напряжения на выходе сумматора 7. Логические напряжения с выходов ком 13 и 14 поступают соответственно на втсрой и первый входы решающего блока 15.

Две последовательности импульсов, которые получаются на выходе компараторов 13 и 14, определяют воз-:" 45 можные сочетания переданных инфор-, мационных символов, Так, "0" на выходе компаратора 13 на интервале времени (q-1)T; qT ., соотнетствует паре инфо„мационных символов 50 б ((- с) (ф)

d, d 1 (О; О), а "1" единица на выходе компаратора 13 — паре (q- ») (ф

d z d (1; О) . В свою очередь,"О" на выходе компаратора 14 на том же интервале времени соответствует паре информационных символов

И-»} (»И й, d z (0;1), а "1" на выходе (4- ) (4 компаратора 14 — паре d 2 d z (1;1) . Решающий блок 15 производит последовательный анализ этих пар информационных символов и определяет наиболее достоверную последовательность переданных символов в соответствии с алгоритмом приема в целом.

Рассмотрим два случая. В первом

7редполагается, что на интервале времени j(q-I)T> с(Т на ныходах обоих компараторов 13 и 14 напряжения по своей полярности совпадают, т.е, имеется либо "1", что соответствует (ч-1 ситуации когда символ d ", пред®е шествующий данному d „, однозначно определен и ранен единице, либо "0", что соответствует ситуации, (с(" когд Йе равен нулю. Для опредеЧ- » ления d необходимо учесть значения пары символов d(" } d "» I (Р;

1=1,2),полученных на предыдущем интервале времени ((с(-2)T; (q 1)Т)

Далее требуется на каждом интервале ((с,-1)Т; с1Т) определить из пар сим((-21 И- )

Волов d d такую В кОТОрОи

ПОСЛ ЕДННИ CHIIBOJI (3- ) с онпадает по значению с первйм символом следую(g-») (с() щей пары d e d „. Во втором предполагается, что напряжения на выходах компараторон 13 и 14 на интервале времени ((q-1)Т;qT) по своим значениям различаются, н в этих ус.— ловиях значение символа однозначно определить невозможно.

Решающий блок 15 работает следующим образом.

В первом случае на выходе сумматора по модулю два I? формируется "1", которая через элемент ИЛИ 18 поступает на последовательные входы регистров 19 и 20, но,на регистр» 20 с инверсией. Кроме того, эта "1" поступает на управляющие входы коммутаторов 21 и 22. На второй вход сумматора 16 поступает задержанное на время

Т с помощью блока 23 значение симво(q- ) ла dе, находящееся в регистре

19. Д7я первого случая возможны две; ситуации: — значение символа с(е совпадает со значением логического уровня, поступающего с выхода компаратора 13.

Тогда на выходе сумматора 16 формиС оставит ель Н . Ла sap ева

Техред N.Äèäûê

Корректор А. бсауленко

Редактор Л.Пчолинская

Тираж 527

Подписное

Заказ 3393

ВНИИИ Государственного комитета по изобретениям и открытиям лри ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент", r.ужгород, ул . Гагарина,101

9 1603534, О иены с входами первого блока выбора, щего блока, выход первого блока вымаксимального напряжения и первого бора максимального напряжения через компаратора, выход которого соединен первый блок задержки соединен с трес первым. входом решающего блока выхо- тьими входами первого и четвертого

У ды третьего и четвертого сумматоров сумматоров, выход второго блока выбосоединены с входами второго блока вы- ра максимального напряжения через бора максимального напряжения и вхо- второй блок задержки соединен с тредами второго компаратора, выход ко- . тьими входами второго и третьего сумрого соединен с вторым входом решаю- 1О маторов. !