Устройство для формирования моделей

Иллюстрации

Показать всеРеферат

Устройство для формирования моделей относится к вычислительной технике и может быть использовано для автоматизации процессов проектирования функциональных узлов из отдельных функциональных преобразователей. Целью изобретения является создание возможности автоматизированного формирования набора функциональных преобразователей, применение которых позволяет решить более крупную задачу. Для этого устройство содержит два блока памяти, три блока стековой памяти, схему сравнения, генератор тактовых импульсов, пять элементов задержки, три элемента И, две группы элементов ИЛИ, дешифратор, счетчик, вычитатель, одновибратор, схему поразрядного сравнения, две группы элементов И, два элемента ИЛИ, с помощью которых реализуется рекуррентный алгоритм построения набора функциональных преобразователей по заданным входным и выходным параметрам функционального узла. 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„,, 1605249

)S))S G 06 F 15/20

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 4485962/24-24 (22) 22 ° 09.88 (46) 07.11,90. Бюл. )т 41 (72) В.Ю.Анисимов, И.Х.Галимзянов, А.Г,Шевчик, И.Ю.Еськин и Ю.Л.Кулайчук (53) 681.32 (088.8) (56) Авторское свидетельство СССР

М 780011, кл. G 06 F 15/38, 1980.

Авторское свидетельство СССР

N 1267436, кл. G 06 F 15/38, 1985. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

МОДЕЛЕЙ (57) Устройство для формирования моделей относится к вычислительной технике и может быть использовано для автоматизации процессов проектирования функциональных узлов из отдельных функциональных преобразователей. ЦеИзобретение относится к вычислительной технике и может быть использовано для автоматизации процессов проектирования функциональных узлов из отдельных функциональных преобразователей, в частности при моделировании для формирования модели, состоящей из подмоделей и позволяющей преобразовать заданную совокупность входных данных в выходные.

Цель изобретения - расширение функциональных возможностей устройства за счет реализации набора функциональных преобразователей.

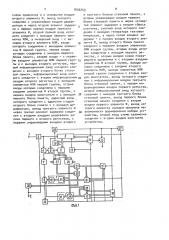

На фиг.. 1 приведена структурная схема устройства; на фиг. 2 - схема

2 лью изобретения является создание возможности автоматизированного формирования набора функциональных преобразователей, применение которых позволяет решить более крупную задачу. Для этого устройство содержит два блока памяти, три Ьлока стековой памяти, схему сравнения, генератор тактовых импульсов, пять элементов задержки, три элемента И, две группы элементов ИЛИ, дешифратор, счетчик, вычитатель, одновибратор, схему поразрядного сравнения, две группы элементов И, два элемента ИЛИ, с помощью которых реализуется рекуррентный алгоритм построения набора функцио- а нальных преоЬразователей по заданным входным и выходным параметрам функционального узла. 3 ил.

С: вычитателя: на фиг.3 - схема сравнения.

Устройство (фиг.1) содержит вход

1 пуска устройства, выход 2 признака окончания работы устройства, генератор 3 тактовых импульсов, элемент 4 задержки, счетчик 5, элемент И 6, элемент 7 задержки, дешифратор 8, элемент И 9, элементы ИЛИ 10 и 11, элементы 12 и 13 задержки, блоки 1416 стековой памяти, регистры 17 и 18, схему 19 сравнения, одновибратор 20, элемент 21 задержки, элемент И 22, блоки 23 и 24 памяти, группы элементов И 25 и 26, вычитатель 27, группы элементов ИЛИ 28 и 29, схему 30 сравнения.

1605249

3 ) (5

pcs или

Вычитатель 27 (фиг.2) содержит группу элементов И 31. Схема 30 поразрядного сравнения (фиг.3) содержит группу элементов ИЛИ 32, группу weментов И 33 и элемент И 34.

Пусть имеется множество U из подмоделей, каждая из которых описывается множеством входных параметров Т и выходных параметров Ов.

Цель устройства по заданным множествам входных параметров 1 и выходных параметров сформировать такой набор подмоделей, последовательная работа которых реализовала бы требуемое преобразование множества I e множество О .. Вводится дополнительное ограниченйе, связанное с требованием однозначности преобразования. В соответствии с этим требованием ни один из параметров не должен определяться в процессе преобразований более, чем в один раз. Пусть

S Й S, S — подмножество множества S (Sмножество уже отобранных подмоделей), SEU можно включить в S только тогда, когда

Z-, (1О =, где Z-, = 1 + U„Q>, (2)

Устройство реализует следующий рекуррентный алгоритм поиска требуемого набора функциональных преобразователей. На каждом этапе производятся следующие операции с моделямипретендентами: если ((Q nQ) g) /1 (Z;P Q =4) (3) верно, то подмодель S добавляется в множество Б ранее отобранных подмоделей, т.е. S S + (S).

При этом переопределяются текущие значения множеств

Z Z +Q иО Q+I -Q (4)

Условием останова является 1 О z.(5)

После добавления подмодели S e множество S происходит переход к следующему этапу работы алгоритмов, т.е, поиск модели S EU, удовлетворяющей условиям (2) и (3). Если такой модели

55 не существует, то происходит удаление из S выбранной на предыдущем шаге подмодели S. После этого производится поиск другой подмодели Б " 4. S, которая удовлетворяет условиям (2) и (3), При этом

Q - О + U» т — U„Q (6)

se «s

Для того, чтобы не производить при каждом возврате рекурсии вычисления по формулам (2) и (6), в устройстве применяются стеки, в которых сохраняются текущие значения множеств и Zg e

Устройство работает следующим образом.

Начальная установка устройства состоит в обнулении счетчика, записи в блок 23, состоящего из N регистров памяти, множеств I, а в блок 24множеств Ов (разрядность всех регистров соответствует максимальному числу параметров подмоделей. Если i-й параметр входит в множество, то в i-м разряде регистра устанавливается единица, иначе - нуль), в регистр 17 заносится множество I>, а в регистр

18 - множество О>

На вход 1 устройства подается импульс, который запускает генератор 3 тактовых импульсов (ГТИ), импульс с выхода которого добавляет единицу к содержимому счетчика 5 и через элемент 4 задержки и элемент И 6 подается на разрешающий вход дешифратора

8. Элемент И 6 закрыт только тогда, когда значение на счетчике 5 больше, чем N. Если текущее значение на счет" чике 5 равно i то íà i-м выходе дешифратора 8 при поступлении разрешающего сигнала появляется потенциал, который вызывает появление на выходах блоков 23.и 24 сигналов, соответствующих множествам I и ;. Группой элементов И 25 и элементом ИЛИ 10 происходит вычисление левой части условия (3), а группой элементов И 26 и элементом ИЛИ 11 - правой части условия (3). Если оба эти условия выполняются, то на входы элемента И 9 подаются: разрешающие сигналы. После этого импульс с выхода элемента И 6, задержанный элементом 7, проходит через элемент И 9 и, задерживаясь в элементе 12, подается на управляющие входы блоков 14-16 и входы разрешения записи регистров 17 и 18. При

5 16 этом в вершину блока 14 записывается номер подмодели i, в блок 15 и регистр 18 записывается новое множество вычисленное в соответствии с (4), а в блок 16 и регистр 17 записывается новое значение множества Z", вычисленное группой элементов ИЛИ 28 в соответствии с (4). После этого сигнал с выхода элемента 12, задержанный элементом 13, поступает на вход обнуления счетчика 5.

При поступлении очередного импульса с ГТИ 3 процесс повторяется. Если на один из входов элемента И 9 с выходов элементов ИЛИ 10 или 11 поступает запрещающий сигнал, то сигнал с ГТИ 3 через него не проходит, и до поступления следующего импульса с

ГТИ 3 изменений состояния устройства не происходит ° Если очередной импульс переводит счетчик 5 в состояние со значением, большим N, то на выходе схемы 19 сравнения появляется потенциал, закрывающий элемент И 6, запрещая тем самым срабатывание дешифратора 8, формирует на выходе одновибратора 20 импульс, который выбрасывает текущие значения из блоков 14-16 и подается на вход элемента И 22. Если при этом на .управляющем выходе блока

14 был потенциал, т.е. блок был пуст, то на выходе устройства появляется сигнал о том, что формирование набора преобразователей невозможно. После прохождения через элемент 21 импульс с выхода одновиЬратора 20 подается на входы разрешения загиси регистров

17 и 18 и счетчика 5. При этом содержимое вершины блока 14 переписывается в счетчик 5, содержимое блока 15 переписывается в регистр 18, а блока 16в регистр 17. Тем самым производится возврат устройства в состояние, соответствующее предыдущему шагу рекурсии,, Если на очередном этапе работы выполняется условие (5), то на выходе схемы 30, которая производит вычисление этого условия, появляется потенциал, который останавливает ГТИ 3 и подается на выход 2 устройства. Номера отоЬранных функциональных преобразователей сформированного набора хранятся в блоке 14.

Вычитатель ?7 (фиг.2) производит операцию вычитания множеств, причем уменьшаемое подается на второй вход, а вычитаемое - на первый вход. Вычисление производится поразрядно, причем

05249 единица на выходе появляется только в том случае, когда сигнал на втором входе равен единице, а на первом входе - нулю, Схема 30 поразрядного сравнения (фиг.3) производит операцию сравнения множеств А и В. Множество A подае ся на первый вход схемы, а  — на второй. Сигнал на выходе схемы 30 появляется только тогда, когда А ъ В, т,е. когда во всех разрядах сигнал на первом входе больше либо равен сигналу на соответствующем втором входе. Это условие не выполняется только тогда, когда на первый вход схемы подается нуль, а на соответствующий второй вход - единица.

20 ф о р м у л а изобретения

Устройство для формирования моделей, содержащее счетчик, выход которого соединен с первым входом схемы

25 сравнения, первый элемент ИЛИ, генератор тактовых импульсов, первый вход которого соединен с входом пуска устройства, второй вход - с выходом признака окончания работы устройства и

gg с выходом схемы поразрядного сравнения, первый вход которой соединен с первым входом константы устройства,, первый Ьлок памяти, два элемента И, два регистра, две группы элементов

И, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет реализации набора функциональных преобразователей, оно дополнительно содержит вто„®и рой элемент ИЛИ, второй блок памяти, три блока стековой памяти, третий элемент И, вычитатель, одновибратор, пять элементов задержки, две группы элементов ИЛИ и дешифратор, информа ционный вход которого соединен с выходом счетчика и с информационным входом первого блока стековой памяти, информационный выход которого соединен с информационным входом счетчика, ВХОД разрешения устанОвки кОтОрогО соединен с первыми входами разрешения записи первого и второго регистров и с выходом первого элемента задержки, вход которого соединен с первым входом первого элемента И, с пер" выми управляющими входами первсго, второго и третьего блоков стековой памяти и с выходом одновибратора, вход которого соединен с выходом

1605249 схемы сравнения и с инверсным входом второго элемента И, выход которого соединен.с управляющим входом дешифратора и через второй элемент задерж5 ки с первым прямым входом третьего элемента И, второй прямой вход которого соединен с выходам первого элемента ИЛИ, а инверсный вход — с выходом-второго элемента ИЛИ, входы которого соединены с выходами элементов И первой группы, первые входы которых соединены с выходом первого блока памяти, вторые входы - с первы! ми входами элементов ИЛИ первой груп- 5 пы и с выходом второго регистра, первый информационный вход которого соединен с, выходом второго блока стекавой памяти, информационный вход которого соединен с вторым информационным gp входом второго регистра и с выходами элементов ИЛИ первой группы, вторые входы которых соединены с первыми входами элементов И второй группы, с первь м входом вычитателя и с выходом 25 первого блока памяти, адресный вход . которого соединен с адресным входам второго блока памяти и с выходам дешифратора, выход третьего элемента И через третий элемент задержки саеди- gp нен с вторыми входами разрешения записи первого и второго регистров, с первыми управляющими входами второго и третьего блоков стекавой памяти, с вторым управляющим входам первого блока стекавой памяти и через четвертый элемент задержки с входам сброса счетчика, счетный вход которого соединен с выходом генератора тактовых импульсов, а через пятый элемент задержки - с прямым входом второго элемента И, выход второго блока памяти соединен с первыми входами элементов

ИЛИ второй группы, вторые входы которых соединены с выходом первого регистра, с вторым входом схемы поразрядного сравнения и с вторыми входами элементов И второй группы, выходы которых соединены с, входами второго элемента ИЛИ, выходы элементов ИЛИ второй группы соединены с вторым входам вычитателя, выход которого соединен с информационным входом третьего блока стековай памяти, с первым информационным входом первого регистра, второй информационный вход которого соединен с выходом третьего блока стекавай памяти, выход первого блока стекавай памяти соединен с вторым входам первого элемента И, выход котарога является выходом признака невозможности формирования набора устройства, второй вход схемы сравнения соединен с вторым входом константы устройства.

1605249

ФАЗ

Составитель Л.Логачева

Редактор Н.Тупица Техред Л.Сердюкова

Корректор С.4ерни

Заказ 3454 Тираж 5.70 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 1 1

II II

Г и на 101