Устройство для вычисления азимутальной корреляционной функции

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано при построении радиолокаторов с синтезированной апертурой антенны (РСА) и цифровой обработкой информации в реальном масштабе времени на борту носителя РСА. Цель изобретения - упрощение за счет уменьшения энергопотребления. Устройство содержит мультиплексоры 1-1...1-(M+1), элементы ИЛИ 2-1...2(M+1), блоки 3-1...3-(M+1) памяти, элементы 4-1...4-(M+1) задержки, блок 5 памяти, умножители 6-1...6-(M+1), сумматор 7. Из группы блоков 3 памяти сформирована двумерная матрица памяти, строки которой соответствуют линиям постоянной дальности, а столбцы - линиям постоянного азимута. Блок управления обеспечивает одновременные запись в один из столбцов и построчное считывание из других столбцов. Считанные данные перемножаются с отсчетами азимутальной опорной функции, хранящимися в блоке 5 памяти. Произведения суммируются многовходовым сумматором, формирующим оценку взаимной азимутальной корреляционной функции принятого и опорного азимутальных сигналов РСА. 1 з.п. ф-лы, 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ASTOPCHOf4Y СВИДЕТЕЛЬСТВУ

Rgb, / Я 1

ale@

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И 0THPblTHRM

ПРИ ГКНТ СССР (21) 4626875/24-24 (22} 27.12.88 (46) 07.11 90. Бюл. У 41 (71) Харьковский институт инженеров железнодорожного транспорта им. С.М.Кирова (72) П.Ф.Поляков, M.Г.Давиденко и А.П.Верещак (53) 681.3 (088.8)

I (56} Авторское свидетельство СССР

У 1282158, кл. G 06 F 15/336, 1985.

Элаши Э. и др. Радиолокационные станции с синтезированием апертуры для космической съемки планеты,области применения, методы, конструкторские разработки. — ТИИЭР, 1982, Р 10, с. 61, рис,18. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ АЗИМУТАЛЬНОЙ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ (57) Изобретение может быть использовано при построении радиолокаторов с синтезированной апертурой антенны (РСА) и цифровой обработкой информации в реальном масштабе вреin@

„„Я0„„ 1605257 А 1 (51}5 G 06 F 15/336

2 лени на борту носителя РСА. Цель изобретения — упрощение эа счет уменьшения энергопотребления. Устройство содержит мультиплексоры 1-1... ...1-(M+1), элементы ИЛИ 2-1...2-(М+

+1), блоки 3-1...3-(М+1) памяти, элементы 4-1...4-(M+1) задержки, блок

5 памяти, умножители 6-1...6-(M+1), сумматор 7. Иэ группы блоков 3 памяти сформирована двумерная матрица памяти, строки которой соответствуют линиям постоянной дальности, а столбцы — линиям постоянного азимута. Блок управления обеспечивает одновременные запись в один из столбцов и построчное считывание иэ других столбцов. Считанные данные перемножаются с отсчетами азимутальной опорной функции, хранящимися в блоке 5 памяти. Произведения суммируются многовходовым сумматором, формирующим оценку взаимной азимутальной корреляционной функции принятого и опорного азимутальных сигналов РСА. 1 з.п. ф-лы, 2 ил.

1605257

Изобретение относится к вычислительной технике и может быть использовано при построении радиолокаторов с синтезированной апертурой антенны (РСА) и цифровой обработкой информации в реальном масштабе времени при жестких ограничениях на энергопотребление.

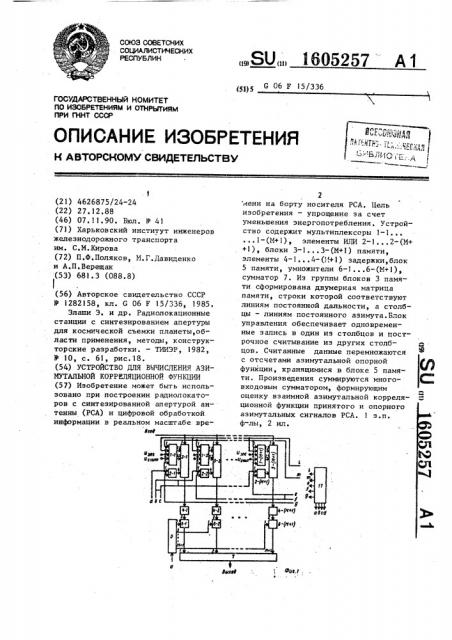

Цель изобретения — упрощение за счет уменьшения энергопотребления. .На фиг.1 представлена структурная схема устройства; на фиг. 2 — структурная схема блока управления.

Устройство содержит (фиг.1) группу мультиплексоров 1-1...1-(М+1), группу элементов ИЛИ 2-1...2-(М+1), группу блоков 3-1...3-(М+1) памяти, группу элементов 4-1...4-(M+1) задержки, блок 5 памяти; группу умножителей 6-1...6"(М+1), сумматор 7.

Генератор 8 тактовых импульсов, делители 9 и 10 частоты, счетчики

11 и 12, дешифратор 13, счетчики

14 и 15, дешифратор 16 составляют блок 17 управления.

Оценка взаимной корреляционной функции принимаемого и опорного сигналов PCA на 1-м этапе обработки вычисляется как

Я 2 м < 1 jajn- ) м (e1

Y X е Х h„(1)

N <

<е1 где Х / Х вЂ” m-й отсчет азимут + ( тального сигнала на

Й-м этапе обработки;

h — отсчет опорного сигЮ нала (комплексной экспоненты);

V Z а= 2è — — Т

9R

7 — скорость движения . носителя РСА;

Ъ - рабочая длина волны

РСА;

R — наклонная дальность;

То — период следования импульсов передатчика РСА;

M — число отсчетов азимутального сигнала, принимаемых за время

МТд синтезирования апертуры.

Отсчеты азимутального сигнала хранятся в группе блоков памяти— статических оперативных эапоминаю35

50 55 щих устройствах (Ст ОЗУ), организованных в виде матрицы памяти размерностью (М+1) столбцов N строк, где

N — число элементов разрешения PCA по дальности. При этом один блок

Ст ОЗУ образует один столбец матрицы па,-. мяти, а строка матрицы памяти образуется одноименными (т ° е., имеющими одинаковый адрес) ячейками всех блоков Ст ОЗУ, Число столбцов матрицы памяти на единицу больше, чем число отсчетов азимутального сигнала, принимаемых за время синтезирования апертуры. Поскольку в РСА, работающем в реальном масштабе времени, один, столбец матрицы памяти должен быть заполнен за время, равное периоду Т и следования импульсов передатчика, и за это же время во всех строках матрицы памяти должен быть выполнен

В-й этап обработки, т.е. вычисления по формуле (1), то наличие лишнего столбца обеспечивает выполнение. этих требований: в составе матрицы памяти постоянно имеется один свободный столбец, используемый для записи (заполнения), а данные, записанные в течение предыдущих М периодов следования импульсов передатчика PCA (т. е., этапов обработки), хранятся в остальных М столбцах матрицы памяти и используются для вычислений по формуле (1) на 1-м этапе обработки.

Таким образом, обновление данных в схеме (фиг.1) производится по столбцам матрицы памяти слева направо: на g.-м этапе обработки обновляется К-й столбец, на (2+1)-м этапе(К+1)-й столбец, Hà (8+2)-м этапе(К+2)-й столбец и т.д. Этот процесс циклический, так как после обновления (М+1)-ro столбца обновляется 1"й столбец и т.д. При этом самые старые отсчеты каждой строки матрицы памяти (Х ) в обозначениях формулы (1) ( находятся в столбце, прилегающем к заполняемому столбцу справа, а самые новые отсчеты (Х() в обозначениях

М формулы (1) — в столбце, прилегающем к заполняемому столбцу слева. Например, если заполняется К-й столбец, то "новизна". отсчетов нарастает с (К+1)-ro по (M+1)-й столбцы и далее с 1-ro по (К-1)-й столбцы.

Поэтому для обеспечения соответствия вычислений формуле (1) в устройство для вычисления азимутальной корреляционной функции введен блок 5

5257

5

160 памяти — постоянное запоминающее устройство (ПЗУ), состоящее из субблоков 17-1...17-(М+1), содержащих от-: счеты h+ опорного сигнала. На входы всех субблоков (входы адреса) подается число, равное номеру заполняемого на данном этапе обработки столбца матрицы памяти. Благодаря этому на выходы всех субблоков (т.е., на выходы ПЗУ) поступает содержимое их ячеек, номера которых равны номеру заполняемого столбца матрицы памяти, т.е. на выход ПЗУ поступает соответствующий столбец таблицы. Например, если заполняется первый столбец, в каждой строке отсчеты азиму е1, (Е) тального сигнала с Х по Х расположены соответственно в ячейках

2-го...(М+1)-ro столбцов Ст ОЗУ, а отсчеты опорного сигнала записаны в первом столбце таблицы соответст-. венно сверху вниз: О, Ь1, Ье,..., Ъ„„-(здесь нуль соответствует заполняемому столбцу, так как его содержимое. не вносит вклада в сумму в формуле (1)). Соедйнеиие Ст ОЗУ, ПЗУ, умножителей 6-2 ° ..6-(М+1) и многовходового сумматора 7 (фиг,l) обеспечивает вычисление искомой суммы произведений согласно (1).

Исходное состояние устройства перед началом Х-го этапа обработки следующее: отсчеты азимутального сигнала (для каждой строки матрицы своего, так как строки соответствуют различным элементам разрешения PCA по дальности) от Х,1 до Х записаны в блоки 3-2...3-(М+1) статическoro оперативного запоминающего устройства, все циклические двоичные счетчики находятся в состоянии "1".

Третьи входы всех мультиплексоров заземлены или подключены к полюсу источника питания в зависимости от того, какой уровень напряжения U nc задает режим записи для микросхем, на которых собраны блоки Ст ОЗУ. Четвертые входы всех мультиплексоров подключены к полюсу источника питания или заземлены в зависимости от того, какой уровень напряжения 11 цдт задает режим считывания для микросхем Ст ОЗУ.

Процесс записи. В начале С-го этапа обработки состояние "1" циклического двоичного счетчика 12 (с циклом длиной М+1) преобразуется дешифратором 13 в сигнал "Лог. 1" на его первом выходе. Этот сигнал через элемент ИЛИ 2-1 поступает на четвертый вход (" Выбор кристалла") блока 3-1, подготавливая этот блок к работе с

5 внешними устройствами. Кроме того, этот сигнал поступает на пятый (управляющий) вход мультиплексора 1-1, благодаря чему напряжение U>ö подается с третьего входа мультиплексо" ра 1-1 на третий вход блока 3-1 (входы выбора режима работы), и подготавливает блок 3-1 к записи. Одновременно первый вход мультиплексора 1-1 подключается к второму входу блока

3-1 (входу адреса), который посредством этого соединяется с выходом циклического двоичного счетчика 11 (с циклом длиной N) выполняющего функ20 цию формирователя адресов записи, На входе этого счетчика действует периодическая, с периодом Ту/N пос" ледовательность импульсов. Она формируется иэ периодической, с периодом

25 Тд/11 (М+1), последовательности импульсов, формируемой генератором 8 тактовых импульсов, посредством деления ее частоты на М+1 делителем 9 частоты. Таким образом, за период Тц следования импульсов передатчика PCA к первому (информационному) входу блока 3-1 поочередно подключаются

H ячеек этого блока, в которые записываются сигналы от Н элементов разрешения РСА по дальности, Так производится заполнение первого столбца матрицы памяти.

По истечении времени Тц с момента начала записи в блок 3-1 двоично-де"

4б сятичный счетчик 12 переходит в состояние "2" под действием импульса с выхода делителя 10 частоты,делящего на 11 частоту следования выходных импульсов делителя 9 частоты, и, та45 ким образом, формирующего последовательность импульсов с периодом Т>.

Начинается (1+1)-й этап обработки.

Состояние "2" двоично-десятичного счетчика 12 преобразуется двоично50 десятичным дешифратором 13 в сигнал

"Лог,l" на. его втором выходе и проис" ходит запись в блок 3-2 так, как описано выше.

Аналогичным образом производится запись во все блоки Ст ОЗУ,включая блок 3-(М+1)-. По окончании записи в него завершается цикл работы циклического двоичного счетчика 12, он

1605257 вновь переходит в состояние "1", и процесс заполнения матрицы памяти вновь начинается с левого ее края (начинается (1+И+1)-й этап обработки).

Процесс считывания. На ""ì этапе обработки на всех выходах двоичнодесятичного дешифратора !3, кроме первого, действуют сигналы "Лог.О".

Они поступают на пятые входы всех мультиплексоров, кроме мультиплексора 1-1. Благодаря этому к вторым входам всех блоков Ст ОЗУ, кроме бло" ка 3-1, подключены вторые входы соот- 15 ветствующих мультиплексоров, а на третьи входы этих блоков Ст ОЗУ пос" тупает напряжение с четвертых входов

cooTветствующих мультиплексоров, устанавливая блоки Ст ОЗУ .в режим считывания.

Вся считываемая часть матрицы памяти должна быть считана построчно за время Тц, т.е. на считывание одной строки отводится время Т !/11.Ïoñ" кольку одна строка матрицы памяти формируется имеющими одинаковый ад" рес (адрес считывания) ячейками блоков Ст ОЗУ, то это значит, что адреса должны меняться через Т„/Н.Функ" 30 цию формирования адресов выполняет циклический двоичный счетчик 14 (с циклом длиной Н), на первый вход которого поступает последовательность импульсов с периодом Т„/Н с выхода делителя 9 частоты.

В начале t-ro этапа обработки циклический двоичный счетчик 14. находится в состоянии "1", т.е. адрес считывания равен единице: считывает- g0 ,ся первая строка, Этот адрес с выхода циклического двоичного счетчика 14 через вторые входы всех мультиплексоров, кроме мультиплексора 1-1 (блок 3-1 находит- 45 ся в режиме записи), поступает на вторые входы всех блоков Ст ОЗУ,кроме блока 3-1. Так как считывание из блоков Ст ОЗУ уже разрешено, то необходимо лишь подать сигнал "Выбор кристалла" на четвертые входы блоков

Ст ОЗУ. Этот сигнал формируется двоично-десятичным дешифратором 16 путем дешифрации состояний циклического двоичного счетчика 15 (с циклом длиной N+I), на первый вход которого поступает с генератора 8 тактовых импульсов последовательность импульсов с периодом T„ /N (М+1).Таким образом, за интервал времени длительностью Т„/Н, в течение которого адрес считывания постоянен, считываются все ячейки первой строки. Их содержимое через элементы задержки поступает на вторые входы умножителей, на первые входы которых подается содержимое соответствующих ячеек постоянного запоминающего устройства 5. На первый вход умножителя,соответствующего заполняемому столбцу

{в данном случае блоку 3-1) поступает нуль, и он не вносит вклада в формирование суммы по формуле (1).

По истечении времени T /H с момента начала L-го этапа обработки циклический двоичный счетчик l5 возвра" щается в состояние "1", а циклический двоичный счетчик 14 переходит в состояние "2" и происходит считывание и вычисление азимутальной корреляционной функции во второй строке.

Аналогичным образом обрабатываются остальные строки.

По истечении времени Т с момента начала С-го этапа обработки все счетчики, кроме циклического двоичного счетчика 12, устанавливаются в состояние "1", а циклический двоичный счетчик 12 переходит в состояние "2".

Начинается (6+1)-й этап обработки, на котором заполняется блок 3-2 (второй столбец матрицы памяти) и происходит считывание из остальных бло« ков Ст ОЗУ так, как это описано выше.

По окончании (2+М)-го этапа обработки (заполнение блока 3-(М+1) и считывание у остальных блоков) все счетчики, включая циклический двоичный счетчик 12, устанавливаются в состояние "1" ввиду того, что длительности их циклов являются долями

Т . Кроме того, один pas за интервал времени (М+1) Тр по вторым входам (входам установки в "1") цикличес кие двоичные счетчики 11, 14 и 15 дополнительно устанавливаются в."1" передним фронтом сигнала с первого выхода двоично-десятичного дешифратора 13, что обеспечивает восстановление описанного выше порядка работы этих счетчиков при случайных сбоях в них.

Формула изобретения

). Устройство для вычисления азимутальной корреляционной функции, )605257 содержащее группу умножителей, группу элементов задержки, блок управления, сумматор, причем выходы элементов задержки группы соединены с первыми входами соответствующих умножителей группы, выходы которых соединены с соответствующими входами сумматора, выход которого является выходом устройства, отличающееся тем, что, с целью упрощения, оно содержит группу блоков памяти, группу мультиплексоров, группу элементов

ИЛИ, блок памяти, причем информационные входы блоков памяти группы объе- 15 динены и составляют информационный вход устройства, первый и второй выходы каждого мулЬтиплексора группы соединены соответственно с адресным входом и входом задания режима рабо- Zg ты соответствующего блока памяти группы, вход разрешения записи-считывания которого соединен с выходом соответствующего элемента ИЛИ группы, а выход соединен с входом соответствующего элемента задержки группы,первый и второй информационные входы мультиплексоров группы соединены соответственно с первым и вторым адрес-. ными выходами блока управления,тре-. ЗО тий и четвертый информационные входы каждого мультиплексора группы соединены соответственно с шиной единичного и нулевого потенциалов, управляющий вход мультиплексора группы соеди- З5 нен с первым входом соответствующего элемента ИЛИ группы и с соответствующим выходом первой группы выходов блока управления, второй вход элемента ИЛИ группы соединен с соответствующим выходом второй группы выходов блока .Управления, второй вход умножителя группы соединен с соответствующим выходом блока памяти, адресный вход которого соединен с третьим, адресным выходом блока управления.

2, Устройство по п.l, о т л ич а ю щ е е с я тем, что блок управления содержит генератор тактовых импульсов, два делителя частоты,четиРе счетчика и два дешифратора, причем выход генератора тактовых импульсов соединен с счетным входом первого счетчика и через первый делитель частоты — со счетными входами второго и третьего счетчиков и с входом второго делителя частоты, выход которого соединен с счетным входом четвертого счетчика, выход которого соединен с входом первого дешифратора, первый выход группы которого соединен с входами установки единичного начального состояния первого, второго и третьего счетчиков, выход первого счетчика соедийен с входом второго дешифратора, выходы второго, третьего и четвертого счетчиков являются соответственно первым, вторым и третьим адресными выходами блока, группа вй- -. ходов первого дешифратора является первой группой выходов блока, группа выходов второго дешифратора является второй группой выходов блока.

1605257

Составитель В,Орлов

Техред И.яндык

Редактор Н.Тупица

Корректор Т.Палий

Заказ 3455 Тираж 568 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101