Регистр сдвига

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки импульсных последовательностей. Целью изобретения является повышение достоверности передачи информации через регистр сдвига за счет коррекции временных интервалов между импульсами в случае их искажения из-за совпадения фронтов информационного и тактового импульсов. При этом интервалы между информационными импульсами кратны &Tgr;, где &Tgr; - целое число периодов тактовых импульсов T. Поставленная цель достигается за счет введения трех элементов ИЛИ 5, 6, 7, двух элементов И 8, 9, инвертора 10 и двух корректирующих триггеров 11, 12. 3 ил.

ССНОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„, 607015 (S1) 5 Г 11 С 19/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АBTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР (21) 4627191/24-24 (22) 29.12.88 (46) 15.11.90. Бюл, К 42 (72) E,Ê.Èîñèïîâ, Г.П.Курячьев, Н.А,Кавказский и Ш.Р,Загитов (53) 681.327.66 (088.8) (56) Алексенко А.Г., Шагурин И.И.

Микросхемотехника, Под ред. И ° П.Степаненко. M.: Радио и связь, 1982, с. 209, рис. 5,6,а.

Данилов P.Â,, Ельцова С.А., Иванов fO.Ï. и др. Применение интег— ральных микросхем в электронной вычислительной технике. — Справочник.

Под ред. Файзулаева Б.Н., Тарабрина Б,В. — М.: Радио и связь, 1987, с. 109, рис.5,45, а.

2 (54) РЕГИСТР СДВИГА (57) Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки импульсных последовательностей. Целью изобретения является повышение достоверности передачи информации через регистр сдвига за счет коррекции временных интервалов между импульсами в случае их искажения из-за совпадения фронтов информационного и тактового импульсов. При этом интервалы между информационными импульсами кратны,, где — целое число периодов тактовых импульсов Т. Поставленная цель достигается за счет введения

Я трех элементов ИЛИ 5-7, двух элементов И 8, 9, инвертора 10 и двух корректирующих триггеров 11, 12. 3 ил.

С:

1607015

Изобретение относится к вычислительной технике и может быть использовано в аппаратуре обработки импульсных последовательностей.

Целью изобретения является повышение достоверности передачи информации через регистр сдвига за счет коррекции временных интервалов между импульсами в случае их искажения из-за

1совпадения фронтов информационного и

1 тактового импульсов, при этом предполагается, что интервалы между инл формационными импульсами кратны (— целое число периодов тактовых

;.импульсов Т).

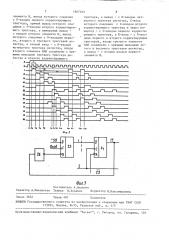

На фиг.1 приведена электрическая схема регистра сдвига; на фиг.2— временные диаграммы его работы; на фиг.3 — схема устройства записи ин- 20 формации в регистр сдвига, Регистр сдвига производит коррекцию импульсной последовательности, привязываясь к ее первому импульсу, Количество разрядов регистра опреде- 25 ляется максимальным интервалом между ,соседними импульсами импульсной последовательности.

На фиг.1 приведена схема регистра сдвига для случая, когда количество различных интервалов между импульсами ,входной последовательности равно двум — ЗТ и 6Т, т.е. для случая, когда О =ЗТ.

На фиг.1 показаны информационный вход 1,„тактовый вход 2, вход 3 начальной установки, и триггеров 4, 4 регистра, три элемента ИЛИ

5-7, элементы И 8, 9, инвертор 10, корректирующие триггеры 11, 12„ На фиг.1, 2 обозначены также выходы

13-20 триггеров,41-46 регистра, выход 21 элемента ИЛИ 5, выход 22 элемента ИЛИ 7, выходы 23, 24 триггероц

11, .12 соответственно. 45

Выходы первых трех (по числу минимального интервала между импульсами) триггеров 4 -4 .регистра соединены с входами элемента ИЛИ 5. Входы элемента ИЛИ 6 соединены соответственно 0 с выходами триггера 4 регистра и второго корректирующего триггера 12.

Входы элемента ИЛИ 7 соединены с выходами триггеров 4 и 4> регистра, Количество входов К элемента ИЛИ 7 определяется количеством различных интервалов между соседними импульсами во входной импульсной последовательности (в данном случае К=2).

Номера триггеров, выходы которых соединены с входами элемента ИЛИ 7, определяются по формуле

N, = 2+Д /Т, где gt — длительность возможного интервала между соседними импульсами, т.е. для нашего случая, когда интервалы между соседними импульсами обрабатываемой последовательности могут быть 1. (37) и 2 (6Т) номера тригге— ров будут. 5 и 8 (ь.=1,K; К=2).

Следовательно, с первым входом элемента ИЛИ 7 должен быть соединен выход триггера 4 регистра, с вторым входом — выход триггера 4

Регистр сдвига работает следующим образом (фиг.1, 2). .При появлении в момент времени на шине 3 начальной установки curttaëa уровня логической регистр сдвига готов к работе.

В момент времени t с устройства записи информации, выполненного, например, в соответствии со схемой, приведенной на фиг.3, на вход регистра по шине 1 поступает первый импульс обрабатываемой последовательности.

Рассмотрим .те ситуации, при которых регистр сдвига может внести в поступающие на. его вход импульсные последовательности искажения. Очевидно, это происходит тогда, когда передние фронты входных и тактовых импульсов почти совпадают во времени (например, в момент t<) и первый триггер 4 регистра может не переключиться по этому такту, а переключится по следующему такту в момент времени при этом на его выходе 13 появится сигнал уровня логической "1". Последующими тактами в моменты времени и t сигнал уровня логической "1" передвигается по регистру, появляясь на выходах 14 и 15. В результате этого на выходе 21 элемента ИЛИ 5 формируется обобщенный сигнал уровня логической 1

В момент времени t > на входе 1 регистра появляется второй импульс обрабатываемой последовательности, который может записаться в первый разряд регистра по переднему фронту очередного тактового импульса.

В результате произойдет искажение интервала между первым и вторым импульсами обрабатываемой импульсной последовательности . на входе регистра интервал между передними фронтами нм—

70!5

5 160 пульсов равен ЗТ, а в регистре интер-, вал между ними ранен 2Т.

Импульсы обрабатываемой последовательности передвигаются в регистре, появляясь поочередно на его выходах

16-20. При этом в момент времени первый импульс появляется на выходе

17 триггера 4 > и через элемент ИЛИ 7 тт тт в виде сигнала логической 1 поступает н а один из входов элемента И 8, н а другом входе которого присутствует также сигнал уровня логической единицы с выхода элемента ИЛИ 5 . В ре з ультате н а входе триггера 1 1 появ т яе т ся тт сигнал уровня логическои 1

В момент времени 7 по инвертированному тактовому импульсу триггер 11 срабатывает и на его прямом выходе 23 появляется сигнал уровня логической

"1", а на инверсном - сигнал уровня логического "0", который, поступая через элемент И 9 на R-входы триггеров 4т-4> регистра, устанавливает их в исходное состояние. Таким образом, в.торой импульс входной последовательности, следующий с искаженным интервалом за первым, не будет записан в следующий разряд регистра — триггер 44.

В момент времени t переключается триггер 12, на его выходе 24 появля— ется сигнал уровня логической "1", . поступающий через элемент ИЛИ 6 на вход триггера 44. В момент времени (т,е. через интервал времени, равный 3T) второй импульс обрабатываемой последовательности записывается в четвертый разряд регистра — триггер

4, Таким образом происходит восстановление интервала времени между первым и вторым импульсами последовательности, поскольку в этот момент времени первый импульс находился в седьмом разряде регистра.

В момент времени t o и t« на входе регистра с выхода устройства для записи информации появляются третий и четвертый импульсы последовательности, которые записываются в регистр в моменты времени t< и t<, т,е. с искажением интервала между вторым и третьим импульсами (он увеличивается на Т). Работа устройства в данном случае аналогична описанной выше, только .для восстановления интервала между вторым и третьим импульсами используется сигнал с выхода 20 триггера 4 регистра.

Таким образом, в результате кор рекции интервалов времени между импульсами обрабатываемой последовательности в регистре сдвига, начиная с четвертого разряда, продвигаются импульсы с восстановленными интервалами следования.

Входная импульсная последовательность на вход регистра сдвига поступает через устройство записи информации, приведенное на фиг,З, которое состоит из D-триггера 25 и инвертора

26 и работает следующим образом.

Импульсы входной последовательности поступают на счетный вход D-триггера 25, который срабатывает по пе-, реднему фронту входного импульса и на его выходе (входе 1 регистра сдвига) появляется сигнал уровня логической "1". При поступлении на вход 2 регистра сдвига тактового импульса на выходе триггера 4 первого разряда регистра появляется сигнал уровня логической "1", который, поступая через инвертор 26 íà R-вход D-триггера 25, устанавливает его в исходное состояние. Прт поступлении на вход 2 регистра сдвига следующего тактового импульса на выходе триггера 4т устанавливается сигнал уровня логического

"0", который, поступая через инвертор

26 на R-вход D — триггера 25, разрешает его работу (т. е, срабатывание по приходу следуюцтего входного импульса).

Формула изобретения

Регистр сдвига, содержащий триггеры, С вЂ” входы которых объединены и являются тактовым входом, D-вход первого триггера является информационным входом, а R-входы триггеров, начиная с четвертого, являются входом начальной установки регистра, прямые вюходы каждого триггера, кроме третьего и последнего, соединены с Р-входами последующих триггеров регистра, прямой выход последнего триггера является информационным выходом регистра, о т л и ч а ю цт и и с я тем, что, с целью повышения достоверности передачи информации, в него введены три элемента ИЛИ, два элемента И, инвертор и два корректирующих триггера, причем входы первого элемента ИЛИ соединены с прямыми выходами первого, второго и третьего триггеров регистра, а выход — с первым входом первого

1607015 (7

Фиа. Л

Составитель А.Дерюгин

Редактор А,Маковская Техред M.Õîäàíè÷ Корректор М,Максимишинец

Заказ 3552

Тираж 487

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, R-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г, Ужгород, ул, Гагарина, 101 элемента И, выход которого соединен с D-входом первого корректирующего триггера, прямой выход которого соединен с D-входом второго корректирующего триггера, а инверсный выход с входом второго элемента И, выход которого соединен с R-входами первого, второго и третьего триггеров регистра, а второй вход — с R-входом четвертого триггера регистра, входы второго элемента ИЛИ соединены с прямыми выходами третьего триггера регистра и второго корректирующего

3 триггера, а выход — с D-входом четвертого триггера регистра, С-вход которого соединен с С-входом второго

5 корректирующего триггера и через инвертор — с С-входом первого корректирующего триггера, à R-вход — с R-вхо/ дами первого и второго корректирующих триггеров, входы третье ro элемента

10 ИЛИ соединены с прямыми выходами пятого и восьмого триггеров регистра, а выход — с вторым входом первого элемента И.