Аналого-цифровой преобразователь с коррекцией динамической погрешности

Иллюстрации

Показать всеРеферат

Изобретение относится к информационно-измерительной технике и предназначено для преобразования аналогового сигнала в цифровой код методом поразрядного уравновешивания с многоступенчатой коррекцией динамической погрешности. Цель изобретения - уменьшение времени преобразования - достигается тем, что в аналого-цифровой преобразователь с коррекцией динамической погрешности, содержащий сравнивающее устройство, блок суммирования, основной цифроаналоговый преобразователь и корректирующий цифроаналоговый преобразователь, генератор тактовых импульсов, регистр последовательных приближений, регистр с элементами переноса единицы, введены RS-триггеры и элементы ИЛИ. 1 з.п. ф-лы, 4 ил., 1 табл.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

PECllV6flHH (51)5 Н 03 М l,/06, 1/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗ06РЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР! (21) 4301051/24-24 (22) 04.09.87 (46) 15.11.90. Бюл. № 42 (71) Пензенский политехнический институт (72) В. С. Грубник, Ю. В. Полубабкин и Б. Г. Дорфман (53) 68!.325 (088.8) (56) Авторское свидетельство СССР № 293297, кл. Н 03 М 1/46, 1968.

Авторское свидетельство СССР № 330538, кл. Н 03 М 1/46, 1970. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ С КОРРЕКЦИЕЙ ДИНАМИЧЕСКОЙ ПОГР1..Ш НОСТИ (57) Изобретение относится к информационно-измерительной технике и предназначено

Изобретение относится к области информационно-измерительной техники и предназначено для преобразования аналогового сигнала в цифровой код методом поразрядного уравновешивания с многоступенчатой коррекцией динамической погрешности.

Цель изобретения — уменьшение времени преобразования.

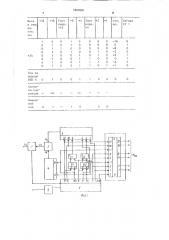

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 — конструкция регистра с элементами переноса единицы; на фиг. 3 — временная диаграмма

его работы; на фиг. 4 — диаграмма состояний компенсирующего напряжения АЦП с двухступенчатой коррекцией динамической погрешности.

Устройство содержит сравнивающее устройство 1, блок 2 суммирования, основной цифроаналоговый преобразователь (ЦАП)

3 и корректирующий цифроаналоговый преобразователь (LIAH) 4, генератор 5 тактовых импульсов (ГТИ), регистр 6 последова-. тельных приближений (РПП), элементы

ИЛИ 7, регистр 8 с элементами переноса единицы, RS-триггеры 9.

ÄÄSUÄÄ 1607076 A 1

2 для преобразования аналогового сигнала в цифровой код методом поразрядного уравновешивания с многоступенчатой коррекцией динамической погрешности. Цель изобретения — уменьшение времени преобразования — достигается тем, что в аналогоцифровой преобразователь с коррекцией динамической погрешности, содержащий сравнивающее устройство, блок суммирования, основной цифроаналоговый преобразователь и корректирующий цифроаналоговый преобразователь, генератор тактовых импульсов, регистр последовательных приближений, регистр с элементами переноса единицы, введены RS-триггеры и элементы ИЛИ.

1 з. п. ф-лы, 4 ил., табл.

Регистр 8 с элементами переноса единицы (фиг. 2) состоит из счетчиков 10, формирователя 11 импульсов (ФИ), элементов

И 12, элементов ИЛИ !3.

Устройство работает следующим образом.

На сравнивающее устройство 1 подаются для сравнения входное напряжение U„ и результирующее напряжение U =LO+U».

Если 1„)Г„, то на выходе блока формируется «!». Если 11„(! !,, то формируется «О». Эти сигналы поступают на вход последовательных данных РПП 6. Выходы параллельных данных РПГ1 6 условно делятся на основные и корректирующие. Основные выходы РГIП 6 подключены к входам ЦАП 3, а корректирующие — к входам ЦАГ1 4.

ГТИ 5 запускается строб-импульсом по входу и начинает вырабатывать импульсы, период которых равен такту уравновешивания, причем количество импульсов определяется разрядностью АЦП и числом ступеней коррекции. По первому импульсу с ГТИ 5 на выходе параллельных данных РПГI 6 создается кодовая комбинация {1000...000) и по1607076 следующими импульсами «1» сдвигается в сторону младших разрядов, включая и выключая разряды ЦАП 3 и ЦАП 4. Таким образом, осуществляется уравновешивание входного напряжения 11„компенсирующим напряжением U . Необходимо отметить, что одновременно с включением старшего разряда из группы корректируемых разрядов первой ступени коррекции ЦАП 3 должен включиться разряд, являющийся старшим в группе разрядов ЦАП 3 второй ступени коррекции динамической погрешности.

Этот разряд обеспечивает необходимое для работы алгоритма коррекции смещение компенсирующего напряжения Vo, так как динамическая погрешность знакопеременна.

Таким образом, диапазон значений динамической погрешности становится однополярным и значительно упрощается реализация алгоритма коррекции. Причем включается этот разряд одновременно с включением корректирующего разряда ЦАП 4, по весу равного весу последнего разряда в данной ступени коррекции динамической погрешности.

Управление смещающими разрядами создается с помощью RS-триггеров 9 и элементов ИЛИ 7, причем S-входы триггеров соединены со старшими разрядами из группы корректируемых, а.R-входы с выходами корректирующих тактов РПП 6.

Корректирующий малоразрядный ЦАП 4 опрашивается РПП 6 в момент такта коррекции, а создаваемое им корректирующее напряжение Uq участвует в процессе уравновешивания V„.

Коррекция результата преобразования производится в конце цикла преобразования в регистре элементами 8 переноса единицы.

Рассмотрим работу регистра 8 по функциональной схеме на фиг. 2. Входы счетчиков 10 соединены с входной шиной регистра.

Запись информации в счетчики старших разрядов осуществляется строб-импульсом, который формируется ФИ 11 по моменту включения одного из младших разрядов преобразователя (фиг. 4). Корркция результата преобразования АЦП производится прибавлением единицы к коду корректируемых разрядов, хранимых в регистре 8. Эта операция реализуется в счетчиках 10 старших разрядов ЦС по входам переноса единицы сигналом «Конец преобразования» и этим же сигналом осуществляется запись информации в счетчик младших разрядов. Элементы И 12 разрешают прохождение сигналов коррекции через элементы ИЛИ 13 на входы 1 счетчиков 10 по сигналу «Конец преобразования». Если в результате коррекции произойдет переполнение каких-то счетчиков, то с выходов переполнения P импульсы через элементы 13 поступят на входы +1 счетчиков 10 более старших разрядов.

Информационные выходы счетчиков 10 под50

55 дов в 4 раза меньше весов разрядов первой ступени коррекции.

Диаграмма состояний компенсирующего напряжения АЦП с двухступенчатой коррекцией динамической погрешности при уравновешивании U„= 24 отн. ед. приведена на фиг. 4. На диаграмме по оси у отложены в относительных единицах значения Бр и U„, по оси х — длительность такта уравновешивания. ключены к выходной шине регистра 8, с которой снимается выходной код АЦП.

Применение в регистре 8 стробируемых счетчиков позволяет осуществить хранение информации на выходе приблизительно на время цикла преобразования в данном АЦП.

Рассмотрим более подробно работу АЦП с коррекцией динамических погрешностей .по функциональной схеме на фиг. 1 на примере 6-разрядного АЦП с последовательной двухступенчатой коррекцией динамической п огре ш иост и.

Пусть U, 24 отн. ед., а компенсирующее напряжение

1.1р = Uo+U», 15 где Uo — выходное напряжение 6-разрядного ЦАП 3;

U» — корректирующее напряжение 2разрядного ЦАП 4 с весами, равными 16 и 4 отн. ед.

По сигналу запуска ГТИ 5 формирует серию из 8-тактовых импульсов. На выходе

РПП 6 устанавливается первоначальная кодовая комбинация 1000000 (см. таблицу) и начинает опрашиваться ЦАП 3, причем одновременно с опросом старшего разряда

ЦАП 3 устанавливается в «1» по S-входу положительным фронтом сигнала триггера 9 и через элемент ИЛИ 7 включается разряд с весом 8 отн. ед. ЦАП 3, который и создает смещающее напряжение Uoo, причем кодовая комбинация становится 10010000. В

30 дальнейшем уравновешивание происходит так же, как и в классической схеме поразрядного преобразования (см. таблицу). Отличие заключается лишь в том, что в момент включения корректирующего напряжения U»

ЦАП 4 сигналом такта коррекции с РПП 6, 35 положительным фронтом по R-входу RSтриггер 9 сбрасывается в «О» и в результате отключается напряжение смещения Uos, создаваемое ЦАГ1 3 (см. таблицу).

Если при этом оказывается, что: — AU) 0, 40 то по сигналу со сравнивающего устройства 1 разряд с весом 16 отн, ед. корректирующего ЦАП 4 остается включенным в

РПП 6 и к цифровому коду в регистр 8 прибавляется «1» по сигналу РПП 6 «Конец преобразования»; — AU(0, то коррекция не

45 производится и разряд с весом 16 отн. ед.

ЦАП 4 отключается.

Для второй ступени коррекции динамической погрешности алгоритм коррекции работает аналогичным образом. Отличие заключается только в том, что веса всех разря1607076

Формула изобретения

На диаграмме отражен процесс уравновешивания входного сигнала в соответствии с таблицей.

В конце цикла преобразования в регистр 8 по информационным входам будет записан код 010100, который по сигналу

«Конец преобразования» скорректируется по результату второго такта коррекции. Код на выходе регистра 8 в этом случае будет соответствовать истинному коду 011000.

Подобный алгоритм коррекции динамической погрешности позволяет корректировать динамическую погрешность от переходного процесса, возникающего при установлении компенсирующего напряжения старших разрядов ПКН. В данном случае при установлении разрядов ПКН с весами 32 отн. ед. и 16 отн. ед. погрешность установления допускается в размере + 8 отн. ед. для первой ступени коррекции, а для второй

+- 2 отн. ед.

Устройство по сравнению с известным обеспечивает более высокое быстродействие, так как из цепи последовательных приближений исключается регистр 8, т. е. сокращается элементарный такт АЦП. Причем этот выигрыш по быстродействию проявляется тем сильнее, чем больше число разрядов

АЦ-преобразования.

Кроме того, устройство в отличие от прототипа имеет возможность хранить результат преобразования весь следующий цикл.

Данный алгоритм в предложенном аналого-цифровом преобразователе позволяет наращивать разрядность АЦП и увеличивать число ступеней коррекции по сравнению с рассмотренным примером.

1. Аналого-цифровой преобразователь с коррекцией динамической погрешности, содержащий сравнивающее устройство, первый вход которого является входной шиной„ второй вход соединен с выходом блока суммирования, первый и второй входы которого соединены соответственно с выходами основного и корректирующе.о цифроаналоговых преобразователей, входы последнего из которых соединены с соответствующими корректирующими выходами регистра последовательного приближения, тактовый вход которого соединен с выходом генератора тактовых импульсоз, подключенного к шине запуска, а и«формационнь1й вход соединен с выходом сравнивающего устройства, а также регистр с элементами переноса единицы, информационные входы которого соединены с

50 соответствующим«основными выходами регистра последовательных приближений, отличаюшийся тем, что, с целью уменьшения времени преобразования, в него введены элементы ИЛИ и RS-триггеры по числу разрядов коррекции, R-входы которых подключены к соответствующим корректирующим выходам регистра последовательных приближений, основные выходы которого с весом разряда, предшествующим весу разряда корректирующих выходов, подключены к S-входам триггеров соответственно и объединены с первыми входами соответствующих элементов ИЛИ, кроме последнего, а первый вход последнего элемента ИЛИ подключен к основному выходу с весом разряда, следующим за весом разряда корректирующего выхода регистра последовательного приближения, вторые входы элементов ИЛИ соединены с выходами соответствующих RS-триггеров, а выходы элементов ИЛИ соединены с входами соответствующих разрядов основного цифроаналогового преобразователя, следующих по весу за корректируемыми, остальные разряды основного цифроаналогового преобразовател я подкл ючены к с оответствующим основным выходам регистра последовательных приближений, выход, конец преобразования которого подключен к входу стробирования регистра с элементами переноса единицы, выходы которого являются выходной шиной, а корректирующие входы соединены соответственно с корректируюгцими выходами регистра последовательных приближений.

2. Преобразователь по и. 1, от,гичаюигийся тем, что регистр с элементами переноса единицы выполнен на счетчиках, формирователе импульсов, элементах И и ИЛИ, причем корректирующими входами блока являются первые входы соответствующих элементов И, вторые входы которых объединены между собой, и с входом стробирования счетчика младших разрядов и являются входом стробирования блока, а выходы соединены с первыми входами -оответствующих элементов ИЛИ, второй вход каждого из которых подключен к выходу переполнения счетчика более младшего разряда, а выходы элементов ИЛИ соединены с входами переноса единицы соответствующих счетчиков, кроме счетчика младших разрядов. входы старшего разряда которого через формирователь импульсов соединен - входами стробирования счетчиков старших разрядов, информационные входы счетчиков являются основными входами блока, а выходы -- выходной шиной.!

607076

Веса +32 +16 х отн.

+8 +4 Такт +2

Такт

Сигнал

СУ 1 отн. корр.

+16 корр. ь4 ед. ед. отн. ед.

+24!

<од на выходе

РПП б 0

1 О О 1

1 О О О

Сигналы коррекции

Выходной код 0

1 О

О О

32 Ю 8

1 О О 1 О О О

О 1 0 1 О 0 О

О 1 1 О О О О

О 1 О 1 О О 1

О 1 О О 1 0 1

О 1 О О 1 1 О

0 1 О О 1 1 1

О 1 0 О 1 1 О

О -16

О О

О -8

О -2

О +2

О О

О -2

1 -1

О

О

О

1

О

1607076

Оа, СтКед 56

1б

S од

ПП

1607076

Гигнсы юнец прйфй23

Сигнал на йвчай

Р

&гнал юррегцио

HQ дыкйЖ

И, ИМИ

С /Г/ Q4g g в 82, Жгуаг на бьиоде

p03p%%3 78 рюш f87

Составитель é3. Махна но в

Редактор О. Спесивых Техред A. Кравчук Корректор М. Макси мишинец

Заказ 3555 Тираж бб9 П одписнсе

ВНИИГ1И Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж 35, Раушская наб., д. 4!5

Произвоастве..но-нздателпский когибинат «Г1агент», г. Ужгород, ул. Гагарина, 101