Устройство для вычисления функций @ и @

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях. Целью изобретения является повышение быстродействия за счет непосредственной проверки сходимости итерационного процесса. Устройство содержит первый коммутатор 1, второй коммутатор 2, первый регистр 3, второй регистр 4, первый регистр-сдвигатель 5, второй регистр-сдвигатель 6, третий регистр-сдвигатель 7, первый сумматор 8, второй сумматор 9, первый блок 10.1 памяти опорных значений функции, второй блок 10.2 памяти опорных значений функции, блок 11 инверсии разрядов, первый элемент И 12, второй элемент И 13, элемент ИЛИ 14, элемент НЕ 15, элемент ИЛИ-НЕ 16, вход 17 младших разрядов аргумента, тактовый вход 18, вход 19 запуска, вход 20 старших разрядов аргумента, выход 21 признака окончания вычислений, выход 22 косинуса, выход 23 синуса. 1 ил.

Р1) О Оо Р 7/548

ГО

ПО

ПР (2 (2 (4 (7 ту (7

Г. и (5 .(5 зи св (5 (5 те ва ля

О

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

/б =.— РЕСПУБЛИК

УДАРСТВЕННЫЙ НОМИТЕТ

ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ГКНТ СССР

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

) 4624007/24-24

) 22.12.88

) 23.11.90 ° Бюл. 9 43

) Московский лесотехнический инсти) А.И.Береэенко, А.Д.Марковский, .Меликов, В.В,Полянский .Ю.Афанасьева

) 6Pl 325(088.8)

) Авторское свидетельство СССР

26651, кл.G 06 F 7/548, 1982.

Байков В.Д., Смолов В.Б. Специалиованные процессоры. Итерационные оритмы и структуры. N.: Радио и зь, 1985, с.137, рис.3.10.

) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНК) Изобретение относится к вычислиьной технике и может быть испольэоо в специализированных вычислитеЦелью изобретения является повы2 шение быстродействия sa счет непосредственной проверки сходимости итерационного процесса. Устройство содержит первый коммутатор 1, второй коммутатор 2, первый регистр 3, второй ре" гистр 4, первый регистр-сдвигатель 5, второй регистр сдвигатель 6, третий регистр-сдвигатель 7, первый сумматор 8, второй сумматор 9, первый блок 10.1 памяти опорных значений функции, второй блок 10.2 памяти опорных значений функции, блок 11 инверсии разрядов, первый элемент И 12, вто" рой элемент И 13, элемент ИЛИ 14, элемент НЕ 15, элемент ИЛИ-НЕ 16, вход 17 младших разрядов аргумента, тактовый вход 18, вход 19 запуска вход 20 старших разрядов аргумента, выход 21 признака окончания вычислений, выхоц 22 косинуса, выход 23 синуса. 1 ил.

1608651

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислителях.

Целью изобретения является повышение быстродействия за счет непосредственной проверки сходимости итерационного процесса.

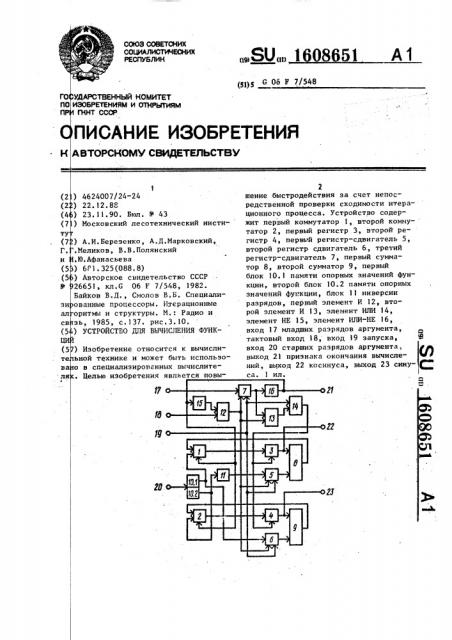

На чертеже представлена функциональная схема устройства.

Устройство содержит первый 1, второй 2 коммутаторы первый 3 и второй 4 регистры, первый 5, второй 6 и третий 7 регистры"сдвигатели, первый 8и второй 9 сумматоры, первый 10.1 и второй 10.2 блоки памяти опорных значений функции, блок 11 инверсии разрядов, первый .12 и второй 13 элементы И, элемент ИЛИ.14, элемент НЕ 15,. 20 элемент ИЛИ-НЕ 16, вход 17 младших разрядов аргумента, тактовый вход 18, вход 19 запуска, вход 20 старших разрядов аргумента, выход 2) признака окончания вычислений, выход 22 коси-. 25 нуса и выход .23 синуса.

Устройство функционирует следующим образом.

Устройство осуществляет обработку (n+1)-разрядных двоичных чисел, пред- З0 ставленных в формате с фиксированной запятой.

В основе работы. устройства лежит следующий алгоритм вычисления функций

x = cosg и = sin Cp . Значение поло.— жительного аргумента (P определяе35 мое двоичным кодом а, а „... а д., где ао - разряд целой части; а,а а — разряд дробной части аргумента, представляется в виде (I = ф + %2 = аоa„, ° ° ., а + 00..., а, „,...,a„, п где ц и/2, q B (l,2,...,п ; — g0. * 2

По значению величины ф определя- 45 ются начальные и-разрядные приближе" ния вычисляемых функций х = созф,, у = sing . Последующие вычисления проводятся с использованием итерационных соотношений 50 хк хк- U„ а +к

УК = ук Ф+ Ек1 а%+к (2)

Е„ ° 2 (3)

-(+к1

u -=y,2" (4)

Полученные в результате (и-q)-и итерации величины х „ и у„ являются искомыми значениями функций х = cosy и у = sing с абсолютной погрешностью, не превышающей 2

В исходном состоянии все разряды кода на выходе третьего регистрасдвигателя 7 имеют нулевое значение, вследствие чего значение признака окончания вычислений на выходе элемента ИЛИ-НЕ 16, являющегося одновременно первым выходом 21 устройства, равно единице. Единичное значение поступает на управляющие входы первого 1 и второго 2 коммутаторов, обеспечивая прохождение на выходы коммутаторов информации, поступающей на их вторые информационные входы.

На тактовый вход 18 устройства непрерывно поступают тактовые импульсы (ТИ). На входы 17 и 20 устройст" ва поступают младшие д и старшие ( разряды аргумента соответственно, По значению кода Р из блоков 10.1 и 10.2 памяти опорных значений функций считываются величины х о и уо

Величина х о поступает на второй инфор мационный вход первого коммутатора 1 и далее с выхода первого коммутатора 1 на информационный вход первого регистра 3, а также со сдвигом íà q разрядов вправо на информационный вход второго регистра- сдвигателя 6. Величина у поступает на второй информационный вход второго коммутатора 2 и далее с выхода второго коммутатора 2— на информационный вход второго регистра 4, а также со сдвигом на о разрядов вправо на вход блока 11 инверсии разрядов и. далее на информационный вход первого регистра-сдвигателя 5, Для выполнения вычислений синхронно с одним из ТИ на вход 19 устройства поступает сигнал "Пуск", который проходит на входы синхронизации запи" си первого 5, второго 6 и третьего 7 регистров-сдвигателей, осуществляя занесение в эти регистры значений (-у 2 1 и х ° 2 1 соответственно, Кроме того, сигнал "Пуск" проходит через элемент ИЛИ 14, осуществляя занесение. в регистры 3 и 4 значений хо и у соответственно

При нулевом значении всех разрядов кода Ц, занесенного в третий регистрсдвигатель 7, значение признака окончания вычислений остается равным единице, вычисления не выполняются и в качестве результатов операции используются значения х и у .

160865 ног ка вит ден он ко око пер

ТИ вог ния по пе го хо ро ко ци ко

18 ме ре ва во ма те бо зн пе вь об че ли вт до не тр им вь ся ти э л ра

Ф ри единичном значении хотя бы одразряда кода д значение признаа выходе элемента ИЛИ-НЕ 16 станоя равным нулю, обеспечивая прохож- 5 е информации с первых информаци- х входов первого 1 и второго 2 таторов. вертированное .значение признака чания вычислений на втором входе

oro. элемента И 12 становится равединице, обеспечивая прохождение входа 18 устройства на выход перэлемента И 12. ри выполнении К-й итерации значе-(Ч,+к) -(ч % к) хк-1 -ук-, 2 у„,, х к- 2 тупают на входы первого и второслагаемых первого сумматора 8 и вого и второго слагаемых второсумматора 9 соответственно, На вы- 20 ах первого 8 и второго 9 сумматоформируются значения х „=x „,—

-(q, ) (1)

2 и у„=у„, +х к, 2 орые поступают на первые информанные входы первсго 1 и второго 2 мутаторов.

Очередной ТИ, приходящий на вход устройства, с выхода первого элета И 12 поступает на входы сдвига истров-сдвигателей 5-7, обеспечи30 по заднему фронту ТИ сдвиг впргна один разряд информации, храняся в регистрах-сдвигателях 5 и 6, двиг влево на один разряд инфории, хранящейся в регистре-сдвига в 35 е 7, с занесением нулей в осводающиеся разряды. При единичном чении величины а +к ТИ с выхода. вого элемента И 12 проходит на од второго элемента И 13 и далее, 4О спечивая по переднему фронту.ТИ ись в региг ры соответственно энаий х „ и ук согласно выражениям и (2). При нулевом значении веины а +к содержимое первого 3 и 45 рого 4 регистров не изменяется.

Процесс вычислений продолжается момента, когда в результате выполия очередной итерации все разряды тьего регистра-сдвигателя будут ть нулевое значение. При этом на оде элемента ИЛИ-НЕ 16 сформируетединичное значение, которое запрепрохождение ТИ на выход первого мента И 12 и устройство прекратит оту. р м у л а изобретения

Устройство для вычисления функв п g u соя, содержащее два

1 6 сумматора, два блока памяти опорных значений функции,три регистра-сдвигатеЛя и два регистра, причем входы старших разрядов аргумента устройства.соединены с адресными входами первого и второго блоков памяти опорных значений функции, выходы первого и второго регистров соединены с входами первых слагаемых соответственно " первого и второго сумматоров, выходы первого и второго регистров-сдвигателей соединены с входами вторых слагаемых соответственно первого и второго сумматоров, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия за счет непосредственной проверки сходимости итерационного процесса, в него дополнительно введены два.коммутатора, блок инверсии разрядов, два элемента И, элемент

ИЛИ-НЕ,.элемент ИЛИ и элемент НЕ,причем вход запуска устройства соединен с входом синхронизации записи регистров-сдвигателей с первого по третий и с перрым входом элемента ИЛИ, тактовый вход устройства соединен с первым входом первого элемента И, выход которого соединен с входами сдвига регистров-сдвигателей с первого по третий и с первым входом второго элемента И, вход младших разрядов аргумента устройства соединен с информационным входом третьего регистра-.. сдвигателя, выходы разрядов которого соединены с соответствующими входами элемента ИЛИ-НЕ, выход которого соединен с входом элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход старшего разряда третьего регистра-сдвигателя соединен с вторым входом второго элемента И, выход которого соединен с. вторым входом элемента ИЛИ, выход которого соединен с синхронизирующими входами первого и второго регистров, информационные входы которых соединены с выходами соответственно первого и второго коммутаторов, первые информационные входы которых соединены с выходами соответственно первого и второго сумматоров, управляющие вхо.— ды первого и второго коммутаторов соединены с выходами элемента ИЛИ-НЕ, выход первого блока памяти опорных значений функции соединен с информационным входом второго регистра-сдвигателя и с вторым информационным входом первого коммутатора, вьп:од второ1608651

Составитель С.Куликов

Техред М,Ходанич Корректор СЛерни

Редактор АЛ1андор

Ю"

Заказ 3617 Тираж 566 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Рауаская наб., д. 4/5

Производственно-издательский комбинат "Патент", г.ужгород, ул. Гагарина, 101

ro блока памяти. опорных значений функции соединен с вторым информационным входом второго коммутатора и с входом блока инверсии разрядов, выход которого соединен с информационным входом первого регистра-сдвигателя, выход элемента ИЛИ-НЕ соединен с выходом признака окончания вычислений устройства, выходы первого и второго регистров соединены с выходами соответственно косинуса и синуса устройства.