Устройство для возведения в степень @ -разрядных двоичных чисел

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах для вычисления степенных функций. Цель изобретения - повышение быстродействия устройства. Устройство имеющее информационные входы и вход управления, содержит умножитель, четыре регистра, блок управления операцией и коммутаторы. В рабочем режиме на информационные входы поступают значения основания и показателя степени. На выходе устройства получают вычисленное значение степенной функции. 9 ил.

(С (4) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В, ЕПЕНЬ п-РАЗРЯДНЫХ ДВОИЧНЧХ ЧИСЕЛ

7) Изобретение относится к вычисли(2 (2 (4 (7

Л. (5 (5

) 4661320/24-24

) 25,01.89

) 23.11.90. Бюл. 0 43

) С.Н. Макареня, С.А. Гуща, Авгуль и А.И. Хилько

) 681.325(088.8)

) Авторское свидетельство СССР

531153, кл. 6 06 F 7/38, 1979.

Авторское свидетельство СССР

809171, кл. G 06 F 7/38, 1981. тельной технике и может быть использовано в специализированных вычислительных машинах для вычисления степенных функций. Цель изобретения — повышение быстродействия устройства.

Устройство, имеющее информационные входы и вход управления, содержит умнояитель, четыре регистра, блок управления операцией и коммутаторы. В рабочем режиме на информационные входы поступают значения основания и показателя степени, На выходе устройства получают вычйсленное значение степенной функции. 9 ил. т в п н н в (.ф

P ( т р (. м

Изобретение относится к вычислиьной технике и может быть использоно при разработке спциализированных оцессоров, Цель изобретения — повышение быстдействия.

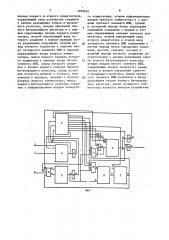

На фиг.1 представлена структуря схема предлагаемого устройства; фиг.2 — р-разрядный регистр и пер@ элемент ИЛИ; на фиг.З вЂ” первый

n/2-разрядный) коммутатор; на г.4 — kn/2-разрядный регистр и втой элемент ИЛИ; на фиг.5 - второй и-разрядный) коммутатор; на фиг.6— рвый kn-разрядный регистр и элемен1 ИЛИ; на фиг. 7 — третий (kn/2-раздный) коммутатор; на фиг.8 - четвертый и-разрядный) коммутатор; на,фиг.9ропрограмма работы устройства.

Устройство содержит входы 1 и 2 казателя и основания степесоответственно, управляющий вход 3 устройства, р-разрядный С„ регистр 4, kn/2-разрядный регистр 5, первый 6 и второй 7 kn-разрядные ре| гистры, kn/2-разрядный умножитель 8, блок 9 управления операцией (БУО), первый коммутатор 10, первый элемент

ИЛИ 11, выход 12 первого коммутатора, вход 13 второго элемента ИЛИ 14 с выходом 15, вход 16 и выход 17 умножитепя 8, выход 18 регистра 7, входы

19 и 20 коммутатора 21 и его выход 22, входы 23 и 24 третьего элемента ИЛИ

25, его выход 26, выход 27 регистра 6, входы 28 и 29 коммутатора 30, вход 31 умножителя 8, коммутатор 32, выход 33 устройства, вход 34 четверто- « Э

ro элемента ИЛИ 35 с выходом 36, вход д, 37 коммутатора 10, входы 38 и 39 коммутатора 21, входы 40 и 41 элемента ИЛИ 42 с выходом 43, вход 44 рс гистра 6 входы 45 и 46 коммутатора

30, вход 47 разрешения записи регист1608654 ра 7, вход 48 коммутатора 32, вход 49. регистра 4, вход 50 и выход 51 коммутатора 10, входы 52 и 53 регистров 6 и 4 соответственно.

Устройство, работает следующим образом.

Исходным состоянием устройства может быть любое, которое определяется результатом выполнения предыдущей операции возведения в степень. При подаче на входы 1 и 2 устройства соответственно показателя степени и основания в двоичном коде, а также при подаче на вход 3 сигнала логической единицы устройство переходит в начальное состояние (блок управления операцией (БУО) находится в начальном состоянии, которое определяется наличием сигнала логического нуля на выходе элемента ИЛИ 35). Одновременно значение показателя степени запоминается в регистре 4, открывается коммутатор 10 и код основания записывается в регистр 5. 25

На первом входе БУО 9 — сигнал логического нуля, при этом на выходах

БУО 9 — сигналы логического нуля. После окончания импульса подаваемого на вход 3, устройство начинает функционировать. Предположим, что основание А-1101, à показатель степени

В-1011 тогда БУО 9, который находился в начальном состоянии, на втором, третьем и четвертом входах сигналы. логической единицы, поэтому БУО 9 фор- 35 мирует на втором, четвертом и шестом .выходах управляющие сигналы логической единицы, которые открывают коммутаторы 21 и 30 по входам 20 я 29 соот40 ветственно и разрешает запись информации в регистр 6 сигналом логической единицы с выхода 43 элемента ИЛИ 42, при этом информация с выхода регистра 5 поступает через открытый комму45 татор 21 в регистр 6 и запоминается, а информация с коммутатора 30 поступа, ет иа вход 31 умножителя 8. На выходе

36 элемента ИЛИ 35 появляется сигнал логической единицы, по которому БУО 9 переходит в рабочее состояние. На вто50 рой вход умножителя 8 информация поступает с выхода регистра 5 и формируД ется на выходе произведение АА=А которое запоминается в регистре 7, далее БУО 9 формирует сигнал логической единицы на первом выходе, открывается коммутатор 10 по входу 18 и информация с выхода регистра 7 через открытый коммутатор 10 поступает на вход 12 регистра 5 и запоминается в БУО 9.

На девятом выходе формируется. сигнал логической единицы, который управляет сдвигом информации в регистре 4, при этом на других выходах БУО 9— .сигналы логического нуля, информация в регистре 4 сдвигается вправо на один разряд, теперь на втором, четвертом и пятом входах БУО 9 — сигналы логической единицы. БУО 9 формирует сигнал логической единицы на третьем выходе, которым открывается коммутатор 30 по информационному входу 28, и на шестом выходе, при котором информация из регистра 6 (в рассматриваемом случае— значение А) через открытый коммутатор 30 поступает на вход 31 умножителя 8. На вход умножителя 8 подается информация с выхода 16 регистра 5 ( в рассматриваемом случае — значе-. ние А ) и формируется произведение

А А =А, которое запоминается в региг. э стре 7. Далее БУО 9 формирует на пятом выходе сигнал логической единицы, который открывает коммутатор 21 по входу 19 и информация с выхода 18 регистра 7 поступает через открытый коммутатор 21 на вход 22 регистра 6 и запоминается.

Далее БУО 9 формирует управляющие сигналы логической единицы на четвертом и шестом выходах,при этом коммутатор 30 открывается по входу 29 и информация с выхода регистра 5 поступает на вход 31 умножителя 8, на выхо-, де 17 которого получаем произведение

А А .=А и информация запоминается

2 + в регистре 7. БУО 9 формирует сигнал на первом выходе и информация с выхода регистра 7 через открытый коммутатор

10 по входу 18 поступает на вход 12 регистра 5 и запоминается. БУО 9 формирует после этого управляющий сигнал на девятом выходе и информация в регистре 4 сдвигается вправо на один разряд. Теперь на втором входе БУО 9 сигнал логического нуля, а на четвертом и пятом — сигналы логической единицы. Так как БУО 9 находится в рабочем состоянии, то он формирует управляющие сигналы на четвертом и шестом выходах. Информация с выхода регистра 5 через открытый коммутатор

30 поступает на первый вход 31 умножителя 8, на выходе которого форми4„а руется произведение.A " А А и заломинается в регистре .7. После этого

) 60865

БУ н х к

P н е с п н с

Ц ть

31 в е ф

Н в р с вь с

Т

Б н е

P с к с к

У н т н и х ч

Б

9 формирует управляющий сигнал первом выходе и информация с выа регистра 7 поступает через оттый коммутатор 10 на вход регист5 и запоминается. БУО 9 формирует

5 девятом выходе сигнал логической ницы, информация в регистре 4 вигается вправо на один разряд. Теь на втором БУО 9 сигнал логичес- 10 го нуля, а на четвертом и пятом одах — логические единицы. БУО 9 третьем и шестом выходах формирует гналы логической единицы и информая с выхода регистра 6 через открыкоммутатор 30 поступает на вход умножителя 8 и формируется произдение А А =А, ко орое эапоминаЬ. Ъ 11 ся в регистре 7. После этого БУО 9 рмирует сигнал логической единицы 20 четвертом выходе и информация с хода регистра 7 через открытый комтатор 21 поступает на вход регист6 и запоминается. БУО 9 формирует гнал логической единицы на девятом 2S оде и информация в регистре 4 вигается вправо на один разряд. перь на втором и четвертом входах

О 9 — сигналы логического нуля, а пятом входе — сигнал логической 30 ницы. Так как БУО 9 находится в бочем состоянии, то он формирует гнал на восьмом выходе, которым отывается коммутатор 32 и информация выхода регистра 6 через открытый ммутатор 32 поступает на выход тройства.

Если БУО 9 имеет на втором входе гнал логического нуля, а на третьем четвертом входах — сигналы логичес- 40 и единицы, то на выходе БУО 9 форрует сигналы управления аналогичкак для случая, когда БУО 9 нахотся в начальном состоянии,так и я случая, когда БУО 9 находится 4 конечном состоянии.

Если на четвертом ьходе БУО 9 — сигл логического нуля, на втором и треем входах — си гналы с о о т вет ст н енIf ) tl И ° II tl с и t1nll !10It

"1", то формируется на восьмом выде БУО 9 управляющий сигнал логиской единицы и информация с выхода гистра 6 через открытый коммутатор поступает на выход 33 устройства у итуация, когда МО,а=О, a" P), Если на втором и третьем входах

О 9 - сигнал логического нуля и

О 9 нахопится в. начальном состоянии, то на седьмом выходе формируется сигнал логической единицы, и тогда на выходе элемента ИЛИ 25 сигнал логической единицы, информация запоминается в регистре 6. Затем БУО 9 на восьмом выходе формирует сигнал логической единицы и информация с выхода регистра 6 через открытый коммутатор 32 поступает на выход 33 уст-» ройства (случай, когда а - любое, k=o, а =1), к

В качестве умножителя можно использовать матричный умножитель, реализующий метод ускоренного .умножения второго порядка, Формула и зобр вт ения

Устройство для возведения в степень.п-разрядных двоичных чисел, содержащее первый kn-разрядный регистр (где k — показатель степени, целое число), элементы ИЛИ, коммутаторы, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены р-разрядный регистр р=

=11о8 К(, kn/2-разрядный умножитель, kn/2-разрядный и второй kn-разрядный регистры, блок управления операцией, причем информационный вход р-разрядного регистра и первый информационный вход первого коммутатора соединены с входами показателя и основания степени устройства соответственно, выходы первого разряда непосредственно, а с второго по р-й через первый элемент

ИЛИ соединены соответственно с первым и вторым входами формирования сигнала записи блока управления операцией, третий вход формирования сигнала записи и вход установки начального состояния которого подключены к выходам соответственно второго и третьего элементов ИЛИ, информационный и управляющий выходы первого коммутатора соединены с одноименными входами kn/2-разрядного регистра, выходы которого,на.чиная с второго, соединены с входами второго элемента ИЛИ, а выходы с первого по kn/2 разрядов подключены к первым информационным входам второго и третьего коммутаторов и к первому входу kn/2-разрядного умножителя, второй вход и выход которого соединены с выходами третьего комутатора и второго kn-разрядного регистра соответственно, выход. †..оследнего из которых подключен к вторым информационным

1608654 входам первого и второго коммутаторов, управляющий вход устройства соединен с входом разрешения записи р-разрядного регистра, входом обнуления первого kn-разрядного регистра и с первым управляющим входом первого коммутатора, второй управляющий вход которого соединен с первым выходом блока управления операцией, второй выход которого подключен к первому входу четвертого элемента ИЛИ и первому управляющему входу второго коммутатора, выход первого разряда которого подключен к первому входу пятого 15 элемента ИЛИ, выход которого соединен с входом первого разряда первого

kn-разрядного регистра, входы разрядов которого, начиная с второго, подключены к выходам, начиная с второго д> разряда второго коммутатора, выход первого kn-разрядного регистра соединен с информационным входом четвертьго коммутатора, вторым информационным входом третьего коммутатора и с входами третьего элемента ИЛИ, третий и четвертый выходы блока управления операцией соединены с первым и вторым управляющими входами третьего коммутатора, второй управляющий вход второго коммутатора и второй вход четвертого элемента ИЛИ подключены к пятому выходу блока управления операцией, шестой, седьмой, восьмой и девятый выходы которого соединены соответственно с входом разрешения записи второго kn-разрядного регистра, вторым входом пятого элемента ИЛИ, управляющим входом четвертого коммутатора и входом управления сдвигом р-разрядного регистра, выход четвертого элемента ИЛИ подключен к входу разрешения записи первого kn-разрядного регистра, выход четвертого коммутатора является выходом устройства. Р 3

)608654

1608654

1608654

Составитель С,Макареня

Редактор А,Шандор Техред. М;Ходаиич Корректор Л. Бескид . аказ 3617. Тираж 565 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101