Устройство для контроля цифровых объектов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматизированным системам контроля и может быть использовано при контроле больших и сверхбольших интегральных схем на МОП-структурах. Цель изобретения - расширение функциональных возможностей путем обеспечения контроля объектов с произвольным временем выполнения операции. Устройство содержит генератор тактовых импульсов, управляющий вычислительный блок, группу элементов, блок памяти тестов, счетчик адреса памяти, регистр адреса тестовой комбинации, схему сравнения, регистр выходной тестовой комбинации, многоканальный амплитудный дискриминатор, счетчик числа повторения тестов комбинации, два элемента ЗИ, три элемента И, элемент НЕ, элемент ИЛИ, формирователь импульса, триггер. Принцип действия устройства состоит в блокировке синхроимпульсов, поступающих на вход синхронизации объекта контроля в тот момент, когда его состояние достигает значения, записанного в регистре выходной тестовой комбинации. Объект считается годным, если он достигает заданного состояния за время, меньшее указанного в счетчике числа повторений тестовых комбинаций. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

/ ф

»»: щ)5 G 06 F 15/46

ГОС

ПО

ПРИ

ДАРСТВЕННЫЙ КОМИТЕТ

ЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ГКНТ СССР

ИСАНИЕ ИЗОБРЕТЕНИЯ

ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

;(21) (22) (46) (72) и М. (53) (56)

1I- 711

А

Р.37 (54)

ВЫХ (57) тизи жет боль схем рете возм роля нем

I зиро быть инте ших стру

Ц, функ обес изво ции.

Н ная с!

4603823/24-24

01.08.88

23.11.90. Вюл. Р 43

Т.И.Лемьянчук, В.И»Чашечников

° Михавчук

621.396 (088.8)

Авторское свидетельство СССР

543, кл. С 05 В 23/02, 1978. торское свидетельство СССР

738, кл. G 05 В 23/02, 1970.

УСТРОЙСТВО ДПЯ КОНТРОЛЯ ЦИФРОВЪЕКТОВ

Изобретение относится к автомаованным системам контроля и моыть использовано при контроле х и сверхбольших интегральных на MOII-структурах. Цель изобия — расширение функциональных жностей путем обеспечения контобъектов с произвольным времеыполнения операции. Устройство

» обретение относится к автоматианным системам контроля и может применено при контроле больших " ральных схем (ВИС) и сверхбольнтегральных схем (СВИС) на ИОПтурах. ь изобретения — расширение ональных возможностей путем ечения контроля. объектов с проьным временем выполнения опера-. чертеже приведена функциональ ема устройства.

„„SU „„1608697

2 содержит генератор тактовых импульсов, управляющий вычислительный блок, группу элементов, блок памяти тестов, счетчик адреса памяти, регистр адреса тестовой комбинации, схему сравнения, регистр выходной тестовой комбинации, многоканальный амплитудный дискриминатор, счетчик числа повторения тестов комбинации, два элемента 3 И, три элемента И, элемент НЕ, элемент ИЛИ, формирователь импульса, триггер. Принцип действия устройства. состоит в блокировке синхроимпульсов, поступающих на вход синхронизации объекта контроля в тот момент, когда его состояние достигает значения, записанного в регистре выходной тестовой комбинации. Объект считается годным, если он достигает заданного состояния за время, меньшее указанного в счетчике числа повторений тестовых комбинаций. 1 ил.

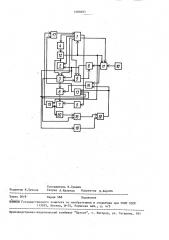

Устройство содержит управляющий вычислительный блок 1, счетчик 2 адреса памяти, блок 3 памяти тестов, регистр 4 адреса тестовой комбинации, регистр 5 выходной тестовой комбина ции, контролируемый объект 6, многоканальный амплитудный дискриминатор

7, счетчик 8 числа повторения тестовых и .комбинаций, группу 9 элементов ЗИ, генератор 10 тактовой частоты, первый элемент ЗИ 11, схему 12 сравнения, второй элемент ЗИ 13, три элемента И

14-16, элемент ИЛИ 17, формирователь

1608697 18 импульса, триггер 19 и элемент

НЕ 20.

Устройство работает следующим образом. 5

В исходное состояние устройство устанавливается сигналом "Сброс" (не показан), при этом в исходное состояние устанавливаются счетчики 2 и 8, триггер 19 и управляющий вычислитель- 10 ный блок 1.

Управляющий вычислительный блок 1 по команде "Пуск" передает в счетчик

2 адреса памяти начальный адрес ячейки блока 3, в которой хранится первая 15 тестовая комбинация для контролируемого типа объекта 6. В регистр 4 адреса тестовой комбинации записывается адрес тестовой комбинации,.на которой требуется зафиксировать выходные сигналы контролируемого объекта 6.

В регистр 5 выходной тестовой комбинации из запоминающего устройства выходных тестовых комбинаций, входящего в состав управляющего вычисли- 25 тельного блока 1, поступает выходная тестовая комбинация, соответствующая выходным сигналам контролируемого объекта 6 на указанном в регистре .4 адреса контролируемой тестовой ком- 30 бинации номере комбинации. Регистр 5 выходной тестовой комбинации соединен с многоканальным амплитудным дискриминатором 7 для задания порога каждого канала дискриминатора.

Па блок 3 из управляющего вычис35 лительного блока 1 поступает импульс запроса. В каждой ячейке блока 3 выделены: один ряд разрядов, в котором записыВяется числО циклОВ генерятОРя 40

10, в течение которых на проверяемую схему должна поступать данная тестовая комбинация входных воздействий; дополнительный разряд, в котором записывается сигнал РазРешения для вклю-45 чения режима автоматической синхронизации работы контролируемого объекza б с системой контроля.

При считывании ячейки блока 3 на входы контролируемого объекта 6 подаются заданные входные воздействия, а число циклов, в течение которых данные воздействия должны подаваться на контролируемый объект, переписываются в обратном коде в счетчик 8 числа повторения тестовых комбинаций через группу 9 элементов ЗИ. На счетный вход счетчика 8 подаются импульсы с генератора 10 через элемент ЗИ 11. При заполнении счетчика

8 наращивается на "1" счетчик 2 и через формирователь 18 импульса по заднему фронту импульса устанавливается в исходное состояние триггер 19.

При этом запрашивается блок 3 по следующему адресу и открывается элемент

И для записи в счетчик 8 следующей тестовой комбинации. На требуемом номере цикла (при равенстве адресов в счетчике 2 и регистре 4) схема 12 г сравнения запрещает прохождение тактовых импульсов на счетчик 8, закрывая элемент ЗИ 11, и подает стробирующий импульс на элемент И 15, разрешая поступление сигнала неисправности

) контролируемого объекта 6 на управляющий вычислительный блок 1 с выхода многоканального амплитудного дискриминатора 7.

При необходимости исследований выходных сигналов следующей тестовой комбинации указанный цикл повторяется. Если контролируемый объект 6 является объектом с произвольным временем выполнения операции, то в дополнительный разряд необходимой ячейки блока 3 записывается сигнал разрешения автоматической синхронизации высокого логического уровня. При считывании данной ячейки блока 3 на входы контролируемого объекта 6 подаются заданные входные воздействия, а максимальное число циклов (максимальное необходимое количество тактовых импульсов генератора 10, поступающее на вход объекта 6 для установки объекта в исходное состояние) переписывается в обратном коде в счетчик

8 числа повторения тестовых комбинаций через группу 9 элементов ЗИ.

На счетный вход счетчика 8 подаются импульсы с генератора 10 через элемент ЗИ 11. Кроме того, эти импульсы через элемент И 14 поступают на второй вход контролируемого объекта 6, При совпадении выходной тестовой комбинации объекта 6 с записанной исходной тестовой комбинацией в регистре 5 с выхода многоканального амплитудного дискриминатора 7 через элемент НЕ 20 и элемент И 16 на триг- гер 19 поступает сигнал, изменяющий по переднему фронту его состояние.

При этом сигналом низкого уровня с выхода триггера 19 запрещается поступление импульсов генератора 10 на синхровход контролируемого объекч п т

5 16

6, так как последний выполнил данную операцию, При заполнении етчика 8 наращивается на "1" счетк 2 и через формирователь 18 имльса триггер 19 устанавливается в ходное состояние.

Если при заполнении счетчика 8 иггер 19 не изменил своего состояя (т.е., находится в исходном сосянии), то сигнал с выхода счетчика через элемент ЗИ 13 и элемент И1П: поступает на вход управляющего числительного блока 1, сигнализия о неисправности в контролируемом ъекте 6. п вь п д э т ц с б

Д д к

P д в п ормула из обретения

Устройство для контроля цифровых ъектов, содержащее управляющий выслительный блок, счетчик адреса мяти, блок памяти тестов, регистр реса тестовой комбинации, регистр ходной тестовой комбинации, многональный амплитудный дискриминатор, етчик числа повторения тестовых мбинаций, первый элемент ЗИ, групэлементов ЗИ, генератор тактовой стоты и схему сравнения, первый, орой входы и выход которой соедины соответственно с выходом рестра адреса тестовой комбинации, ходом счетчика адреса памяти, соененными с первым входом первого емента ЗИ, первым входом прерывая управляюцего вычислительного блопервый, второй и третий инфорционные выходы которого соединены информационными входами регистра реса тестовой комбинации, счетчика реса памяти, регистра выходной тесвой комбинации, первый,. второй и етий управляющие выходы управляюго вычислительного блока соединены ответственно с первым входом выра блока памяти тестов, первым вхом группы элементов ЗИ, вторым вхом первого элемента ЗИ, третий вход торого соединен с выходом генератотактовой частоты, а выход — с вхом суммирования счетчика числа поорения тестовой комбинации, выход реполнения которого соединен. с одом суммирования счетчика адреса мяти, вторым входом группы элеменв ЗИ, вторым входом выбора блока

08697

45 третьего элемента И, второй вход которого соединен с вторым входом вто50

5

35 памяти тестов, первая информационная группа выходов которого соединена . с третьими входами группы элементов

ЗИ, вторая информационная группа выходов является выходом устройства, подключенного к информационным входам контролируемого объекта, адресный вход блока памяти тестов соединен с выходом счетчика адреса памяти, информационный вход счетчика числа повторения тестовой комбинации соединен с выходами группы элементов ЗИ, первая и вторая группы входов амплитудного дискриминатора соединены соответственно с входами устройства, к которым подключены .выходы контролируемого объекта и выходы регистра выходной тестовой комбинации, о тл и ч а ю ц е е с я тем, что, с целью расширения функциональных возможностей путем обеспечения контроля объектов с произвольным временем выполнения операции, в него введены второй элемент ЗИ, первый, второй, третий элементы И, элемент НЕ, формирователь импульса, триггер и элемент ИЛИ, первый, второй входы и выход которого соединены соответственно с выходом второго элемента И, выходом второго элемента ЗИ, вторым входом прерывания управляюцего вычислительного блока, первый и второй входы и выход первого элемента И соединены соответственно с выходом первого элемента ЗИ, первым входом второго элемента ЗИ и выходом триггера, синхровыходом устройства, который подключается к синхровходу контролируемого объекта, первый и второй входы второго элемента И подключены соответственно к выходу схемы сравнения, выходу амплитудного дискриминатора и входу элемента НЕ, выход которого соединен с первым входом рого элемента И и третьим информационным выходом блока памяти, вход формирователя импульса соединен с трегьим входом второго элемента ЗИ и выходом переполнения счетчика числа повторения тестовой комбинации, вход сброса и вход установки триггера соединены соответственно с выходом треть-. его элемента И и выходом формирова теля импульса.

1608697

Составитель В.Гришин

Техред А.Кравчук Корректор Н.Король

Редактор Н.Тупица

Заказ 3619 Тираж 568 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101