Устройство для извлечения квадратного корня из суммы квадратов двух напряжений

Иллюстрации

Показать всеРеферат

Изобретение предназначено для использования в системах преобразовательной техники, аналоговой вычислительной техники, электроприводах постоянного тока и системах автоматики различного назначения. Цель изобретения - повышение точности и расширение области применения путем повышения коэффициента усиления по мощности. В устройстве использован принцип широтно-частотно-импульсной модуляции, которая осуществляется вторым компаратором 12, выдающим импульс включения пятого ключа 20 длительностью Δ &Tgr; = &Tgr;√X<SP POS="POST">2</SP> +Y<SP POS="POST">2</SP>/Y, Y = MAX{/X/,/Y/}, X = MIN {/X/, /Y/ }, где &Tgr; - постоянная времени интеграторов 7, 8, 9. Частотно-импульсная модуляция обеспечивается введением источника 14 опорного напряжения и третьего компаратора 13, моменты срабатывания которого определяют период выходных импульсов T=&Tgr;U<SB POS="POST">оп</SB>/Y, @ U<SB POS="POST">оп</SB> - напряжение источника 14 опорного напряжения. При этом обеспечивается строгое соблюдение требуемой зависимости √X<SP POS="POST">2</SP> + Y<SP POS="POST">2</SP>. Благодаря тому, что пятый ключ 20 подключен к шине постоянного напряжения, достигается большой коэффициент усиления по мощности. Четвертый компаратор 16 и второй сумматор 15 выявляют знак производной сигнала на первом входе второго компаратора 12 и коммутируют выходной сигнал второго компаратора 12 на входы RS-триггера 19, что обеспечивает формирование только одного на периоде дискретизации импульса управления пятым ключом 20, предотвращая его "дребезг". 2 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСтИЧЕСНИХ

РЕСПУБЛИН

А1

С 06 С 7/20 (2 (2 (4 (7 ин (7 (5 (5

l(- 1

У (5

PA д ( и в ч п к

1

) 4642509/24-24

) 26.12.88

) 23.11.90. Бюл. Р 43

) Ленинградский политехнический титут им. M.È.l(àëèíèíà

) М.M.Ерихов

) 681.3(088.8)

) Авторское свидетельство СССР

312618,кл. G 06 Г 7/20, 1986.

Авторское свидетельство СССР

476495, кл. С 06 Г 7/20, 1986.

) YCTP0ACTB0 ДЛЯ ИЗВЛЕЧЕНИЯ KBAjlНОГО КОРНЯ ИЗ CYNMbl KBAPPATOB

НАПРЯЖЕНИЙ

Изобретение предназначено для льзования в системах преобразоельной техники, аналоговой выительной техники, электроприводах оянного тока и системах автоматиазличного назначения. Цель изобния — повышение точности и расине области применения путем пония коэффициента усиления по ости. В устройстве использован цип широтно-частотно-импульсной ляции, которая осуществляется втокомпаратором 12, выдающим импульс

„„SU„„1608703

2 включения пятого ключа 20 длительной л2 х+у стью Д ь ь, у = юах ((х(, I y(3, х,= юза((х (, (у (%, тие ьь постоянная времени интеграторов 8-9.

Частотно-импульсная модуляция обеспечивается введением источника 14 опорного напряжения и третьего компаратора 13, моменты срабатывания которого определяют период выходных импульсов

Т = . О 110„ /у, где U д — напряжение источника 14 опорного напряжения. При, этом обеспечивается строгое соблюдевие требуемой зависимости (хс т уз.

Благодаря тому, что пятый ключ 20 подключен к шине постоянного напряжения, достигается большой коэффициент уси- Е ления по мощности. Четвертый компаратор 16 и второй сумматор 15 выявляют знак производной сигнала на пер- . С вом входе второго компаратора 12 и коммутируют выходной сигнал второго Я компаратора 12 на входы RS-триггера

19, что обеспечивает формирование только одного на периоде дискретизации импульса управления пятым ключом

20, предотвращая его "дребезг". 2 ил.

1608703

Изобретение предназначено для использования в системах преобразовательной, аналоговой вычислительной техники, электроприводах постоянного тока, системах автоматики различного назначения.

Пель изобретения — повышение точности и расширение области применения путем повышения коэффициента усиления по мощности.

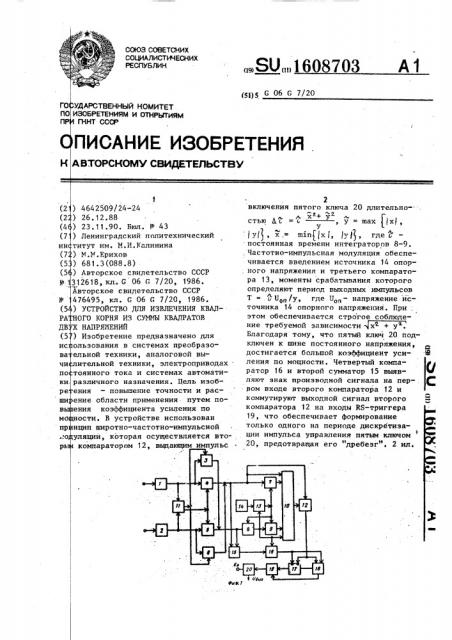

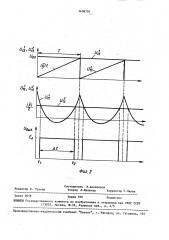

На фиг. 1 представлена функциональная схема устройства, на фиг. 2 временные диаграммы работы устройства. 15

Устройство содержит первый 1 и второй 2 блоки выделения модуля, первый 3, второй 4, третий 5 и четвертый 6 ключи, первый 7, второй 8 и третий 9 интеграторы, первый сумматор 20

10, первый 11, второй 12 и третий 13 компараторы, источник 14 опорного напряжения, второй сумматор 15, четвертый компаратор 16, элемент НЕ-И 17, элемент И 18, RS-триггер 19, пятый 25 ключ 20.

Устройство работает следующим образом, Первый компаратор 11 и ключи 3-6 коммутируют модули входных напряжений 30 таким образом, что на вход первого интегратора 7 поступает наименьшее налэихеиие х = min ((х(, (yf), а иа вход второго интегратора 8 — наибольшее у = иах ((х(, Iyl) Если коэффициенты усиления интеграторов 7-9 выбра.ны равным 1/i, 1/1., 2/ соответственл но (— постоянная времени интеграторов), а коэффициенты усиления по первому и второму входам второго ком- 40 паратора 12 равными 1 и 1/2, то моменты срабатывания t и t второго компаратора 12 определяются квадрат- ным уравнением

L \ х. х у — — (у+х) — + — = 0 лд- " 2 7

2yt/i,

5 первого сумматора 10, выходной сигнал четвертого компаратора 16 имеет уровень логической "1".

Следовательно, при первом на периоде совпадении входных сигналов

U< и Ui второго компаратора 12

I Z в момент времени t< на выходе элемента И 18 появится логическая "1", RS-триггер перейдет в состояние "1" и будет находиться в нем до тех пор, пока знак производной ИП< /dt не изменится (выходной сигнал четвертогс компаратора 16 будет иметь уровень логического "On), при этом компаратор 12 перейдет в состояние логичел. л

Ьс= t -t

Срабатывание третьего компаратора

13 произойдет в момент совпадения интеграла напряжения у с опорным напряжением Uo„= const:

= "Uq/у . откуда длительность выходного импульса устройства составляет

При этом выдается импульс, обнуляющий интеграторы 7-9, длителность которого определяется инерционными свойствами второго интегратора S u третьего компаратора 13.

Таким образом, постоянная составляющая последовательности выходных импульсов устройства ц, „= е,а. !т =E «Я + y /с,„ в точности пропорциональна требуемой функции входных напряжений.

В моменты переключения второго компаратора 12 под действием помех, присутствующих во входных сигналах х и у, а также при малых yrлах пересечения входных сигналов второго компаратора 12 в течение малого промежутка времени может наблюдаться серия многократных переключений компаратора 12. Эти переключения, ввиду их кратковременности, мало сказываются на точности воспроизводимой функциональной зависимости х + у, однако такой

Я. 2. режим работы крайне неблагоприятен для работы пятого ключа 20, поскольку при этом резко ухудшаются его энергетические характеристики. Для исключения явления "дребезга" в устройство вводят второй сумматор 15, четвертый компаратор 16, элементы

НЕ-И 17 и И 18, RS-триггер 19.

Коэффициенты усиления второго сумматора 15 выбираются единичными по обоим входам, коэффициенты усиления четвертого компаратора 16 равны. 1 и 2 по первому и второму входам соответственно. Таким образом, при условии ског да ч

RS-т лени ново обра возм пято личн си,гн

П цион быть ходя во м вход

Ф о

У ратн напр рой, кото.вым ход соед пара перв рого к вт и к и че и ин рато дами того чей, чей комп щим перв сумм

5 16

"0" в момент времени t . Тог-2. рез элемент HF.— И 17 на вход иггера 19 поступит сигнал обнуи RS-триггер 19 перейдет в устойчивое состояние. Таким ом, на периоде дискретизации жны только два переключения о ключа 20, соответствующие раз м точкам t< и t совпадения лов U u U на фиг.2. скольку напряжение на информаом входе пятого ключа 20 может выбрано достаточно большим, вые напряжение устройства будет ого раз превосходить уровень

ых напряжений. мула изобретения тройство для извлечения квадго корня из суммы квадратов двух жений, содержащее первый и втолоки выделения модуля, входы

ых являются соответственно первторым входами устройства, выервого блока выделения модуля нен с первым входом первого комора и с информационными входами

ro и второго ключей, выход втоблока выделения модуля подключен рому входу первого компаратора нформационным входам третьего вертого ключей, неинвертирующий ертирующий выходы первого компаа соединены с управляющими вхосоответственно первого и четверключей и второго и третьего клювыходы второго и четвертого клюоединены с первым входом второго ратора, с первым неинвертируюходом первого сумматора и через и интегратор подключены к перинвертирующему входу первого тора, выходы первого и третьего

08703 6 ключей через последовательно включенные второй и третий интеграторы соединены с вторым неинвертирующим входом первого сумматора, второй инвертирующий вход которого подключен к выходу второго интегратора, вход обнуления которого соединен с входами обнуления первого и третьего интеграторов, выход первого сумматора подключен к второму входу второго компаратора, пятый ключ, выход которого является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности и расширения области применения путем повышения коэффициента усиления по мощности, в него введены второй сумматор третий и четвертый компараторы, эле20 менты И и НЕ-И, RS-триггер и источник опорного напряжения, причем выходы второго и третьего ключей соединены соответственно с первым и вторым входами второго сумматора, выход

25 которого подключен к первому входу четвертого компаратора, второй вход которого соединен с выходом второго интегратора, а выход четвертого компаратора подключен к первым входам элементов И и HF. — И, вторые входы которых соединены с выходом второго компаратора, выходы элементов НЕ-И и И подключены соответственно к R-, и

S-входам RS-триггера, выход которого

35 соединен с управляющим входом пятого ключа, информационный вход которого подключен к шине постоянного напряжения, выход источника опорного напряжения соединен с первым входом треть40 его компаратора, abmoq которого подключен к входу обнуления третьего интегратора, информационный вход которого соединен с вторым входом третьего компаратора.

1608703

1 2 18у Q

Редактор Н. Тупица

Заказ 3619 Тираж 559 Подписное

ВНИИЕИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r, Ужгород, ул. Гагарина, 101

f Я 15 15 ОП

Составитель В.Алекперов

Техред А.Кравчук Корректор С.Черни