Цифрочастотный интегратор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной и информационно-измерительной технике, а именно к системе автоматического управления, и может найти применение в системах числового программного управления, а также в измерительных и вычислительных устройствах. Цель изобретения - повышение достоверности интегрирования. Цифровой интегратор содержит регистр управляющего кода 1, элемент И 2, первый блок 3 формирования последовательности импульсов, первый счетчик 4, второй блок 5 формирования последовательности импульсов, элемент задержки 6, счетчик 7, одновибратор 8 и D-триггер 9. По значению управляющего кода, представленного в минимальной форме, и хранящегося в регистре управляющих кода, блоками 3 и 5 формируются две эквивалентные по числу импульсов за цикл интегрирования последовательности, поступающие соответственно на суммирующий и вычитающий входы счетчика 7. Нулевое состояние второго счетчика 7, фиксируемое по окончании цикла интегрирования триггером 9, указывает о правильности интегрирования. При наличии недопустимых ситуаций в формировании частотно-импульсных последовательностей на выходах 10 и 18 осуществляется установка триггера в единичное состояние. 1 ил.

союз советских социдлистических

РЕСПУБЛИК (19) (11) 4629510/24-24

02.01.89

23.11.90. Бюл, М 43

Специальное конструкторско-техноческое бюро "Модуль" Винницкого технического института .П. Стахов, В.А. Лужецкий,.А.Н. Ромаи Н.В. Николаева

81.3 (088.8) вторское свидетельство СССР

57956, кл. G 06 f 7/64, 1987, анчеев В.П. Цифрочастотные вычислиые устройства. -М,; Энергия, 1976. с. иг.14. тель

24, (21) (22) (46) (71) лог пол (72) нюк (53) (56)

М1 (54) (57) ной нике упра сист ния, тель

ИФРОЧАСТОТНЫЙ ИНТЕГРАТОР зобретение относится к вычислительинформационно-измерительной теха именно к системе автоматического ления, и может найти применение в мах числового программного управлетакже в измерительных и вычислиых устройствах. Цель изобретения— повышение достоверности интегрирования.

Цифровой интегратор содержит регистр 1 управляющего кода, элемент И 2, первый блок 3 формирования последовательности импульсов, первый счетчик 4, второй блок 5 формирования последовательности импульсов, элемент 6 задержки, счетчик 7, одновибратор 8 и D-триггер 9, По значению управляющего кода, представленного в минимальной форме и хранящегося в регистре управляющего кода, блоками 3 и 5 формируются две эквивалентные по числу импульсов за цикл интегрирования последовательности, поступающие соответственно на суммирующий и вычитающий входы счетчика 7.

Нулевое состояние второго счетчика 7, фиксируемое по окончании цикла интегрирования триггером 9,.указывает о правильности интегрирования. При наличии недопустимых ситуаций в формировании частотно-импульсных последовательностей на выходах

10 и t8 осуществляется установка триггера в единичное состояние, 1 ил.

1608708

Изобретение относится к вычислительной и информационно-измерительной технике, а именно к системам автоматического управления, и может найти применение в системах числового программного управления, а также в измерительных и вычислительных устройствах, Целью изобретения является повышение достоверности интегрирования;

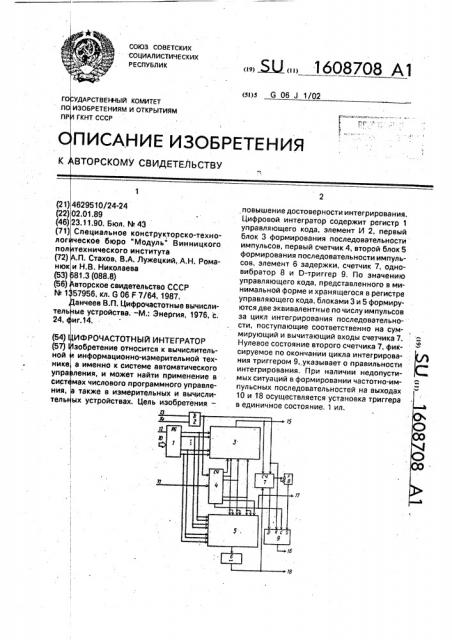

На чертеже представлена структурная схема предлагаемого интегратора, Цифрочастотный интегратор содержит регистр 1 управляющего кода, элемент И 2, первый блок 3 формирования последовательности импульсов, первый счетчик 4, второй блок 5 формирования последовательности импульсов, элемент 6 задержки, второй счетчик 7, одновибратор

8, D-триггер 9, входы 10 — 14, выходы 15 — 18.

В интеграторе разрядность блоков определяется разрядностью и регистра 1 управляющего кода и имеет следующие значения; счетчик 4 — (n+1), блок 3 формирования последовательности импульсов — n; блок 5 формирования последовательности импул ьсов — 2(n-1)+1, Повышение достоверности интегрирования достигается за счет формирования двух эквивалентных по численности за цикл интегрирования последовательности. Отличие от нуля разности этих последовательностей показывает на наличие ошибки.

Интегратор работает следующим образом, По включении питания на входе 13 и при наличии сигнала на входе 14 начальной установки интегратора вырабатывается импульс отрицательной полярности, под воздействием которого счетчики 4 и 7 и 0триггер 9 устанавливаются в состояние логического "0". На вход 10 интегратора от внешнего устройства поступает значение управляющего кода в минимальной форме; которое записывается в регистр 1 при поступлении активного уровня сигнала записи на вход 12.

На вход 11 интегратора поступает опорная импульсная последовательность, под возделствием которой на импульсных выходах счетчика 4 формируются импульсы, числа которых за цикл пересчета счетчика 4 равны весам фибоначчиевой системы счисления. Частотные потоки с выхода первого фибоначчиевого счетчика 4 отбираются блоком 3 и суммируются. Отбор импульсов блоками 3 и 5 производится с различных разрядов первого счетчика 4, при этом формируются две эквивалентные по числу импульсов последовательности.

10 сти с выходов блоков 3 и 5 эквивалентны по

Контроль работы интегратора осуществляется следующим образом.

Импульсы с выхода блока 3 формирования последовательности импульсов поступают на суммирующий вход счетчика 7, а импульсы с выхода блока 5 формирования последовательности импульсов — на вычитающий вход счетчика 7, Поскольку частотные последовательночислу импульсов, то по окончании цикла интегрирования состояние счетчика 7 при правильной работе интегратора должно быть нулевым.

Состояние счетчика 7 по окончании цикла интегрирования фиксируется триггером

9. Для этого вход переполнения счетчика 7 подключен к D-входу триггера 9, а управляющий С-вход триггера 9 — к выходу переполнения счетчика 4 и выходу 17 интегратора.

При правильной работе интегратора по окончании цикла интегрирования на выходе переполнения счетчика 7 появляется уровень логического "0", указывающий на нулевое состояние счетчика 7. Активным уровнем сигнала переполнения счетчика 4, возникающего при окончании цикла интегрирования, значение сигнала переполнения счетчика 7 фиксируется в триггере 9.

Логическая "1" на выходе 16 сигнализирует о неправильной работе интегратора.

Счетчик 7, элемент 6 задержки, одновибратор S, D-триггер 9 образуют узел контроля интегрирования. Элемент 6 задержки предназначен для временного сдвига импульсной последовательности с выхода блока 3. За счет этого обеспечивется последовательное, один за другим поступление кодов с блоков 3 и 5 формирования последовательности импульсов на суммирующий и вычитающий входы счетчика 7 при их одновременной выдаче. Если на счетчик

7 подано различное число импульсов от блоков 3 и 5, одновибратор 8 вырабатывает импульс отрицательной полярности, который устанавливает триггер 9 в единичное состояние, Это сигнализирует о наличли ошибки.

Формула изобретения

Цифрочастотный интегратор, содержа.щий два счетчика и первый блок формирования последовательности импульсов„ выход которого соединен с первым выходом интегратора, о тл ич а ю шийся тем, что, с целью повышения достоверности интегрирования, в него дополнительно введены регистр управляющего кода, элемент И, второй блок формирования последовательности импульсов, одновибратор, элемент

1608708

Составитель А; Тимофеев чар

ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат. "Патент", г, Ужгород, ул,Гагарина, 101 зад кл сче вы кон

0-т да до кот ми зап не ля кол кот гру

21вхо ров вы ниг го ржки и О-триггер, 0-вход которого подчен к выходу переполнения второго чика, а С-вход D-триггера подключен к оду переноса первого счетчика и выходу ца интегрирования интегратора, R-вход 5 иггера соединен с установочными вхои первого и второго счетчиков и с выхоэлемента И; первый и второй входы рого являются первым и вторым входаачальной установки интегратора, вход 10 си управляющего кода которого соедис управляющим входом регистра управщего кода, выход I-ro (i = 1...n, где и— чество разрядов входного кода разряда рого соединен с 1-м разрядом первой 15 пы входов первого логического блока и и (2i-1)-м разрядами, кроме последнего, ов первой группы второго блока форминия последовательности, импульсов, а д разряда регистра соединен с послед- 20 разрядом первой группы входов второлока формирования последовательности импульсов, входы (2Н)-го и 2l-ro разрядов -: второй группы входов которого, кроме п-го, соединены с!+1 выходами первого счетчика, i-й выход которого, кроме п-го, соединен с

I-м входом второй группы входов первого блока формирования последовательности импульсов, выход которого соединен с суммирующим входом второго счетчика, вычитающий вход которого соединен с вторым выходом интегратора и выходом элемента задержки, вход которого соединен с выходом второго блока формирования последовательности импульсов, S-вход 0-триггера соединен с выходом одновибратора, вход которого соединен с выходом второго счетчика, счетный вход первого счетчика соединен с входом синхронизации устройства, а вход записи регистра управляющего кода— с информаионным входом интегратора, вход и-го разряда второй группы входов второго логического блока соединен с выходом n-ro разряда первого счетчика.