Устройство для вывода графической информации

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано для вывода графической информации из ЭВМ. Цель изобретения - повышение быстродействия устройства. Цель достигается введением коммутатора 19, формирователя 20 адреса, второго 21 и третьего 22 регистров адреса, третьего 23 и четвертого 24 сумматоров и соответствующих функциональных связей. Изобретение позволяет перемещать фрагменты изображения на экране телевизионного приемника. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН ((9) (II),SU (S1)5 С 09 С 1/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ FIGHT СССР

Н A ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ (21) 4645310/24-24 (22) 29. 11.88 (46) 07, 12.90. Бюл. К - 45 (71) Московский инженерно-физический институт (72) Î,Н. Цапко и В,Б. Шувалов (53) 68 1.327,11(088.8) (56) Авторское свидетельство СССР

N - 824285, кл. С 09 С 1/16, 1979.

Авторское свидетельство СССР

Р 1078450, кл, G 09 С- 1/16, 1982.

2 (54) УСТРОЙСТВО ДЛЯ ВЫВОДА ГРАФИЧЕСКОЙ ИНФОРМАЦИИ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано для вывода графической информации из ЭВМ. Цель изобретения — повышение быстродействия устройства, Цель достигается введением коммутатора 19, формирователя ?О адреса, второго 21 и третьегп 22 регистров адреса, третьего

23 и четвертого 24 сумматоров и соответствующих функциональных связей, Изобретение позволяет перемещать фрагменты изображения на экране телевизионного приемника. 2 ил, 1612323

Изобретение относится к автоматике и вычислительной технике и может быть использовано для вывода графической информации из ЭВМ.

Пель изобретения — повышение быстродействия устройства.

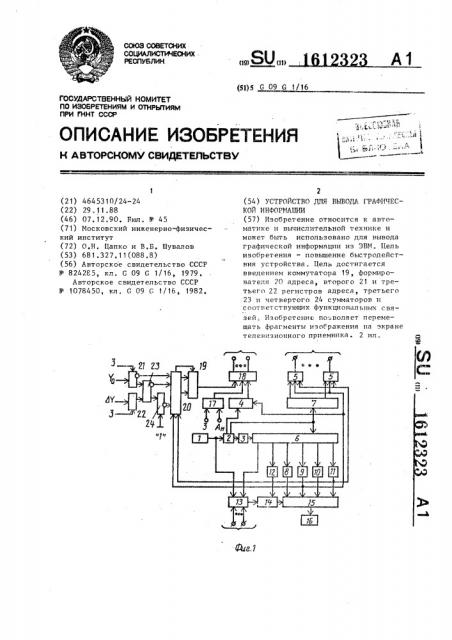

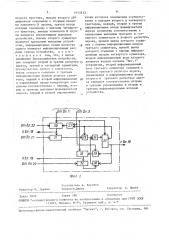

На фиг. 1 представлена структурная схема устройства; на фиг. 2—, структурная схема формирователя ад-.реса.

Устройство содержит генератор 1 тактовых импульсов, счетчик точек

2, строк 3 и адреса 4, элементы И 5

: группы,l первый 6 и второй 7 дешифраторы, первый 8, второй 9, третий

,10, четвертый 11 и пятый 12 триггеры, регистр 13 сдвига, элемент И 14, первый сумматор 15,. телевизионный индикатор 16, первый регистр 17 ад- 20 реса, второй. сумматор 18, коммутатор

19, формирователь 20 адреса, второй

21 и третий 22 регистры адреса, третий 23 и четвертый 24 сумматоры.

Формирователь 20 адреса содержит 25 счетчики 25 и 26, элементы И 27-30, блоки 31 и 32 сравнения, триггер 33 и элемент ИЛИ 34.

Устройство работает следующим образом. 30

Генератор тактовых импульсов формирует импульсы высокой частоты, соответствующие требуемой дискретизации растра экрана по горизонтали, которые поступают на вход счетчика 2 точек и на тактовый вход регистра 13 сдвига, осуществляя сдвиг содержащейся в нем информации, которая заносится из памяти ЭВМ, Емкость регистра 13 сдвига равна разрядности слова памя- „0 ти 3ВМ. Коэффициент пересчета счетчика 2 точек соответствует телевизионному стандарту длительности строчной развертки. Сигнал с первого выхода (старшего разряда) счетчика 2 точек поступает на вход счетчика 3 строк, который осуществляет пересчет строк в кадре и имеет период пересчета„ равный длительности кадровой раз. вертки.

Сигналы с выходов счетчиков 2 и 3 поступают на входы дешифраторов 6 и 7.

Первый дешифратор формирует управляющие сигналы записи слова информации в регистр 13 сдвига пере55 броса пятого триггера 12, который разрешает прохождение видеосигнала с регистра 13 сдвига через элемент

И 14 во время видимого хода луча кадровой и строчной разверток: строчный синхроимпульс формируется первым триггером 8, строчный гасящий импульс формируется вторым триггером 9, кадровый синхроимпульс формируется третьим триггером 10, кадровый гасящий импульс формируется четвертым триггером 11.

Полученные таким образом компоненты телевизионной сийхросмеси совместно с видеосигналом, поступающим с выхода пер вог о элемента И 14, пр еобразуются сумматором 15 в стандартный телевизионный видеосигнал, ко торый поступает на видеовход телевизионного индикатора 16. Сигналы с выхода второго 7 дешифраторз поступают на элементы И 5, на которых совместно с сигналами с выходов второго 9 и четвертого 11 триггеров формируются сигналы запроса следующего слова из 3ВМ причем запрос следующего слова памяти совмещен во времени со сдвигом предыдущего слова в регистре 13.

Размер изображения на экране составляет 2 слов по горизонтали и

YYl

2 строк по вертикали. Каждая точка на экране кодируется одним битом в памяти ЭВМ, а разрядность слова

21 бит, Адрес А > считываемого слова, формируемый устройством на выходах второй группы, определяется по формуле

А ц АН AX+ AgY где А „ц„— начальный адрес массива от ображ ения, з ада ва емый из ЭВМ, в регистр 17 ад-. реса;

А — адрес слова в строке

X изображения, формир у емый счетчиком 4 адреса;

А — текущий адрес строки изображения, Поле координат экрана имеет начачо координат в нижнем левом углу экрана. Развертка изображения на экране осуществляется слева направо, начиная с верхнего левого угла.

Адрес Ау определяется кодом счетчика 4 адреса, который устанавливается в "0" строчным гасящим импульсом и пересчитывает импульсы с периодом цикла смены адресов памяти, посту5

161 лающие с третьего выхода счетчика 2 точек на видимом ходе строки.

Составляющая адреса А формируется следующим образом, В режиме перемещения фрагмента изображения вниз из ЭВМ в регистр 21 заносится координата Y границы сме"

О. щения, а в регистр 22 - код gY величины смещения, На инверсном выходе сумматора 23 формируется значение Yp + $Y а на инверсном выходе сумматора 24значение Yp + g Y + 1.

По кадровому гасящему сигналу в счетчик 25 заносится код Y + ДУ с инверсного выхода сумматора 23 и сбрасывается в "0" триггер 33 и счетчик 26. Инверсный выход триггера

33 разрешает работу элементов И 2? и 28, а прямой выход триггера 33 запрещает работу элементов И 29 и 30. Сигналы видимого хода строки с выхода триггера 9 через элемент

И 27 поступают на счетный вход счетчика 25, который работает по заднему фронту тактового импульса, Таким образом, верхняя сторона на экране —. это строка с А = Y + ДУ.

Блок. 31 сравнения с. pàBíèBàåò выходной код счетчика 25 с кодом

Y и, когда эти коды сравниваются, о формирует сигнал, который, проходя через элементы И 28 и ИЛИ 34, задним фронтом перебрасывает по тактовому входу триггер 33 в единичное состояние, При этом последней строчкой в первом фрагменте является строка с А ч = Т, Единичное состояние триггера 33 на его прямом выходе переключает коммутатор 19 так, что к входу сумматора 18 подключается выход счетчика 26, установленного в этот момент в "0", в силу чего первой строкой второго фрагмента (фиг.3) является строка с A = О.

Сигнал видимого хода строки, проходя через элемент И 29, увеличивает состояние счетчика 26, Элемент 32 сравнения сравнивает код счетчика 26 с кодом Yp + $ Y + 1 и при сравнении вырабатывает сигнал, который задним фронтом перебрасывает триггер 33 слова в нулевое состояние, Тем самым к входу сумматора 18 снова подключается выход счетчика ."5, Таким образом,.последняя строка второго Фрагмента (фиг. 3) имеет А ч = Y + QY + 1, а первая строка третьего фрагмента адрес А =

2323

= Y " 1, Далее счетчик.2 считает- до

N конца кадра, т, е, до кода (2 — ) .

Предлагаемое изображение обеспечивает повышение быстродействия устройства, так как стирание и перезапись всех точек иэображения, находящихся в перемещаемых участках, заменяется занесением информации в регистры 21 и 22.

Формула изобретения

Устройство для вывода графической информации, содержащее счетчик точек, счетчик строк, счетчик адреса, первый сумматор, первый регистр адреса, регистр сдвига, элемент И, группу элементов И, пе"вый и второй дешифраторы, с первого по пятый триггеры, второй сумматор и генератор тактовых импульсов, выход которого соединен с тактовыми входами регистра сдвига и счетчика точек, первый выход которого соединен с TRKTQHbtM входом счетчика строк, выход которого соединен с первым информационным входом пер— вого дешиФратора, с первого по пятый выходы которого соединены с информационными входами соответственно с первого ио пятый триггеров, выходы с первого по четвертый триггеров соединены с информационными входами группы первого сумматора, выход пятого триггера соединен с первым входом элемента И, выход которого соединен с информационным входом первого сумматора, выход которого подключен к видеовходу телевизионного приемника. второй вход элемента И соединен с выходом регистра сдвига. управляюший вход которого соединен с шестым выходом первого дешнфратора, второй информационный вход которого, соединенный с информационным входом второго дешифратора, подключен к второму выходу счетчика точе;;, третий выход которого соединен с тактовым входом счетчика адреса, выход которого соединен с первым информа- . ционным входом второго сумматора, второй информационный вход которого соединен с выходом первого регистра адреса, управляющий и информационный входы которого являются периымн управляющими и информацнонньли входами устройства, вход сброса счетчика адреса, соединенный с первыми входами элементов И группы, подключен к выходу

7, 1б12323

Составитель А, Коробов

Т ехр ед М, Дидьпс

Корректор О. Пипле

Редактор И„ щербак

Заказ 3832 Тираж . 88 Подписноp

ИПЯПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113Î35, Москва, Ж-35, Раушская наб., д, 4/5

1f,tl

Производственно-издательский комбинат Патент, г ° Ужгород, ул„ Гагарина, 101 второго триггера, выходы второго дешифратора соединены с вторыми входами элементов И группы, третьи входы которых соединены с выходом четверто, го триггера, выходы элементов И группы являются управляющими выходами устройства, выходы второго сумматора являются адресными выходами устройства, информационные входы регистра сдвига являются информационными входами группы устройства, о т л и— ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства„ оно содержит второй и третий регистры адреса, третий и четвертый сумматоры, формирователь адреса и коммутатор, выход которого соединен с третьим информационным входом второго сумматора, первый и второй информационные и управляющий входы коммутатора соединены соответственно с первым, вторым и третьим выходами формирователя адреса, первый и второй управляющие входы которого подключены соответственно к выходам второго и четвертого триггеров, первый, второй и третий информационные входы формирователя адреса соединены соответственно с инверсными выходами третьего и етвертого сумматоров и второго регистра, адреса, прямой выход которого соединен с первым информационным входом третьего сумматора, прямой выход которого соединен с первым информационным входом четвертого сумматора, второй информационный вход которого является входом сигнала "Лог,1" устройства, второй информационный вход третьего сумматора соединен с выходом третьего регистра ацреса, управляющие и информационные входы второго и третьего регистров адреса являются соответственно вторым и Ipåòüèì управляющими и вторым и третьим информационными входами устройства,