Способ динамического выравнивания токов параллельно включенных биполярных транзисторов

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике, в частности к преобразовательной технике, и может найти применение в регуляторах электрической мощности. Целью изобретения является динамическое выравнивание токов параллельно включенных биполярных транзисторов при их включении и выключении. Последовательно с каждым из параллельно включенных биполярных транзисторов включен токоограничивающий элемент. На интервалах включения-выключения измеряют разность потенциалов между точками соединения каждого из биполярных транзисторов с соответствующим токоограничивающим элементом. В зависимости от знака полученной разности при включении подают запирающий сигнал на коллекторный переход опережающего биполярного транзистора. При выключении запирающий сигнал подают на коллекторные переходы отстающих биполярных транзисторов. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (si)s G 05 F 1/56, 1 /59

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4605680/24-07 (22) 15.11,88 (46) 15.12,90, Бюл. N. 46 (71) Филиал Всесоюзного научно-исследовательского института электромеханики (72) С.Н.Болдырев и В.В.Талов. (53) 621.316.722.1 (088.8) (56) Электротехника, 1986, М 2, с, 25 — 27.

Источники вторичного электропитания.

Под ред. Ю.И.Конева. М.: Радио и связь, 1983, с. 103 — 104. (54) СПОСОБ ДИНАМИЧЕСКОГО ВЫРАВНИВАНИЯ ТОКОВ ПАРАЛЛЕЛЬНО ВКЛК3ЧЕННЫХ БИПОЛЯРНЫХ ТРАНЗИСТОРОВ (57) Изобретение относится к электротехнике, в частности к преобразовательной технике, и может найти применение в регуляторах электрической мощности, Изобретение относится к электротехнике и может быть использовано при разработке преобразовательных комплексов большой мощности.

Целью изобретения является повышение надежности путем динамического выравнивания токов параллельно включенных биполярных транзисторов при их включении и выключении.

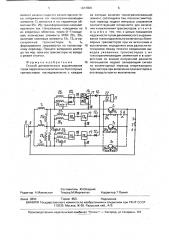

На чертеже приведен пример схемы устройства, реализующего данный способ, Способ динамйческого выравнивания токов параллельно включенных биполярных транзисторов, последовательно с каждым из которых включен токоограничивающий элемент, состоит в том, что попарно определяют знак разности потенциалов между точками соединения силового вывода каждого из биполярных транзисторов и токоограничивающего элемента и подают запирающий,, Ы,, 1614009 Al

Целью изобретения является динамическое выравнивание токов параллельно включенных биполярных транзисторов при их включении и выключении. Последовательно с каждым из параллельно включенных биполярных транзисторов включен токоограничивающий элемент. На интервалах включения — выключения измеряют разность потенциалов между точками соединения каждого из биполярных транзисторов с соответствующим токоограничивающим элементом. В зависимости от знака полученной разности при включении подают запирающий сигнал на коллекторный переход опережающего биполярного транзистора. При выключении запирающий сигнал подают на коллекторные переходы отстающих биполярных транзисторов. 1 ил. сигнал на коллекторный переход опережающего транзистора при включении и отстающего транзистора при выключении.

Устройство для реализации способа выравнивания токов параллельно включенных биполярных транзисторов содержит п параллельно включенных биполярных транзисторов 1i — 1п, блок 2 подключения нагрузки с двумя выводами 3, 4, цепь управления с двумя выводами 5, 6, и токоограничивающих элементов, например дросселей или резисторов, 7i — 7л, блок подключения первого источника 8 питания постоянного тока с двумя клеммами 9, 10, и базовых резисторов 11>—

11п, п развязывающих диодов 121 — 12,, п управляемых ключевых элементов 13> — 13 (например, на транзисторе 14 с базовым резистором 15 и резистором 16 смещения), каждый из которых имеет два выходных вывода

17. 18 и один входной вывод 19, n (n — 1)-вхо1614009 довых логических элементов ИЛИ 20} — 20„, блок подключения второго источника 21 пл тания постоянного тока с двумя клеммами

22, 23, и ограничительных резис1 ров 24}—

n(n — 11

24„и трансформаторов, каждый из которых имеет одну первичную обмотку 25 и две вторичные обмотки 26 и 27 соответственно, причем эмиттеры транзисторов 1} — 1л подключены к одному выводу 3 блока 2 подключения нагрузки 2 и одному входу 6 цепи .,управления, а коллектор каждого силового транзистора 1 > — 1л через соответствуюв;ий токоограничивающий элемент 71 — 7„подключен к одной клемме 9 блока подключения первого источника 8 питания постоянного тока, вторая клемма 10 которо l o соединена с другим выводом 4 блока 2 подключения нагрузки, база каждого транзистора через базовый резистор 111 — 11„ соединена с другим входом 5 цепи управле- ,ния, параллельно эмиттерному переходу транзистора 14 ключевых элементов 131—

13> включен резистор 16 смещения, а база через базовый резистор 15 соединена с входным выводом 19, один выход каждого

КЛЮЧЕВОГО ЭЛЕМЕНта 131 — 13л ПадКЛЮЧЕН К ,первому выводу соответствующего развя зывающего диода 12} — 12,, а второй выход

,ключевых элементов 13} — 13n соединен с коллектором соответствующего биполярного транзистора 1> — 1л, входной вывод 19 каждого из которых соединен с выходом соответствующего (и-1)-входового логического элемента ИЛИ 201 — 20n, первичные обмотки трансформаторов 251. — 25 "& )

? включены между коллекторами каждых двух из биполярных транзисторов 11 — 1л, а каждая из вторичных обмоток 261 — 26 и (и 1), 2

27i — 27 1 >- между одним иа входов

2 одного иэ логических элементов ИЛИ 201—

20п и вторым выходом соответствующего ему управляемого ключевого элемента 1 3}в

13П, причем начало первичной обмотки 251—

25 " тв1} соответственно хаждого трансг форматора соединено с началом первой вторичной обмотки 26} — 26 "(" "3 этого

2 трансформатора, а конец первичной обмотки 251 — 25 Яп ) — с концом второй

2 вторичной обмотки 271 — 27 и (л-1 ), одна

2 клемма 22 блока подключения второго источника 21 питания подключена к второму выводу каждого из развязывающих диодов

12> 12>, а другая клемма 23 через каждый

55 ограничительный резистор 24} 24 ° к базе каждого биполярного тг}анзистора 1} - 1л, Устройство для реализации способа динамического выравнивания 10К00 параллельно включенных биполярных транзисторов работает следующим образом.

В исходном состоянии, т.е. при подключенных источниках 8 и 21 питания к блокам, ключевые элементы 131-- 13п и биполярные транзисторы 1} — 1„находятся в закрытом состоянии.

При поступлении отпирающего управляющего импульса на эмиттерные переходы биполярные транзисторы 11 — 1n открываются, и если насыщение транзисторов проходит одинаково, увеличение их коллекторныx токов происходит равномерно. Если же насыщение транзисторов в процессе включения проходит неодинаково, например транзистор 1} открывается быстрее, чем транзисторы 12 1ть то потенциал его коллектора сгановится ниже, чем потенциал коллекторов транзисторов 12 — 1„, и при этом по первичным обмот кам 251, 25п трансформаторов начинает протекать ток. а напряжение, наводимое во вторичных обмотках

26} — 26 n (и -12,271 —. 27 n (n I) через

2 2 (и-1)-входовые логические элементы ИЛИ

201 — 20П поступает на входы 191 — 19П управления ключевых элементов 13} — 13,. В данном случае открывается ключевой элемент 131 и по цепи клемма 22 блока подключен и я источни ка 21 питания развязывающий диод121 — ключевой элемент

131 — коллекторный переход транзистора 1t — ограничительный резистор 24} — клемма

23 источника 21 питания протекает ток, который призакрывает биполярный транзистор 11, напряжение íà его коллекторе повышается, а коллекторные токи транзисторов 1} — 1, выравниваются. Если после этого разбаланс токов повторяется, то аналогично происходит ограничение коллекторного тока B любом из транзисторов, включение которого происходит быстрее, чем у остальных, Процесс выравнивания коллекторных токов при включении длится до тех пор, пока все транзисторы не войдут в режим насыщения. Выравнивание токов в статическом режиме происходит за счет деления суммарного входного тока токоограничивающими элементами 71 — 7П.

При поступлении на эмиттерные переходы транзисторов 11 — 1П запирающего импульса управления начинается процесс их выключения, Так как частотные свойства транзисторов различны. то первым в активную область входит самый быстродействующий транзистор. например 12. При эгом в

1614009

Формула изобретения

Способ динамического выравнивания токов параллельно включенных биполярных транзисторов, последовательно с каждым 17 @ г01

Составитель Ю.Опадчий

Техред M.Ìîðãåíòàë Корректор Т.Палий

Редактор А.Маковская

Заказ 3893 Тираж 653. Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 момент начала спада его коллекторного тока напряжение на токоограничивающем элементе 7z меняется и по первичным обмоткам 25, 25 трансформаторов начинает протекать ток. Напряжение, наводимое на их вторичных обмотках, через (и-1)-входовые логические элементы ИЛИ 201, 20, включает ключевые элементы 13, 13> и насыщенные транзисторы 1>, 1л форсированно закрываются по коллекторному переходу. Процесс запирания длится до тех пор, пока все транзисторы не войдут в режим отсечки. из которых включен токоограничивающий элемент, состоящий в том, что на их эмиттерный переход подают импульсы управления соответствующей полярности для включе5 ния и выключения транзисторов, о т л и ч аю шийся тем, что, с целью повышения надежности путем динамического выравнивания токов параллельно включенных биполярных транзисторов при их включении и

10 выключении, определяют знак разности потенциалов между точками соединения выводов указанных транзисторов с их токоограничивающим элементом и в соответствии со знаком полученной разности

15 потенциалов подают запирающий сигнал на коллекторный переход опережающего транзистора при включении транзисторов и отстающего при их выключении.