Устройство слежения за дорожкой дискового носителя информации

Иллюстрации

Показать всеРеферат

Изобретение относится к технике слежения за информационной дорожкой носителя оптической записи на дисковых запоминающих устройствах. С целью повышения точности автоматического слежения за информационной дорожкой в устройстве обеспечена синхронизация моментов переключения считывающего луча относительно основной линии информационной дорожки. Устройство содержит последовательно установленные на оптической оси источник излучения 1, светоделитель 2, качающееся зеркало с приводом 3, объектив 4, составляющие оптическую головку 5, дисковый носитель информации 6, а также фотоэлектрический преобразователь 7, оптически связанный со светоделителем и подключенный к входу дельтамодулятора 9, блок реверсирования 12, анализатор приращений 10, блок местного управления 8, блок управления 11, первый и второй демодуляторы 14, 15. 13 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51)5 G 11 В 7/09

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

flO ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМ

ПРИ ГКНТ СССР (21) 4277146/24-10 (22) 06.07.37 (46) 15.!2.90. Бюл. !! - 46 (72) О.Ф.Буэин, П.П.Иакарычев и А.С.Бычков (53) 634.852 (083.3) (56) Патент ФРГ i!i- 2541520, кл. G 11 В 7/03, опублик. 08 04.76.

Авторское свидетельство СССР

1! - 1278951, кл. С 11 В 7/03, 22.03,86. (54) УСТРОЙСТВО СЛЕЖЕНИЯ 3А ДОРОЖКОЙ

ДИСКОВОГО ИОСИТЕЛЯ И1!СОР!!АЦИИ (57) Изобретение относится к технике слежения эа информационной дорожкой носителя оптической записи на дисковых запоминающих устройствах ° С целью повышения точности автоматического слежения эа информационной до„; SU„„1614031 рожкой в устройстве обеспечена синхронизация моментов переключения счи- тывающего луча относительно основной линии информационной дорожки. Устройство содержит последовательно установленные на оптической оси источник

1 излучения, светоделитель 2,качающееся зеркало с приводом 3,. объектив

4, составляющие оптическую головку

5, дисковый носитель 6 информации, а также фотоэлектрический преобразователь 7, оптически связанный со светоделителем и подключенный к входу дельта †модулято 9, блок 12 реверсирования, анализатор 10 приращений, блок 8 местного управления, блок 11. управления, первый 14 и второй 15 демодуляторы. 13 ил.

1614031

Изобретение относится к приборостроению и может .найти применение в оптических дисковых запоминающих устройствах.

Цель изобретения — повышение точности слежения за информационной дорожкой.

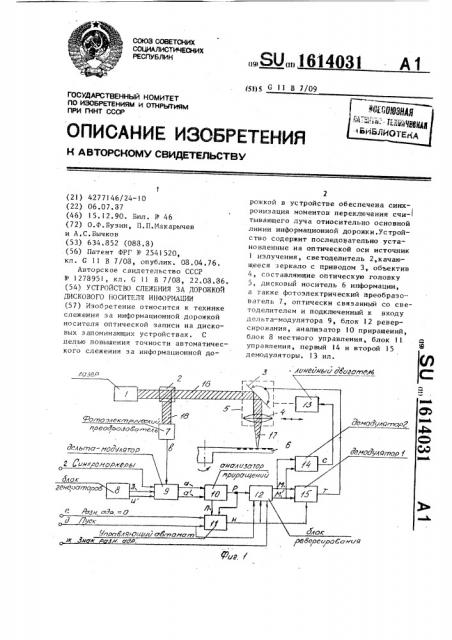

На Фиг.1 приведена структурная схема устройства слежения за информа- 10 циоиной дорожкой Дискового носителя информации; на Фиг.2 — функциональная схема дельта-модулятора огибаюЩей сигнала воспроизведения; .на фиг.3 — Функциональная схема акали- 15 затора приращений огибающей сигнала воспроизведения; на Фиг.4 — функциональная схема блока управления; на Фиг.5 — Функциональная схема блока реверсирования; на фиг, 6-7 20 функциональные схемы первого и второго демодуляторов соответственно; на фиг, 8 — 13 — рисунки и временные диаграммы, поясняющие принцип работы устройства для слежения за дорожкой 25 дискового носителя информации.

Устройство для слежения за дорожкой дискового носителя информации (фиг.1) содержит лазер 1, светоделитель 2, качающееся зеркало 3 с приводом и объектив 4, составляющие оптическую головку 5, дисковый носитель 6 информации, фотоэлектрический преобразователь 7, блок 8 местного управления, дельта-модулятор 9 оги35 бающей нижнего уровня сигнала воспроизведения, анализатор 10 приращений огибающей нижнего уровня сигнала воспроизведения, управляющий автомат

11, блок 12 реверсирования сигнала 40 управления, линейный двигатель перемещения оптической головки 13,первый демодулятор 14 сигнала управления, второй демодулятор 15 сигнала управления. Оптический луч 16 проходит светоделительный элемент 2 и направляется зеркалом 3 и объективом 4 на поверхность дискового носителя 6 информациии. Сфокусиров анный оптиче ский луч 17, отразившись от поверхности дискового носителя 6 информации, вновь падает на светоделительный элемент 2, который делит его на два луча, Луч

18, отраженный гранью светоделительного элемента 2, направляется на фо55 тоэлектрический преобразователь 7.

Информация на оптическом носител.е записывается блоками в промежутках между синхромаркерами.

Схема выделения синхромаркеров запоминающего устройства после амплитудной и временной селекции сигналов воспроизведения Формирует по заднему фронту выделенных синхромаркеров последовательность импульсов "Синхромаркеры", которая поступает в устройство слежения за дорожкой по входу

"г"..Кроме того, для работы устройства слежения необходимы внешние сигналы "Пуск" (из устройства управления оптического дискового запоминающего устройства ОДЗУ), "Знак разности адресов" и "Разность адресов = 0" (из блока дискретного позиционирования ОДЗУ), поступающие по входам

"д"у ",ж" и "е11 соответственно. чункциональная схема дельта-модулятора 9 огибающей сигнала воспроизведения приведена на фиг.2, Схема содержит амплитудный компаратор 19, D-триггер 20, десять формирователей

21,22,24,25,31,32,34,35,36,42, семь элементов И 23,27,28,33,37,39,40, два RS-триггера 26,38, семиразрядный двоичный реверсивный счетчик 29, цифроаналоговый преобразователь 30 и элемент ИЛИ 41 .

На первый вход амплитудного компаратора 19 поступает аппроксимирую— щее напряжение "б", на второй вход— сигнал воспроизведения "в" (фиг.2) °

На входы "a" и "и" поступают соответственно последовательности импульсов с первого и второго выходов блока 8 местного управления. На вход

"г" поступает последовательность

"Синхромаркеры" из блока выделения синхромаркеров ОДЗУ. Прямой "а" и инверсный "в" выходы дельта-модулятора подключены соответственно к прямому и инверсному входам анализатора 10 приращений

В соответствии с функциональной схемой (Фиг,2) дельта-модулятор 9 работает следующим образом.

RS-триггер 38 задает режим синхронизации работы дельта-модулятора

9 от синхросерии СИ2, поступающей из блока 8 местного управления ло входу "и" (триггер 38 сброшен в нулевое состояние), или от синхромаркеров, выделяемых блоком селекции синхромаркеров запоминающего устройства и поступающих на вход "r". Если величина огибающей нижнего уровня синхромаркеров при слежении за дорожкой уменьшается, то старший разряд счет!

6! чйка 29 становится равным О. RS-триг-

rep при этом переходит в единичное состояние и последовательность сигналов "Синхромаркеры" через схему

39 совпадения поступает на вход элемента ИЛИ 41, Переход в режим синхронизации от синхросерии СИ2 осуществляется по сигналу "1 " со старшего разряда счетчика 29, В режиме синхронизации от синхромаркеров уменьшается величина временной задержки, вносимой дельта-модулятором 9 в контур слежения эа дорожкой. Следовательно, увеличивается точность слежения за дорожкой.

В любом режиме синхронизации дельта-модулятора 9 на выходе элемента ИЛИ 41 формируется последовательность импульсов, частота следования которых равна 96 кГц, Элементы 21,31,23,24,25 и элементы 42,32,33,34,35 служат для разнесения по времени сигналов,.поступающих с выхода амплитудного компаратора 19 и элемента ИЛИ 41, На прямой вход запуска формирователя 31 и инверсный вход запуска формирователя

32 поступает последовательность уп-. равляющих импульсов СИ1 с выхода

"3" блока 8 местного управления.Частота следования импульсов К вЂ” 1 ЯГц, скважность равна двум. На выходах формирователей 31, 32 формируются последовательности импульсов длительностью 200 нс, сдвинутых один относительно другого по времени на . величину 1/2 ig (фиг,Я), С выхода фотоэлектрического преобразователя на вход 2 амплитудного компаратора 19 дельта-модулятора 9 подается сигнал воспроизведения "в" на вход 1 — аппроксимирующее напряжение с выхода UAfl 30. Если амплитуда сигнала воспроизведения станет меньше величины аппрокск»ирующего напряжения, то на выходе компаратора19 появится единичный уровень, который установит D-триггер 20 в единичное состояние. Формирователь 21 формирует импульс длительностью

1,4 мкс, по заднему фронту которого формирователь 22 формирует импульс сброса триггера 20 в исходное нулевое состояние. На выходе схемы совпадения И 23 формируется один либо два импульса, проходящих с выхода элемента 31 (фиг. Ba,б соответственно).

По переднему фронту первого иэ них

4031

ЦАП 30 увеличивается.

40 Функциональная схема анализатора

10 приращений приведена на фиг.З.Схема содержит три схемы ИЛИ 43,49,50, элемент 44 задержки, два формирователя 45,52, две схемы И 47,48,шестнадцатиразрядный сдвигающий регистр

46, семиразрядный двцичнь»й реверсивный счетчик 51 и инвертор 53,Первые входы схем ИЛИ 43, 49 и вход сдвига вправо DR сдвигающего регистра 46 соединены с прямым выходом "а" дельта-модулятора 9. Вторые входы схем

ИЛИ 43, 50 соединены с инверсным вы.ходом "а" дельта-модулятора 9.Выход знакового разряда реверсивного счетчика 51 и инвертора 53 соединены соответственно с управляющими входами

"п" и "р" управляющего автомата II.

В соответствии с функциональной схемой анализатор IO приращений оги5

t5

20 формирователь 24 формирует импульс длительностью 1,4 мкс. Пришедший эа это время второй.импульс с выхода схемы совпадения И 23 не оказывает чвлияния на работу схемы, „ Сигнал с элемента 24 запускает формирователь

25, на выходе которого формируется импульс длительностью 200 нс,который устанавливает в единичное состояние

RS-триггер 26. Спустя 500 нс (так как импульсы с элементов 31, 32, а следовательно, и с элементов 25, 35 разнесены по времени на 500 нс) содержимое RS-триггера 26 считывается импульсом с элемента 35, н с выхода схемы совпадения И 27 единичный сигнал поступает на вычитающий вход счетчика 29 и инверсный выход "а" дельта-модулятора 9. При этом амплнтуда аппроксимирующего напряжения на выходе ЦАП 30 уменьшается..

Если амплитуда сигнала воспроиэО ведения больше величины аппроксимирующего напряжения, то на выходе амплитудного компаратора 19 уровень логической единицы не возникает. Dтриггер 20 остается в нулевом состоянии, на выходах элементов 21 23, 24,25 уровни логической единицы не формируются. RS-триггер 26 остается в нулевом состоянии и, следовательно, единичный импульс с выхода одновибратора 13 через схему 15 совпадения поступает на суммирующий выход счетчика 29 и прямой выход "а" дельтамодулятора 9. При этом амплитуда аппроксимирующего напряжения на выходе

1614031 бающей сигнала воспроизведения работает следующим образом.

Ка суммирующий и вычитающий входы реверсивного счетчика 51 через эле5. менты ИЛИ 49, 50 и на входы схемы

ИЛИ 43 поступают последовательности импульсов "а", "а " (фиг.9) несущие информацию о приращениях огибающей нижнего уровня сигнала воспроизведения. Ка вход элемента 44 задержки поступает последовательность импульсов 43 частотой 96 кГц и длитель— ностью 200 нс. Время задержки

A элемента 44 составляет 100 нс.Таким образом, на .вход последовательного занесения и сдвига С сдвигающего регистра 46 импульсы поступают с задержкой 100 нс. Формирователь 45 по заднему фронту импульсов 44 формирует сигнал 45 занесения, по которому к содержимому счетчика 51 добавляет-. ся единица, если значение старшего разряда Q15 сдвигающего регистра 46 равно нулю, и вычитается единица,если значение Q15 равно единице.

Если с прямого выхода "а" дельтамодулятора 9 на вход OR регистра 46 и первый вход схемы ИЛИ 49 поступает импульс, соответствующий положитель- 30 ному приращению огибающей нижнего уровня сигнала воспроизведения, то содержимое счетчика 51 увеличится на единицу и спустя время задержки элемента 44 содержимое регистра 46 будет 35 сдвинуто на один .разряд вправо,причем в младший разряд (P регистра 46 по входу Пк запишется единица.

Если в текущий момент времени приращение огибающей нижнего уровня 40 сигнала воспроизведения отрицательно, то по входу "а " с дельта-модулятои I!1 ра 9 поступает единичный импульс, уменьшающий на единицу содержимое счетчика 51. Спустя с происходит 45 сдвиг вправо содержимого регистра 46, причем в младший разряд регистра

Q0 заносится нуль.

В обоих случаях содержимое счетчика 51 сигналом с формирователя 45 через элементы 47,49 или 48,50 увеличится или уменьшится на единицу в зависимости от значения старшего разряда Я15 регистра 46.

Таким образом, информация о приращениях огибающей нижнего уровня сигнала воспроизведения,поступающая с прямого "а" и инверсного "а " выходов дельта-модулятора 9, задерживается с помощью сдвигающего регист.ра 46 на 16 тактов и вычитается из содержимого счетчика 51, который содержит ту же информацию, полученную без задержки. Следовательно, по содержимому счетчика 51 можно судить о величине и знаке первой разности от огибающей нижнего уровня сигнала воспроизведения. Исходное состояние регистра 46 и счетчика 51 задается импульсом с формирователя 52 при включении питания. В исходном состоянии содержимое четных разрядов регистра 46 равно единице, нечетных— нулю. Счетчик 51 по входу R сбрасывается в нулевое. состояние.

Функциональная схема блока !1 управления приведена на фиг ° 4. Схема содержит три схемы И, 54,58,62, три схемы ИЛИ 55,59.,63, три элемента 56,60,64 задержки и три D-тригге— ра 57,6!,65. Входы "и", "р" блока

11 управления соединены соответственно с выходами "п", "р" анализатора 10 приращений. На входы "е" и "д" подаются соответственно внешние сигналы "Разность адресов = 0" из блока дискретного позиционирования запоминающего устройства и сигнал

"Пуск" из устройства управления накопителем.

Качало работы блока 1! управления .осуществляется по сигналу "Пуск" °

Этим сигналом D-триггеры 57, 61, 65 через элементы ИЛИ 55, 59, 63 и элементы 56, 60, 64 задержки (, . 40 нс) по входу R устанавливаются в нулевое состояние. При этом единичный уровень с инверсного выхода триггера 65 разрешает прохождение сигналов, постулающих по входам "е", "р", "п", на входы "с" всех D-триггеров. Однако нулевыми уровнями с прямых выходов 0-триггеров 57 и 61 прохождение сигналов с входов "п", "р" на входы С триггеров 61, 65 блокировано. Таким образом, появление сигналов на входах "р", "п" не приводит к изменению состояния схемы.

С приходом сигнала по входу "е" Этриггер 57 устанавливается в единичное состояние. При этом разрешается занесение сигнала, появляющегося на входе "и", на триггер 61 и на триггеры 61, 65 через элементы ИЛИ 59, 63 и элементы 60,64 задержки проходит импульс сброса. Если после сигнала, пришедшего по входу "е", появляется.

1614031

10 сигнал на входе "и", то D-триггер

61 устанавливается в единичное сос" тояние и разрешает занесение снгнала по входу "р" на триггер 65. Затем триггеры 57, 65 устанавливаются в

ll ll

0 ° Если после этого появляется с игн ал н а входе " р ", то D- триггер 6 5 устанавливается в единичное состояни е и н а выходе "н " управляющего автомата 1 1 появляется высокий уровень напряжения .

Таким о б р аз ам, высокий ур а в епь на выходе "н" блока 11 управления появляется лишь при последовательном

1О

55 поступлении сигналов по входам "е", l1 ll l ° l1

j °

Функциональная схема блока 2 реверсирования приведена на фиг ° 5.Схема содержит Т-триггер 67 и три схе- 20 мы И 66, 63, 69. Первые входы элементов И 66, 68, 69 объединены и соединены с выходом "н" управляющего автомата ll ° Второй вход схемы И 66 соединен с выходом "к" анализатора

10 приращений огибающей нижнего уровня сигнала воспроизведения. Выходы схем И 63, 69 соединены соответственно с входами "и", м демодуляторов

15 и 14. Установочные входы К и

ST-триггера 67 соединены соответст-. венно с внешними шинами "д" (" Пуск" ) и "ж" (" Знак разности адресов") и являются входами начальной установки блока 12 реверсирования.

В соответствии с функциональной схемой блок !2 реверсирования работает следующим образом.

По сигналу "Пуск" (единичный импульс, поступающий по входу "д" из . 40 устройства управления накопителем)

Т-триггер 67 по входу R сбрасывается в нулевое состояние. После этого в зависимости от знака разности адресов требуемой и текущей дорожек 45

Т-триггер о7 принимает исходное состояние ° Если разность адресов 4 О, то Т триггер 67 по входу S устанав-. ливается в единичное состояние импульсом, поступающим из блока дискретного позиционирования по входу

"д" блока 12 реверсирования. При наличии высокого уровня на входе "и" блока 12 реверсирования на выходе элемента И 68 формируется низкий уровень, на выходе элемента И о9— высокий. Если разность адресов О, единичный импульс на входе "ж" не формируется и Т-триггер 67 остается в нулевом состоянии. При этом высокий уровень формируется на вы" ходе элемента И 68, а низкий — на выходе элемента И 69. При наличии на входе н" низкого уровня напряжения прохождение сигнала реверса по входу "к" через элемент И 66 блокировано. Т-триггер 67 остается в исходном состоянии, на выходах элементов И 68, 69 формируется сигнал логической единицы. Наличие на входе

"н" высокого уровня напряжения разрешает прохождение сигнала реверса с выхода "к" анализатора 10 приращений через элемент И 66 на вход Ттриггера 67. При этом Т-триггер 67 изменя ет свое состояние на противоложное, что приводит к смене на противоположные уровней сигналов на выходах элементов И 68, 69..

Функциональная схема первого демодулятора 14 сигнала управления приведена на фиг.б. Схема содержит интегратор с цепью 71 задания начальных условий, два формирователя

74,75, два трансформатора ?О, 72 уровней и аналоговый сумматор 73.

Входы формирователей 74, 75 и трансформатора 70 уровней соедийены соответственно с первым "м" и вторым

"м " выходами блока !2 реверсирова-, ния. Выход аналогового <сумматора 73 через усилитель мощности соединен с электрическим входом привода качающегося зеркала 3. Интегратор 71 трансформаторы 70,72 уровней и аналоговый сумматор 73 выполнены на ос->

1 нове операционных усилителей и дискретных элементов С l, Р— Р1 7, В соответствии с функциональной схемой демодулятор 14 работает следующим образом.

При наличии низкого уровня сигнала на входе "н" (" Начальная установка") замыкается верхняя контактная группа ключа К. При этом осуществляется ввод нулевых начальных условий в интегратор 71. С выходов "м", "м " блока 12 реверсирования на входы трансформатора 70 уровней и формирователей 74, 75 поступают логические уровни напряжения, соответствующие состоянию блока 12 реверсирования.

Трансформаторы уровней преобразуют уровни логической "1" и логического

"0" в положительные и отрицательные перепады напряжения, которые поступа3 ют с выхода трансформатора 70 уров16!4031

12 ней на вход интегратора 71 и один иэ входов аналогового сумматора 73 и с выхода трансформатора 72 уровней

) на второй вход аналогового сумматора

73. Интегральная составляющая сигнала управления формируется ga выходе интегратора 71 и подается на третий вход аналогового сумматора 73. Формирователи 74, 75, трансформаторы !О

70, .72 уровней и аналоговый сумматор

73 введены в демодулятор 14 для осуществления коррекции сигнала управления положением качающегося зеркала 3 и обеспечения устойчивой работы !5 всего устройства в целом, Схема 70 формирует сигнал, соответствующий пропорциональной составляющей сигнала управления, а схема 72 - дифференциальной составляющей сигнала управ- 20 ления. ,Временные диаграммы, поясняющие работу демодулятора 14 сигнала в установившемся режиме, приведены на фиг.10..

Функциональная схема второго демодулятора 15 сигнала управления приведена на фиг.7; Схема содержит два формирователя 79, 80, два трансформатора 76; 78 уровней и аналоговый 30 сумматор. 77. Входы формирователей

79, 80 и трансформатора 76 уровней соединены соответственно с первым

"м" и вторый ."м " выходами блока 12 реверсирований. Выход аналогового сум- 5 матора 77 через фильтр нижних частот и усилитель мощности соединен с электрическим входом линейного двигателя 13, Работа функциональных элементов демодулятора 15 аналогична 40 работе соответствующих элементов демодулятора 14.

Устройство для слежения за дорожкой дискового носителя информации работает следующим образом. 45

Работа осуществляется под управлением управляющего автомата 1 i.,В исходном состоянии (в фазе дискретного позиционирования) на выходе

"н" управляющего автомата 11 присут 50 ствует низкий логический уровень. При этом интегратор 70 первого демодулятора 14 принимает нулевое начальное значение, на первом "м" и втором

"и " выходах блока 12 реверсирования формируются единичные уровни.

Таким об р аз ом, выходное на пряж ение трансформаторов 69, 7! уровней первого демодулятора 15 и трансформаторов 75, 77 уровней второго демодулятора 15 разно нулю, а следовательно, сигнал на выходах демодуляторов 14 и 15 также равен нулю. Таким образом, слежение за дорожкой начинаетоя из "среднего" положения исполнительных механизмов 3 и 13.

По сигналу "Пуск" Т-триггер 67 блока 12 реверсирования обнуляется.Далее в зависимости от знака разности текущего и заданного адресов дорожек

Т-триггер 67 блока 1 2 реверсирования устанавливается в единичное состояние (разность адресов (.!) импульсом, поступающим по входу "ж" из блока дискретного позиционирования, либо остается в нулевом состоянии (при разности адресов )О единичный импульс на входе "ж" не формируется), При попадании считывающего луча !

7 на,информационную дорожку на выходе фотоэлектрического преобразователя.7 возникает сигнал воспроизведения "в". Верхний уровень сигнала воспроизведения "в" определяется коэффициентом отражения носителя информации К! и не зависит от положения считывающего луча 17 относительно инфОрмационной дорожки. Нижний уровень "в " сигнала воспроизведения "в" определяется как коэффициентом отражения подложки К2, так и величиной отклонения считывающего луча

l7 от центральной линии информационной дорожки.

Дельта-модулятор 9 отслеживает огибающую нижнего уровня "в™ сигнала воспроизведения "в" и формирует на прямом "а" и инверсном "a " выходах последовательности логических нулей и единиц в соответствии с ее изменениями ° Вид огибающей нижнего уровня сигнала воспроизведения при пересечении лучом !7 информационных дорожек в процессе дискретного позиционирования показан на фиг,ll.

E моменты времени t, t ..., луч

17 находится на середине информационной дорожки, нижний уровень сигнала воспроизведения минимален, знак первой разности от огибающей меняется с "-" на "+" ° В моменты времени луч 17 находится между дорожками, нижний уровень сигнала воспроизведения максимален, знак первой разности от огибающей меняется с "+" на -". Таким образом, при движении считывающего луча 17 по направлению

1614031

14 к центральной линии информационной дорожки приращения огибающей нижнего уровня сигнала воспроизведения отрицательны, при движении луча 17 от центральной линии информационной дорожки — положительны. Анапизатор

19 приращений осуществляет вычисление первой разности от огибающей нижнего уровня сигнала воспроизведения в каждый текущий момент времени. Если!

О производная )О, то на выходе "н" анализатора 10 приращений формируется уровень логического нуля, на выходе "р" — единицы, если первая разность (О, то наоборот. При смене знака первой разности с "+" на (моменты времени tgy ty) положительный перепад напряжения формируется на выходе "п" анализатора 10 приращений, В момент времени г. (фиг,)I) разность адресов текущей и требуемой дорожек станет равной О. При этом

20 поминающего устройства выдает соответствующий сигнал на вход "е" блока

1) управления. В моменты времени t и t на входах "и" и "р" соответ7 стненно формируются уровни логической "1" и, следовательно, на выходе

"н" блока 11 управления также формируется единичный уровень. При этом

30 снимается блокировка со схем И 68, 69 блока 12 реверсирования и интегратор

71 демодулятора !5 переводится в режим интегрирования. Таким образом, цепь обратной связи замыкается и устройство переходит н режим слежения за дорожкой.

С выходов первого и второго демодуляторов 14, 15 на входы зеркала 3 и линейного двигателя )3 подается управляющее напряжение, которое вызывает перемещение луча. !7 в направлении, противоположном направлению остаточного перемещения луча блоком дискретного позиционирования.Начальное направление перемещения считывающего луча 17 задается путем уста нонки триггера 67 блока 12 реверсирования в нулевое или единичное состояние в зависимости от знака разности адресов текущей и требуемой до-. рожки сигналом, поступающим из блока дискретного позиционирования в блок

12 реверсирования по входу "ж"..Однако иэ-эа инерционности исполнительных механизмов перемещения считываюблок дискретного позиционирования за- 25 щего луча 17 изменение направления его движения на противоположное происходит спустя некоторый промежуток времени и (фиг. I I, момент времени сВ), после чего приращения огибающей нижнего уровня сигнала воспроизведения станут отрицательными и знак первой разности сменится с "+" на

11 I t

В момент времени t луч 17 вновь пересечет осевую линию информационной дорожки. Знак первой разности от огибающей нижнего уровня сигнала воспроизведения изменится с "-" на

"+". На выходе "р" анализатора 10 приращений появится положительный перепад напряжения, который переведет триггер 67 блока 12 реверсирования в противоположное состояние. Изменение на противоположное состояние триггера 67 вызывает смену полярности сигналов на выходах трасформато,ров 70, 76 уровней демодуляторов

I4, )5 и приводит к изменению направления движения считывающего луча 17 относительно осевой линии информационной дорожки (фиг.!1, момент времени t ). Дальнейшая работа устройства происходит аналогично. B момент времени.t! луч 17 вновь пересечет информационную дорожку..При этом знак первой разности от огибаю.пей нижнего уровня сигнала воспроизведения вновь изменится с "-" на +", Т-триггер 67 блока 12 реверсирования перейдет в первоначальное состояние и восстановит энак приращения выходного напряжения демодулятора 15.Ñïóñтя время Д t t „- t считывающий луч 17 также примет первоначальное направление движения. Далее изменения направления движения считывающе-. го луча будут происходить в моменты времени t )<, t.<,... По завершении переходного процесса в устройстве устанавливаются периодические колебания считывакицего.луча 17 относительно основной линии информационной дорожки.

Управляющий сигнал на вход линейного двигателя 13 подается с демодулятора )5, Форма сигналов на выходе

"с" демодулятора 15 показана на фиг.12, На интервале А колебания считывающего луча 17 смещены относительно центральной линии дорожки вправо, на интервале Б — симметричны, на интервале В - смещены в противо16

l5

1614ОЗ1 положном направлении. Постоянная составляющая сигнала демодулятора 14 на интервале А имеет положительный знак, ее величина пропорциональная смеще5 нию. На интервале Б - постоянная составляющая равна нулю, на интервале

В она имеет отрицательный знак, ее величина пропорциональна смещению.

Под воздействием сигнала демодулятора 1п

15 линейный двигат ель оказывает дополнительное согласованное с зеркалом 3 воздействием на положение считывающего луча.

Формула изоб ретения устройство слежения эа дорожкой дискового носителя информации,содержащее последовательно. установленные на оптической оси источник излучения, светоделитель, качающееся зеркало с приводом, объектив, дисковый носитель информации, а также фотоэлектрический преобразователь, опти- 25 чески сопряженный со светоделителем, дельта-модулятор, включающий амплитудный компаратор, реверсивный счетчик и цифроаналоговый преобразователь, анализатор приращений, включаю- ЗО щий реверсивный счетчик и первую схему ИЛ11, блок .реверсирования, состоящий из Т-триггера и двух схем И, первый и второй демодуляторы, связанные соответственно с приводом качающегося зеркала и линейным двигателем перемещения оптической головки, и блок генераторов, о т л и— ч а ю щ е е с я. тем, что, с целью повышения точности слежения за информационной дорожкой, введен блок управления, содержащий первый, второй и третий Э-триггеры, три схемы

И, три схемы ИЛИ и три элемента задержки, первые входы схем ИЛИ соеди- 45 иены с первым входом блока управления, первый вход третьей схемы И и вторые входы второй и третьей схем

ИЛИ соединены с вторым входом блока управления, третьи входы первой схемы И и первой и третьей схем ИЛИ соединены с третьим входом блока управления, второй вход первой схемы ИЛИ и третьи входы второй схемы ИЛИ и второй схемы И.соединены с четвертым

55 входом блока управления, выходы первой, второй и третьей схем И соединены соответственно с входами занесения второго, третьего и первого Dтриггеров, входы сброса которых соединены через соответствующие элементы задержки с выходами первой,второй и третьей схем ИЛИ, выход первого Dтриггера соединен с первым входом первой схемы И, выход второго Э-триггера соединен с первым входом второй схемы И, выход третьего Э-триггера— с выходом блока управления вторыми входами первой, второй и третьей схем И, в анализатор приращений введены сдвигающий регистр, вторая схема ИЛИ, инвертор и формирователь импульсов начальной установки, причем первый вход первой схемы ИЛИ и вход сдвигающего регистра соединены с первым входом анализатора приращений, первый вход второй схемы ИЛИ соединен с вторым входом анализатора приращений, вторые входы схем ИЛИ соединены с выходом сдвигающего регистра, выходы первой и второй схем ИЛИ соединены соответственно с входами инкремента и декремента счетчика, старший разряд которого соединен с первым выходом всего анализатора приращений и с входом инвертора, выход которого соединен с вторым выходом анализатора приращений„ выход формирователя импульсов соединен с входами начальной установки сдвигающего регистра и счетчика, в дельта-модулятор введены два RS-триггера, коммутатор, пять схем И и семь формирователей импульсов, первый вход первой схемы И и первый информационный вход .коммутатора соединены с первым управляющим входом дельта-модулятора, второй информационный вход коммутатора соединен с вторым управляющим входом дельта-модулятора, входы первого и второго формирователей импульсов соединены с третьим управляюшим входом дельта-модулятора, выход компаратора соединен через третий формирователь импульсов с первым входом второй схемы И, выход которой соединен через четвертый формирователь импульсов с входом установки первого триггера, выход коммутатора соединен через пятый формирователь с первым входом третьей схемы И, выход которой через шестой формирователь импульсов соединен с первыми входами четвертой и пятой схем И,вторые входы которых соединены с выходом первого триггера,,а выходы — с входами инкремента и декремента счетчиIS

17

I 614031 ка, выходы первого и второго формирователей импульсов соединены соотв етств енно с в торыми входами второй и третьей схем И, выход четвертой схемы И соединен через седьмой формирователь импульсов с входом сброса первого триггера, старший разряд счет чика соединен с входом сброса второго триггера и вторым входом первой схемы И, выход которой соединен с входом установки второго триггера, выход которого соединен с управляющим входом коммутатора, в блок pesepсирования введена третья схема И, первые входы первой, второй и третьей схем И соединены с первым управляющим входом блока реверсирования,второй вход первой схемы И и выходы сброса и установки триггера соединены соответственно с информационным, вторым и третьим управляющими входами блока реверсирования, выходы первой схемы

И соединен со счетным входом триггера, прямой и инверсный выходы которого соединены с вторымн входами второй и третьей схем И, выходы которых соеФ дннены с соответствующими информационными выходами блока реверсирования, при этом первый и второй входы блока управления соединены соответственно с входной шиной управления и шиной

-разности адресов, третий и четIp вертый — с первым и вторым выходами анализатора приращений, выход блока управления соеди-! цен с входом ус тановки нулевых начальных условий первого демодуля15 тора и с первым управляющим входом блока реверснрования, первый, второй и третий управляющие входы дельта-модулятора соединены соответственно с входной миной синхромаркеров р0 и выходами блока генераторов, второй и третий управляющие входы блока реверсирования соединены соответственно с входной шиной управления и входной шиной знака разности адресов.

-161403I

f 61403) 7О i

Р11 Я

36 аз

М а) 1614031.1614031 еС =2f2

D 4) о

» »», л

Риг. О

Составитель С.Ботуз

Техред А.Кравчук

Редактор А.Маковская

Корректор И,Муска

Заказ 333

Тираж 347

Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035,. Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул, Гагарина, 101 о я

»

Ь "ч »»

»»» с

Ф I . ф

Н

Q I&

»

» л