Устройство опознавания синхросигналов для аппаратуры цифровой видеозаписи

Иллюстрации

Показать всеРеферат

Изобретение касается цифровой видеозаписи и может быть использовано в аппаратуре передачи дискретной информации. Цель изобретения - увеличение помехоустойчивости опознавания синхросигналов, а также снижение скорости обработки синхросигналов. Устройство содержит регистр 3 сдвига, счетчик 4 импульсов, первый регистр 5, три блока 8, 9, 10 памяти второй 11 и третий 12 регистры. Изобретение позволяет использовать низкоскоростные элементы и уменьшить энергопотребление устройства. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

1614034 А1

s G 11 В 27/10

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 4442942/24-10 (22) 20.06.88 (46) 15.12.90. Бюл. М 46 (71) Всесоюзный научно-исследовательский институт телевидения и радиовещания (72) Л.Е, Цизин и А.Д. Ротенштейн (53) 681.325.61(088.8) (56) Авторское свидетельство СССР

М 1278970, кл. G 11 В 27/10, 1986. (54) УСТРОЙСТВО ОПОЗНАВАНИЯ СИНХРОСИГНАЛОВ ДЛЯ АППАРАТУРЪ| ЦИФРОВОЙ ВИДЕОЗАПИСИ (57) Изобретение касается цифровой видеозаписи и может быть использовано в аппаратуре передачи дискретной информации.

Цель изобретения — увеличене помехоустойчивости опознавания синхросигналов, а также снижение скорости обработки синхросигналов. Устройство содержит регистр 3 сдвига, счетчик 4 импульсов, первый регистр 5, три блока 8, 9, 10 памяти, второй 11 и третий 12 регистры. Изобретение позволяет использовать низкоскоростные элементы и уменьшить энергопотребление устройства, 2 ил.

1614034

Изобретение касается цифровой видеозаписи и может быть использовано в аппаратуре передачи дискретной информации, Цель изобретения — увеличение помехоустойчивости опознавания синхросигналов, а также снижение скорости обработки синхросигналов, позволяющее использовать низкоскоростные элементы и уменьшить энергопотребление устройства.

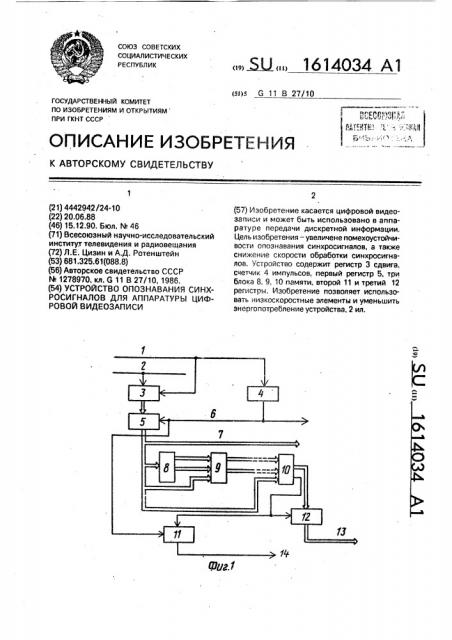

На фиг. 1 изображена структурная схема предлагаемого устройства; на фиг. 2— диаграммы сигналов, поясняющие работу устройства, Устройство содержит шину 1 тактовой синхронизации, информационную шину 2. регистр 3 сдвига, счетчик 4 импульсов, первый регистр 5, сигнал 6 тактовой частоты, выходную шину 7 данных, первый блок 8 памяти, второй блок 9 памяти, К-й блок 10 ланити, второй регистр 11, третий регистр "»2, выходную шину 13 кода распараллеливания и выходкой сигнал 14 синхронизации, Регистр 3 сдвига подключен своим входом к информационной шине 2, а синхронизирующим входом — к шине 1 тактовой синхронизации, подключенной к входу счетчика 4 импульсов, соединенного своим выходом с выходом сигнала 6 тактовой частоты, подключенным к синхрониэирующему входу второго регистра 11 и к синхронизирующему входу первого регистра 5, подключенного своими входами к выходам регистра 3 сдвига, а своими выходами — к выходной шине 7 данных, к входам первого блока 8 памяти, к первым входам всех, кроме первого, блоков памяти, причем второй блок 9 памяти соединен своими вторыми входами с первыми выходами первого блока 8 памяти, третьими входами — с вторыми выходами первого блока 8 памяти, первыми входами — с вторыми входами третьего блока памяти, вторыми выходами — с третьими входами третьего блока памяти. ко орый соединен своими первыми и вторыми выходами соответственно со вторыми и третьими входами следующего по порядковому номеру блока памяти, причем(К-1)-й блок памяти соединен своими вторыми входами с первыми выходами (К-2)-го блока памяти, третьими входами со вторыми выходами (К-2)-го блока памяти, своими первыми выходами со вторыми входами К-ro блока 10 памяти, вторыми выходами с третьими входами К-го блока 10 памяти, подключенного своими первыми выходами к входам третьего регис р;. 12, соединенного своими выходами с выходной шиной 13 кода распараллеливания, а синхронизирующим входом -- с вторым выходом третьего блока 10 памяти и с входом второго регистра 11, с выхода которого снимается выходной сигнал 14 синхронизации, Устройство работает следующим образом, На регистр 3 сдвига воспроизводимые данные поступают по информационной шине 2, а импульсы воспроизводимой тактовой частоты F — по шине 1 тактовой синхронизации (фиг. 2а). Счетчик 4 импульсов форми10 рует сигнал 6 тактовой частоты fT (фиг. 2б) делением частоты Г» wa и, где n — число символов в словах воспроизводимых данных, который поступает на синхрониэирующие входы первого регистра 5 и второго регистра 11. На перво" регистре 5 осуществляется перетактирование распараллельных входных данных тактовой частотой (фиг. 2в), которые поступают в в ыходную шину 7 данных и на первые входы всех блоков памяти

8, 9 и 10, общее испо которых при обнаружении синхросигналов длиной m символов определяется как k=inr(m+2*n-2)(n), Каждый блок памяти проверяет наличие своего исимвольного сегмента синхросигнала в потоке данных, опредсляет расположение первого символа сегмента в и-битном слове данных (код DSVV распараллеливания) и формирует значение DSVV, При наличии в потоке данных синхроинформации РЯ (фиг. 2г) перat é блок 8 памяти фиксирует первые q символов синхросигнала (где ц < и в связи с произвольностью распараллеливания входных данных) и на своих первых выходах устанавливает код РЯМ распараллеливания, который определяется значением и-q и поступает на вторые входы второго блока 9 памяти, на третьи входы которого со вторых выходов первого блока 8 памяти приходит сигнал "Rer" наличия и количества ошибок, используемый для обнаружения синхросигнала, символы которого поражены ошибками. На следующий такт сигнала 6 тактовой частоты второй блок 9 памяти анализирует п-символьный сегмент синхросигнала, начинающийся с q+1 символа, и производит необходимую коррекцию DSW, значение которого устанавливается на первых выходах блока 9 памяти и поступает на вторые входы следующего блока памяти, на третьи входы которого со вторых выходов второго блока 9 памяти приходит сигнал "Rer" ошибки, в результате чего 1-й блок памяти /1 >! > К/ определяет наличие се мента синхросигнала, начинающегося с (l-2) n+q+1 символа синхронизации, причем на его вторые входы.поступает код DSUV с первых выходов предыдущего блока памяти, а на его третьи входы — сигнал "Rer" ошибки со вторых выходов предыдущего блока памяти, с его первых и вторых:выходов на вторые и третьи

1614034

Формула изобретения 25

Jsw

Фие 2

Составитель С;ботуз

Техред М.Моргентал Корректор О. Кравцова

Редактор А.Ревин

Заказ 3894 Тираж 480 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский кол;бинат "Патент", r. Ужгород, ул.Гагарина, 101 входы следующего блока памяти соответственно поступают код DSNI и сигнал Rer ошибки. К-й блок 10 памяти проверяет наличие в потоке данных оставшихся символов синхросигнала, начинающихся с (К вЂ” 2)* п+ц+1 5 символа. При обнаружении синхросигнала, число ошибок в котором определяется сигналом "Rer" ошибки и не превышаетзаданного значения, на первых выходах блока 10 памяти устанавливается необходимый для 10 синхронизации данных код DSW, который поступает на входы третьего регистра 12 и по команде, приходящей со ьгорого выхода

К-го блока 10 памяти на синхронизирующий . вход этого регистра, код DSW переписыва- 15 ется во выходную шину 13 кода распараллеливания (фиг. 2д). Та же команда со второго выхода К-го 5лока 10 памяти поступает на вход второго регистра 11, на синхронизирующий вход которого приходит сигнал 6 так- 20 товой частоты, в результате чего с выхода регистра 11 снимается выходной сигнал 14 синхронизации (hSW) (фиг. 2е). устройство опознавания синхросигналов для аппаратуры цифровой видеозаписи, содержащее регистр сдвига, подключенный своим входом к информационной шине, 30 синхронизирующим входом — к шине тактовой синхронизации, подключенной к входу счетчика импульсов, о т л и ч а ю щ е е с я тем что, с целью увеличения помехоустойчивости опознавания синхросигналов и снижения скорости обработки синхросигналов, в него введены К блоков памяти, второй и третий регистры, причем выход счетчика импульсов соединен с третьим выходом опознавателя синхросигналов и тактовыми входами первого и второго регистрсв, входы первого регистра подключены к выходам регистра сдвига, а выходы первого регистра — к выходной шине данных и к первым входам К блоков памяти, причем -й (iE/1:К) блок памяти соединен своими вторыми входами с первыми выходами (i — 1)го блока памяти, третьими входами — с вторыми выходами (i — 1)-ro блока памяти, а выходы i-го блока памяти соединены с вторыми и третьими входами (!+1)-го блока памяти, К-й блок памяти подключен своими первыми выходами к входам третьего регистра, соединенно(о своими выходами с вторым выходом опознавателя синхросиг-. налов, синхронизирующий вход третьего регистра — . вторым выходом К-ro блока памяти и с входом второго регистра. выход которого подключен к первому выходу опознавателя синхросигналов, перзый вход опознавателя синхросигналов соединен с информационным входом регистра сдвига и информационной шиной, тактовые входы регистра сдвига и счетчика импульсов соединены с шиной тактовой синхронизации.