Синхронизатор независимых импульсных последовательностей

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи информации. Цель изобретения - повышение точности определения величины сдвига фаз между частотами импульсных последовательностей записи и считывания. Синхронизатор содержит выделитель 1 тактовых частот, запоминающий блок 2, обнаружитель 3 вида согласования скоростей, г-р 4 импульсов считывания, эл-т НЕ 5, эл-ты ИЛИ 6 и 7, счетчик 8 импульсов, фазовый детектор 9 и эл-ты И 10 и 11. Каждому временному положению импульсной последовательности на выходе счетчика 8 соответствует определенное дискретное значение сдвига фаз. В моменты достижения следующего дискретного значения осуществляется сдвиг счетчика 8 соответственно влево или вправо вслед за перемещением импульсной последовательности фазового детектора 9, чем и обеспечивается соответствующий временной сдвиг для обнаружения следующего значения сдвига фаз. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (я)ю Н 04 1 7/04, Н 04 J 3/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ

ПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМ

ПРИ ГКНТ СССР

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К .АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

g1) 4666532/24-09

2) 23.03.89 . 6) 15.12.90. Бюл. М 46

P2) А.А. Штефан и В.А. Приходько ф3) 621.394.662 (088.8) (56) Авторское свидетельство СССР

ЬЬ 537452, кл. Н 04 1 7/02, 1974. (54) СИНХРОНИЗАТОР НЕЗАВИСИМЫХ

ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ (57) Изобретение относится к электросвязи и может быть использовано в цифровых системах передачи информации. Цель изобретения — повышение точности определения величины сдвига фаз между частотами импульсных последовательностей записи и считывания. Синхронизатор содержит вы,, Ы,, 1614121 А1 делитель 1 тактовых частот, запоминающий блок 2, обнаружитель 3 вида согласования скоростей, г-р 4 импульсов считывания, эл-т

НЕ 5, эл-ты ИЛИ 6 и 7, счетчик 8 импульсов, фаэовыйдетектор9иэл-ты И 10и 11. Каждому временному положению импульсной последовательности на выходе счетчика 8 соответствует определенное дискретное значение сдвига фаз. В моменты достижения следующего дискретного значения осуществляется сдвиг счетчика 8 соответственно влево или вправо вслед за перемещением импульсной последовательности фазового детектора 9. чем и обеспечивается соответствующий временной сдвиг для обнаружения следую-—

I щего значения сдвига фаз. 2 ил.

1614121

40 запрета импульса,в моменты обнаружения 45 сдвига фаз, равных + 2z, в последовательность импульсов генератора 4. Обнаружение дискретных значений фазы осуществляется с помощью фазового детек50

Изобретение относится к технике электросвязи и предназначено для использования в цифровых системах передачи информации, Целью изобретения является повышение точности определения величины сдвига фаз между частотами импульсных последовательностей записи и считывания.

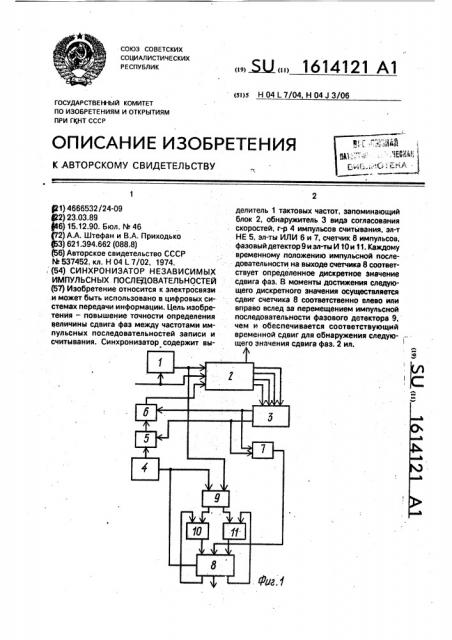

На фиг. I приведена структурная схема синхронизатора независимых импульсных последовательностей; на фиг.2 — временные диаграммы, поясняющие его работу.

Синхронизатор независимых импульсных последовательностей содержит выделитель 1 тактовых частот, запоминающий блок 2, обнаружитель 3 вида согласования скоростей, генератор 4 импульсов считывания, элемент НЕ 5, первый 6 и второй 7 элементы ИЛИ, счетчик 8 импульсов, фазовый детектор 9, первый 10 и второй 11 элементы.

Синхронизатор независимых импульс, ных последовательностей работает следующим образом.

Информационный сигнал, поступаю; щий на вход синхронизатора, записывается . в запоминающий блок 2 с помощью тактовой частоты 1Втч, которая поступает с выхода выделителя 1 тактовой частоты.

Информация считывается из запоминающего блока 2 частотой считывания, формируе, мой в генераторе 4 импульсов считывания через последовательно соединенные элементы НЕ 5 и ИЛИ 6. При этом отношение номинальных значений тактовой частоты

1Втч и тактовой частоты генератора 4 f> рав,,но m/m+K, где К- число служебных позиций цикла;

m — число информационных позиций цикла.

На элементах НЕ 5 и ИЛИ 6 производится торможение или ускорение скорости считывания с помощью обнаружителя 3 вида согласования скоростей путем вставки или тора 9, на входы которого поступают частота

1Втч и частота 12 с второго выхода генератора 4 импульсов считывания, которая выбирается из условия получения необходимой величины дискретного значения

2л где N — число дискретных значений сдвига фаэ.

При этом на выходе фазового детектора 9 формируется последовательность

35 импульсов с частотой биений 4 f = f2 — 1Втч (hf« f2, Л1«ГВтч) и соответственно с периодом, равным - —

1 1 т2 тВтЧ

Изменение временного положения импульса выходного сигнала фазового детектора 9 может происходить только дискретно по фронту импульсов частоты f2 (поскольку

f2 поступает на С-вход триггера, выполняющего роль фазового детектора 9). Таким образом, количество периодов частоты f2 на периоде частоты сигнала фазового детектора 9 определяет максимальное количество дискретных значений фазы ч т2 2

Х т2 РВТЧ и соответственно минимальное значение отслеживаемой фазы ,, 2 л т2 — втч

Временные диаграммы работы фазово-. го детектора 9 приведены на фиг.2а,б,в,г для

N=8. Сигналы с парафазных выходов фазового детектора 9 поступают на соответствующие входы элементов И 10 и 11, на другие входы которых поступают импульсные последовательности с выходов счетчика 8 импульсов, сдвинутые относительно друг друга на период частоты f2 (фиг,2д,е). Коэффициент счета счетчика 8 выбран так,чтобы в исходном состоянии моменты появления импульсов с выхода счетчика 8 совпадали с моментами переключения фазового детектора 9 (фиг. 2г,д„е). В исходное состояние счетчик 8 устанавливается каждым сигналом согласования скоростей через элемент

ИЛИ 7. При этом импульсы с выходов счетчика 8 не проходят на выход элементов И 10 и 11, так как они попадают на нулевые уровни соответствующих парафазных выходов фазового детектора 9 (фиг, 2в,г,д,е). При положительном рассогласовании частот записи и считывания и при достижении величины сдвига фаз от минимального значения, равной 2л /N (фиг. 2к,е), на выходе одного из элементов И 10(11) будет совпадение логической "1" с выхода фазового детектора 9, момент переключения которого сместился на одну позицию вправо по отношению к исходной позиции, с импульсом выходной управляющей последовательности счетчика 8 (фиг. 2и,е,м) и поэтому на выходе элемента И 10 (11) появляется импульс, который уменьшает состояние счетчика на единицу. Этим осуществляется определение первого дискретного значения сдвига фаз. При этом импульсные последовательности с выходов счетчика сдвигаются на один такт частоты 12 вправо, 1614121

1 Х

1 . 2

8 у

5 5 7 и к л

Составитель В.Евдокимова

Техред М.Моргентал Корректор 3.Лончакова

Редактор E.Êîï÷à

Заказ 3898 Тираж 527 Подписное

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР

113035, Москва, Ж-35, Раушская наб., 4/5

Производственно-издательский комбинат "Патент", r. Ужгород, ул.Гагарина, 101 в результате чего восстанавливается исходное соотношение между импульсными последовательностями счетчика 8 и фазового детектора 9 (фиг. 2к,л,м). При достижений последующих значений сдвига фаз происходит последовательный сдвиг счетчика 8 по позициям вправо до момента согласования скоростей, по которому производится установка счетчика 8 в исходное состояние. При отрицательном рассогласовании скоростей импульсная последовательность на выходе фазового детектора 9 перемещается влево, при этом импульсы появляются на выходе второго элемента И 11, вызывая ускорение счета счетчика 8 на единицу и, соответственно, перемещение импульсных последовательностей с выходов счетчика влево до момента согласования скоростей.

Таким образом, каждому временному положению импульсной последовательности на выходе счетчика 8 соответствует определенное дискретное значение сдвига фаз. В моменты достижения следующего дискретного значения осуществляется сдвиг счетчика соответственно влево или вправо вслед за перемещением импульсной последовательности фазового детектора 9, чем и обеспечивается соответствующий временной сдвиг для обнаружения следующего значения сдвига фаз.

Ф о р м ул а. и з о б р ете н и я

Синхронизатор независимых импульсных последовательностей, содержащий последовательно соединенный выделитель тактовой частоты, запоминающий блок и обнаружитель вида согласования скоростей, последовательно соединенные генератор импульсов считывания„элемент НЕ и первый

5 элемент ИЛИ, а также первый и второй элементы И, выходы которых подключены к соответствующим управляющим входам счетчика импульсов, управляющие выходы которого соединены сортветственно с первыми входа-, 10 ми первого и второго элементов И, а выходы обнаружителя вида согласования скоростей соединены соответственно с другими входами элемента НЕ и первого элемента ИЛИ, выход которого соединен с входом считыва15 ния запоминающего блока, информационный вход которого соединен с входом выделителя тактовой частоты, отличающийся тем, что,с целью повышения точности определения величины сдвига фаз между частотами

20 импульсных последовательностей записи и считывания, в него введены фазовый детектор и второй элемент ИЛИ, при этом выходы обнаружителя вида согласования скоростей через второй элемент ИЛИ соединены с ус25 тановочным вхсдом счетчика импульсов, а выход выделителя тактовой частоты и второй выход генератора импульсов считывания соединены с соответствующими входами фазового детектора, выходы кото30 рого соединены соответственно с вторыми входами первого и второго элементов И, причем второй выход генератора импульсов считывания соединен с тактовым входом счетчика имп ;льсов.